基于10-0B066PA030SB-M996F09、RZ/T1主控器件的2.2KW伺服控制系统解决方案

276

276

拍明

拍明

概述

伺服控制系统,或称伺服系统,是用来精确地跟随或复现某个过程的反馈控制系统。伺服控制系统是使物体的速度、位置等输出状态被控量能够跟随输入目标(或者给定值)的任意变化的一种自动控制系统。其基本要求是精确、快速响应和稳定;其发展趋势是小型化、模块化、网络化。

优势

• 优选功率模块 10-0B066PA030SB-M996F09,集成整流、制动、逆变一体化设计,六管模块,600V/30A,可适用于单相 220V 交流输入的 2.2KW 小型化伺服控制系统,方便安装生产,一致性好,可靠性高;

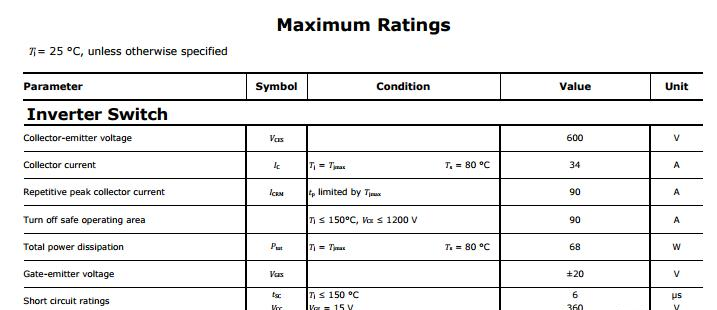

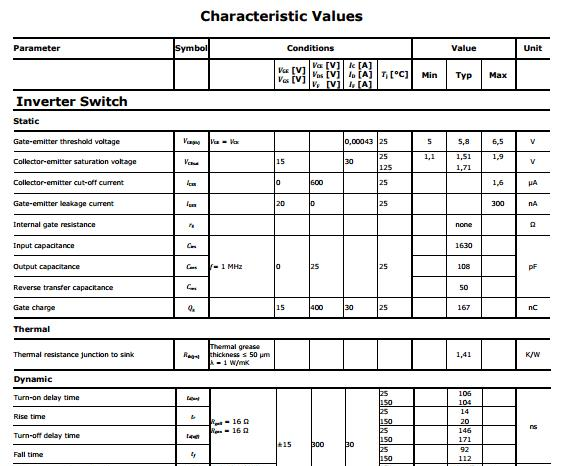

【10-0B066PA030SB-M996F09】

Features

● IGBT3 (600 V) technology

● Open emitter topology

● New ultra-compact housing

● Single-screw heat sink mounting

Target applications

● Dedicated design for motor drive

Types

● 10-0B066PA030SB-M996F09

• 内置以太网MAC、EtherCAT,32位MCU RZ/T1,集算法控制和网络通信于一身;

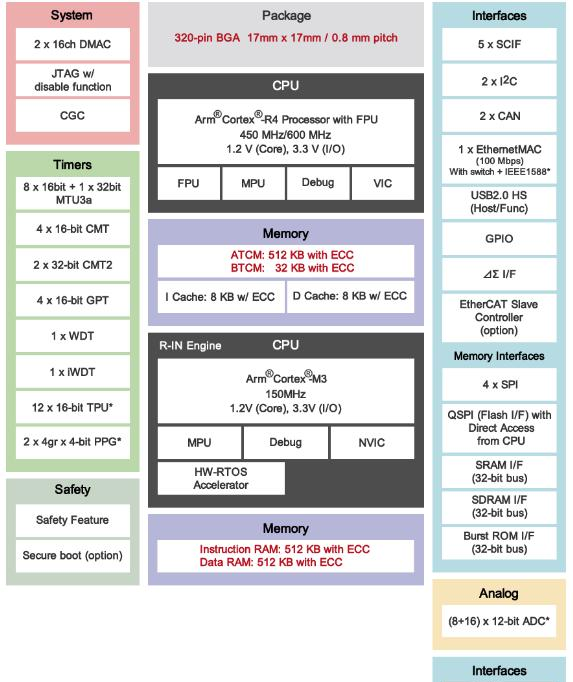

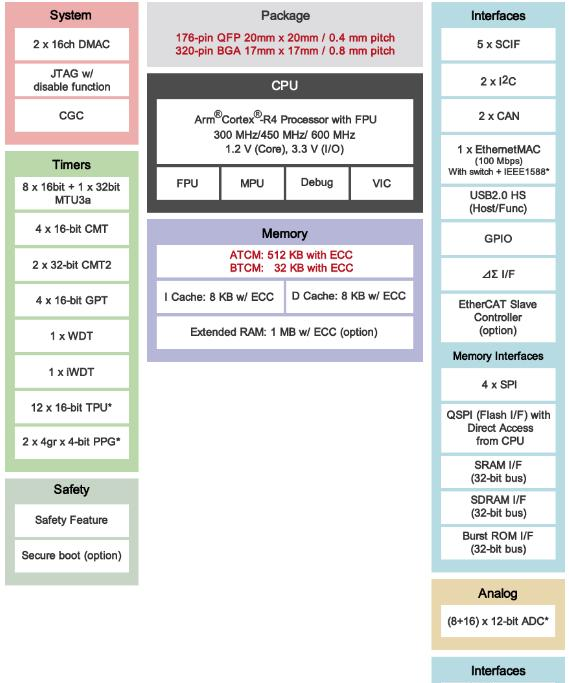

【RZ/T1】

Realize Real-Time Control of Industrial Equipment and Networking at the Same Time

The RZ/T1 Group has the Arm® Cortex®-R4 Processor with FPU core, which was designed for real-time processing, and is capable of high-speed operation at up to 600 MHz. Furthermore, access does not need to be performed via cache memory, and tightly-coupled memory capable of definitive real-time response processing is built-in, enabling high-speed access from the CPU without passing through the cache memory.

RZ/T1 devices that are equipped with a built-in R-IN engine, an accelerator for industrial Ethernet communications, can perform industrial Ethernet processing without loss of real-time performance by Hardware RTOS (HW-RTOS)

RZ/T1 devices that are equipped with a configurable absolute encoder interface are perfectly suited for precision motion control applications. The range of industry standards that are supported by the configurable encoder interface includes EnDat2.2, BiSS®-C, A-format™, Tamagawa and HIPERFACE® DSL.

Key Features : RZ/T1(with R-IN engine)

| ITEM | RZ/T1(with R-IN engine) | |||

|---|---|---|---|---|

| Part NAME | R7S910015 | R7S910016 | R7S910017 | R7S910018 |

| Packages | 320FPBGA | |||

| 0.8mm pitch | ||||

| 17mm x 17mm | ||||

| Main CPU | Arm®Cortex®-R4 Processor with FPU | |||

| Maximum operating frequency | 450MHz | 600MHz | ||

| FPU | Supports single-precision and double-precision addition, subtraction, multiplication, division, multiply-accumulation, and square root calculation | |||

| Tightly-coupled memory | ATCM: 512 KB (with ECC); BTCM: 32 KB (with ECC) | |||

| Cache memory | Instruction cache: 8 KB (with ECC); data cache: 8 KB (with ECC) | |||

| Communication accelerator | R-IN engine multi-protocol communication accelerator | |||

| Expanded internal SRAM | 1 MB (with ECC) *also used for storing protocol stack | |||

| Clocks | External clock/resonator input frequency: 25 MHz | |||

| CPU clock frequency: up to 450/600 MHz | ||||

| Low-speed on-chip oscillator (LOCO): 240 kHz | ||||

| Timers | Up to 33 expanded timer functions | |||

| 16-bit TPUa (12 channels), MTU3a (9 channels), GPTa (4 channels): input capture, output compare, PWM waveform output | ||||

| 16-bit CMT (6 channels), 32-bit CMTW (2 channels) | ||||

| Communications | EtherMAC: 1 port (with switching) | |||

| EtherCAT slave controller | ||||

| USB 2.0 high-speed host/function: 1 channel | ||||

| CAN (ISO 11898-1 compliant): up to 2 channels | ||||

| 16-byte SCIFA with FIFO: 5 channels | ||||

| I2C bus interface: 2 channels of up to 400 kbps transfer speed | ||||

| RSPIa: 4 channels | ||||

| SPIBSC: 1 channel of multi-I/O serial flash memory connectable | ||||

| Memory interfaces | SPI 4ch | |||

| QSPI(Flash I/F) with Direct Access from CPU | ||||

| SRAM I/F(32bit bus) | ||||

| SDRAM I/F(32bit bus) | ||||

| Burst ROM I/F(32bit bus) | ||||

| Encoder interfaces | - | A-format™, BiSS®-C, EnDat2.2, HIPERFACE®DSL, Tamagawa | - | A-format™, BiSS®-C, EnDat2.2, HIPERFACE®DSL, Tamagawa |

| A/D converter | 12-bit A/D converter: 2 units (unit 0: 8 channels; unit 1: 16 channels) | |||

| DMA | 16 channels x 2 units | |||

| Other functions | Built-in temperature sensor for measuring internal chip temperature | |||

| Safety features (register write protection, input clock oscillation stop detection, CRC, IWDTa, A/D self-diagnostics, error control module, etc.) | ||||

| Security functions (option): Secure boot, JTAG lock, etc. | ||||

| Power supply voltage | 3.3 V (I/O), 1.2 V (internal) | |||

| Operating temperature range | Tj = -40℃ ~ +125℃ | |||

Pin Count / Memory Size:

SRAM

| 1568KB | ● | |

|---|---|---|

| 544KB | ● | ● |

Pins | 176 | 320 |

Block Diagram:

with R-IN engine

without R-IN engine

*Arm and Cortex are registered trademarks of Arm Limited (or its subsidiaries) in the EU and/or elsewhere.

All rights reserved.

*EtherCAT is a patented technology that Renesas has licensed from Beckhoff Automation GmbH, and is a registered trademark.

*EtherNet/IP is a trademark of ODVA.

*BiSS is a registered trademark of iC-Haus.

*CAN(Controller Area Network):An automotive network specification developed by Robert Bosch GmbH of Germany.

*All other names of products or services mentioned here are trademarks or registered trademarks of their respective owners.

* A-format is a trademark of the Nikon Corporation.

*HIPERFACE DSL is registered trademark of SICK STEGMANN GmbH.

*EnDat is registered trademark of DR. JOHANNES HEIDENHAIN GmbH.

• 可按需提供包括驱动光耦、隔离放大、隔离通信的隔离器件、AC/DC、DC/DC、LDO辅助电源及编码器,以及保险丝、滤波器、TVS管等保护器件,器件配套齐全。

【伺服控制】

伺服控制是为满足某种目的,产生运动和对物体运动进行控制是我们人类最重要的活动之一。伺服控制是对物体运动的位置、速度及加速度等变化量的有效控制。

责任编辑:Davia

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)