基于Microsemi公司的PolarFire FPGA系列开发方案

394

394

拍明

拍明

原标题:Microsemi PolarFire FPGA系列开发方案

Microsemi公司的PolarFire FPGA系列具有最低功耗最佳成本的中等规模的FPGA,逻辑单元(LE)从100K到500K,12.7G 收发器, 1.6 Gbps I/O,比同类产品的功耗低50%以上.主要用在物联网(IoT),工业自动化,通信设备,有线接入网,蜂窝基础设备,国防和航空通信领域.本文介绍了PolarFire FPGA系列主要特性,低功耗特性,可靠性和安全特性,框图,以及评估板MPF300-EVAL-KIT-ES主要特性,框图和电路图.

PolarFire™ FPGAs are the fifth-generation family of non-volatile FPGA devices from Microsemi, built on state-of-the-art 28nm non-volatile process technology. Cost-optimized PolarFire FPGAs deliver the lowest power at mid-range densities. PolarFire FPGAs lower the cost of mid-range FPGAs by integrating the industry’s lowest power FPGA fabric, lowest power 12.7 Gbps transceiver lane, built-in low power dual PCI Express Gen2 (EP/RP), and, on select data security (S) devices, an integrated low-power crypto co-processor. PolarFire FPGAs can operate at 1.0 V and 1.05 V, offering the end user the ability to trade off power and performance to match the application requirements.

Microsemi's lowest power, cost-optimized mid-range PolarFire FPGA engineering samples are now available for all customers. The PolarFire FPGA family spans from 100K logic elements (LEs) to 500K LEs, features 12.7G transceivers, and offers up to 50% lower power than competing mid-range FPGAs. The devices are ideal for a wide range of applications within wireline access networks and cellular infrastructure, defense and commercial aviation markets, as well as industrial automation and IoT markets.

Cost-optimized Architecture

Architecture and process optimizations for 100K/500K LE devices

Transceiver performance optimized for 12.7 Gbps, which yields smaller size

1.6 Gbps I/Os—hardened I/O gearing logic with CDR (supports SGMII/GbE links on these GPIOs)

Best-in-class high-performance, hardened security IP in mid-range devices

Power Optimization

The lowest static power—1/10 static power vs. competing devices

Transceiver optimized for 12.7 Gbps, which yields 1/2 the power vs. competing devices

Low power Flash*Freeze mode yields best-in-class standby power

Integrated hard IP—DDR PHY, PCIe endpoint/root port, crypto processor

Total power (static and dynamic)—up to 50% lower power

PolarFire FPGAs deliver up to 500K logic elements, 12.7G transceivers at 50% lower power.

PolarFire FPGA系列主要特性:

Up to 481K logic elements consisting of a 4-input look-up table (LUT) with a fractureable D-type flipflop

20 Kb dual- or two-port large static random access memory (LSRAM) block with a built-in single error

correct double error detect (SECDED)

64 × 12 two-port μRAM block implemented as an array of latches

18 × 18 math block with a pre-adder, a 48-bit accumulator, and an optional 16 deep x 18 coefficient ROM

Built-in μPROM, modifiable at program time, readable at run time for user data storage

High-speed serial connectivity with built-in multi-gigabit multi-protocol transceivers from 250 Mbps

to 12.7 Gbps

Integrated dual PCIe for up to ×4 Gen2 endpoint (EP) and root port (RP) designs

High-speed I/O (HSIO) supporting up to 1600 Mbps DDR4, 1333 Mbps DDR3L, and 1333 Mbps

LPDDR3/DDR3 memories with integrated I/O digital

General purpose I/O (GPIO) supporting 3.3 V, built-in CDR for serial gigabit Ethernet, 1067 Mbps

DDR3, and 1600 Mbps LVDS I/O speed with integrated I/O digital logic

Low-power phase-locked loops (PLLs) and delay-locked loops (DLLs) for high precision and low-jitter

1.0 V and 1.05 V operating modes

PolarFire FPGA系列低功耗特性:

Low device static power

Low inrush current

Low power transceivers

Unique Flash*Freeze (F*F) mode

PolarFire FPGA系列可靠性特性:

FPGA configuration cells single event upset (SEU) immune

Built-in SECDED and memory interleaving on LSRAMs

System controller suspend mode for safety-critical designs

PolarFire FPGA系列安全特性:

Cryptography Research Incorporated (CRI)-patented differential power analysis (DPA) bitstream

protection

Integrated physically unclonable function (PUF)

56 KBytes of secure non-volatile memory (sNVM)

Built-in tamper detectors and countermeasures

Digest integrity check for FPGA, μPROM, and sNVM

Data security features in S devices—true random number generator, integrated Athena TeraFire

EXP5200B Crypto Coprocessor, suite B capable, and CRI DPA countermeasure pass-through license

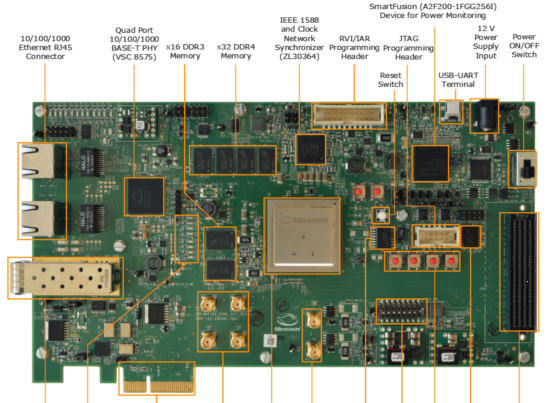

PolarFire FPGA评估板MPF300-EVAL-KIT-ES

Microsemi’s PolarFire Evaluation Kit is an ideal platform for evaluating the lowest power, cost-optimized, non-volatile PolarFire FPGAs. This kit has a full-featured 300K LE PolarFire FPGA, which integrates reliable non-volatile FPGA fabric, 12.7 Gbps transceivers, 1.6 Gbps I/Os, best-in-class-performance, hardened security IP, and crypto processors. The silicon features power optimization with the lowest static power for 28 nm non-volatile FPGAs, its low power mode; Flash*Freeze yields best-in-class standby power and it has integrated DDR PHY, PCIe endpoint/root port, crypto processor hard IPs.

评估板MPF300-EVAL-KIT-ES主要特性:

300K LE PolarFire FPGA in an FCG1152 package (MPF300TS-1FCG1152I)

HPC FMC connector

1x SFP+ cage

IEEE1588 phase-locked loop (PLL)

SMA connectors for testing of full-duplex 12.7Gbps SerDes channel

4GB DDR4 x32 and 2GB DDR3 x16

PCI Express (x4) edge connector

2 x RJ45 for 10/100/1000 Ethernet using serial gigabit media-independent interface (SGMII) on general purpose input/output (GPIO)

Dual 10/100/1,000 BASE-T PHY (VSC8575) for SyncE and 1588 application

Power management unit for 1 or 1.05 volt (V) PolarFire FPGA core voltage

USB to universal asynchronous receiver/transmitter (UART) interface

Embedded programming and debugging using serial peripheral interface (SPI) and Joint Test Action Group (JTAG)

On-board power monitoring

2 x 1Gb SPI flash memory

图. 评估板MPF300-EVAL-KIT-ES外形图

责任编辑:HanFeng

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)