基于Lattice ECP5的SoC电子流媒体后视镜解决方案

348

348

拍明

拍明

自通用汽车旗下凯迪拉克品牌推出采用流媒体后视镜的车型后,越来越多的车厂开始将目光及方向瞄准了流媒体后视镜,而流媒体后视镜也的确为车主的行车安全提供了更大的便捷、更安全的行车保障,注定未来成为趋势。

大联大世平推出的该方案全部采用符合车厂质量标准AEC-Q100原件,以Lattice 40nm低功耗ECP5 FPGA为核心,内置RISC-V软核处理器,使用单芯片SoC方案实现电子流媒体镜功能,支持去雾除霾、夜视增强、电子防眩光及电子变焦等。

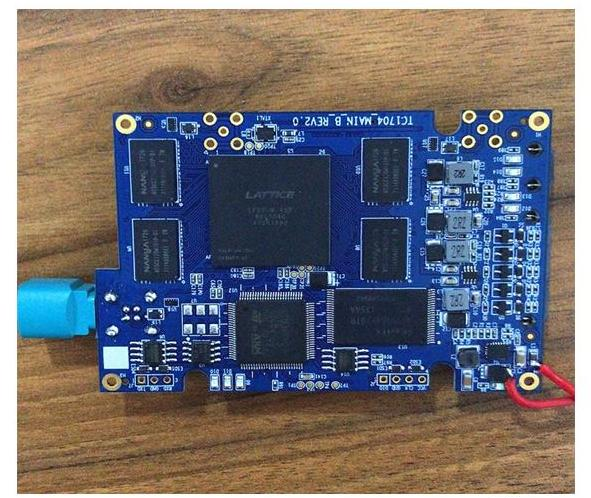

图示1-大联大世平联合深圳驰晶科技推出基于Lattice ECP5的SoC电子流媒体后视镜系统方案图

功能描述

符合车规标准的TVI摄像头或LVDS摄像头;

支持最大85度的后视可视范围,大范围降低车主的视觉盲区;

夜视增强,WDR(电子防眩光),雾天及霾天具有智能去雾霾图像增强功能;

完美替代玻璃后视镜全球研发足迹,以确保汽车质量、稳健性和高产量。

图示2-大联大世平联合深圳驰晶科技推出基于Lattice ECP5的SoC电子流媒体后视镜的方案照片

重要特性

低功耗40nm FPGA;

支持高达1080p摄像头输入,低于50ms的延迟,60fps高帧率;

支持硬件并行去雾除霾及电子变焦功能;

支持MIPI DSI/LVDS推屏;

低成本,全车规零件规格,软件环境支持ISO26262汽车前照大灯客户应用。

【ECP5 和 ECP5-5G】

为您的桥接以及加速应用打破功耗、尺寸和成本方面的限制

投入更少,获得更多——ECP5和ECP5-5G器件相比竞争对手的FPGA产品成本低40%,使用更好的布线架构、双通道SERDES以及增强的DSP模块,减少高达4倍的乘法器资源使用,致力于为ASIC和ASSP提供互连。

小尺寸封装,两倍功能密度——采用10x10 mm、0.5mm引脚间距封装,拥有高达85K LUT,并带有SERDES。适当地精简封装引脚,便于采用目前低成本的PCB布线技术。

功耗降低30%——使用单通道SERDES时静态和动态功耗低于0.25W,使用四通道SERDES时功耗低于0.5W。

特性

ECP5支持最高3.2 Gbps SERDES速率,ECP5-5G支持最高5 Gbps SERDES速率

器件拥有双通道模块,可提供最多4通道,实现更高的粒度

增强的DSP块为对称滤波器提供2倍的资源节约

单事件翻转(Single event upset, SEU)应对支持

可编程IO支持LVCMOS 33/25/18/15/12、XGMII、LVTTL、LVDS、Bus-LVDS、7:1 LVDS、LVPECL以及MIPI D-PHY输入接口

【ECP5 Versa开发套件】

ECP5互连平台——设计工程师可使用该套件评估ECP5 FPGA关键的互连功能,包括PCI Express、千兆以太网、DDR3和通用SERDES的性能。

快速实现用户功能的原型开发——使用ECP5 Versa开发板,设计工程师能够快速实现基于ECP5 FPGA的原型开发和测试。

概念验证演示——设计工程师现可下载多款适用于该开发板的演示,加速PCI Express、千兆以太网、DDR3、软错误修正(SEC)和通用SERDES性能的开发。

特性

半长的PCI Express:可实现PCI Express x1互连演示

1个全双工SERDES通道可通过SMA连接进行电气测试

支持USB-B连接,用于UART和器件编程

2个RJ45接口用于10/100/1000以太网至RGMII

板上引导闪存:128M串行SPI闪存

DDR3-1866存储器(64Mb/x16)

用于原型开发的扩展夹层互连

14段字母-数字显示

用于演示的开关、LED和显示器

Diamond®软件提供编程支持

板上参考时钟源

ECP5 FPGA支持DDR3,存储速率高达800Mbps。

责任编辑:Davia

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)