Lattice ECP5-5G系列低功耗无缝连接解决方案

409

409

拍明

拍明

原标题:Lattice ECP5-5G系列低功耗无缝连接解决方案

lattice公司的ECP5-5G系列是支持5G SERDES和有多达85K LUT的FPGA,支持的5G协议包括PCI Express Gen 2.0, CPRI和JESD204B,能无缝地连接到ASIC和ASSP,主要应用包括照相机,显示器,游戏平台,小性和低端路由器.本文介绍了ECP5-5G系列主要特性和优势,以及ECP5™ PCI Express板主要特性,框图,电路图和材料清单.

Lattice’s ECP5-5G family is the only FPGA product line supporting 5G SERDES and up to 85K LUTs in a small 10x10 mm package. The ECP5-5G devices support multiple 5G protocols including PCI Express Gen 2.0, CPRI, and JESD204B. This product family enables seamless connectivity to ASICs and ASSPs in a wide array of applications including cameras, displays, gaming platforms, small cells and low-end routers. Numerous resources including software, device samples, soft IP and hardware boards are available upon request.

Designers of equipment for many emerging high volumeapplications are blending FPGAs with ASICs and ASSPs torapidly build flexible systems that meet tight cost, power and formfactor constraints. In developing the ECP5TM FPGA family, Latticebreaks the rule that all FPGAs should be the highest density,power hungry, and expensive. With a focus on compact, highvolume applications, Lattice optimized the ECP5 architecture forlow cost, small form factor and low power consumption. Thesecharacteristics make the ECP5/ECP5-5G devices ideal fordelivering programmable connectivity solutions to complementASICs and ASSPs.

With up to 85K LUTs, 3.7Mbits embedded memory, 156 sysDSP blocks with DDR support, four 3.2Gbps/5Gbps SERDES channelsand 365 user IO, the ECP5/ECP5-5G devices provide a low-cost solution that meets the common connectivity requirements forcomplementing ASICs and ASSPs. A broad range of interface standards are supported including DDR3, LPDDR3, XGMII and7:1 LVDS, PCI Express, Ethernet (XAUI, GbE, SGMII) and CPRI. The devices are offered in multiple package options, and alsoinclude support for encryption and dual boot capabilities. Smart depopulation of balls simplifies PCB board routing and reducescost by utilizing fewer layers. Low power enhancements include stand-by mode operation of the individual blocks including SERDES,dynamic IO bank controllers and reduced operating voltage. The ECP5 family is supported by the Lattice DiamondTM designsoftware, the leading-edge design and implementation tool optimized for cost sensitive, low-power Lattice FPGA architectures.

ECP5-5G系列主要特性和优势:

Cost Optimized Architecture

• Focused on providing best value below 100K LUTs.

• Smart ball depopulation simplifies package integration withexisting PCB technology.

• Double Data Rate capability improves DSP block utilization.

Small Packages with High Functional Density

• 85K LUTs in 10x10 mm, 0.5 mm pitch package with SERDES.

Low Power Consumption

• Single channel SERDES functions below 0.25W.

• Quad channel SERDES functions below 0.5W.

ECP5™ PCI Express板

The ECP5™ PCI Express Board allows designers to investigate and experiment with the features of the ECP5 Field-Programmable Gate Array. The features of the ECP5 PCI Express Board can assist engineers with rapid prototyping and testing of their specific designs. The guide is intended to be referenced in conjunction with demo user’s guides to demonstrate the ECP5 FPGA.

图2.ECP5™ PCI Express板外形图

ECP5™ PCI Express板主要特性:

• PCI Express form-factor

– Allows demonstration of PCI Express x4 interconnection

• USB-B connection for UART and device programming

• One RJ45 interfaces to 10/100/1000 Ethernet to RGMII

• On-board Boot Flash – 128M Serial SPI Flash

• 8GB LPDDR3 memory components (256Mbx32)

• Expansion connections and headers

– Allows flexibility for user prototype expansion

• Switches, LEDs and displays for demo purposes

• Lattice Diamond® Programmer configuration support

• On-board reference clock sources

• Easy power measurements

– All ECP5 rails have probable power resistors

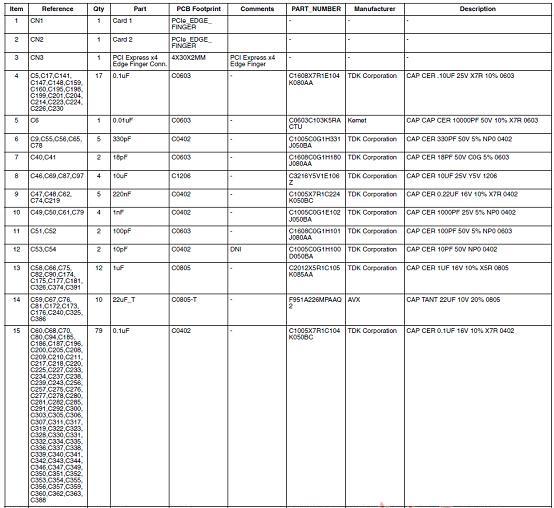

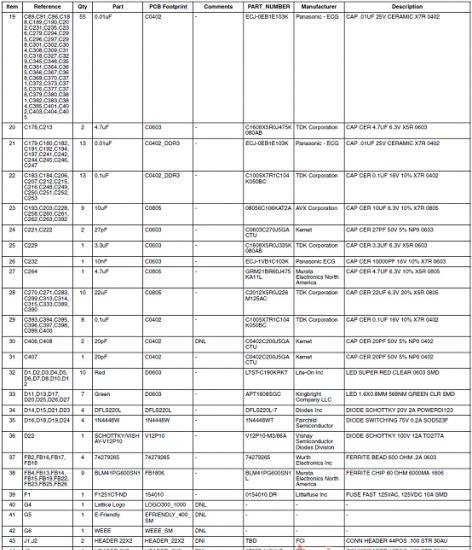

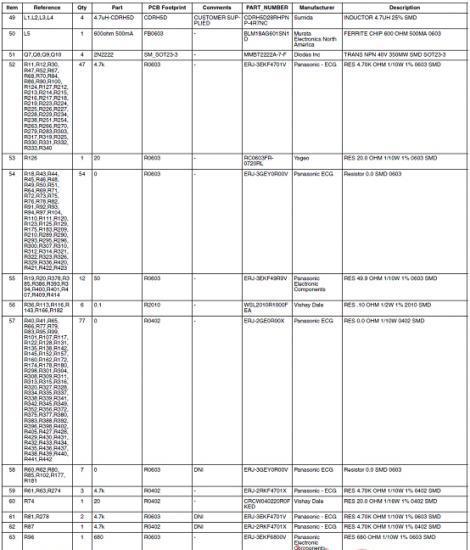

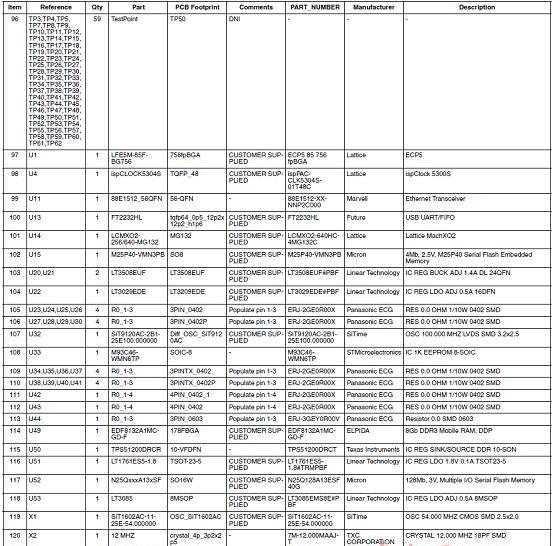

ECP5™ PCI Express板材料清单(BOM):

责任编辑:HanFeng

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)