基于Si5380/Si5381/Si5382主控器件的一站式无线接入网时钟解决方案

226

226

拍明

拍明

Silicon labs DSPLL技术近10年来在性能和功能集成方面持续创新,已广泛应用于高性能领域内,互联网基础设施便是其中之一,有超过50Mu DSPLL设备上市,受到逾100个美国和国际专利保护。目前顶级互联网基础设施供应商都在使用Silicon Labs产品。

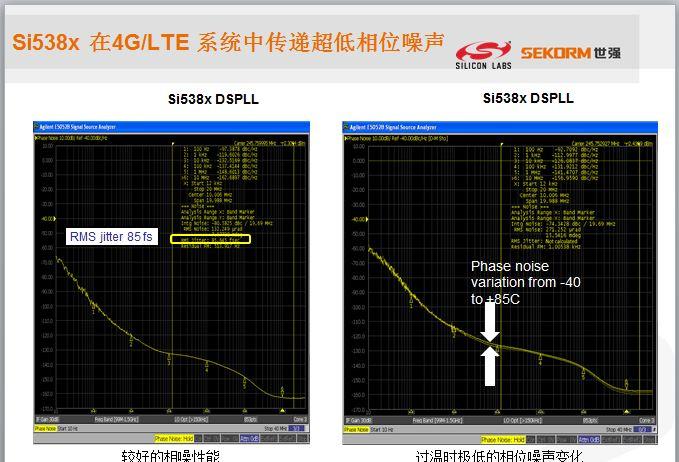

Silicon Labs无线时钟的简化处理方案采用先进的第四代DSPLL技术,不需要外部锁相环路器件,具有高度免疫板级噪声,其15GHz内部VCO提供更高频率范围,此外数字环路提供一致的、可重复的抖动传输,快速保持稳定。Si5381/Si5382单芯片时钟树方案可广泛应用于小型化蜂窝/多业务分配系统,同时满足4G/LTE和通用时钟设计需求。相较于传统方案,该方案不需要外部VCXO和滤波器,极低的使用面积,功耗只有1.3W,可自动无损伤切换,其中Si5381:4-PLL; Si5382: 2-PLL。

【Si5381/Si5382】

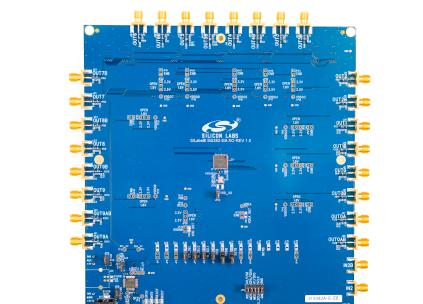

The Si5381/82A-E-EB is used for evaluating the Ultra-Low Phase Noise Quad/Dual PLL. The Si5381/82 employs fourth-generation DSPLL technology to enable clock generation for LTE/ JESD204B applications which require the highest level of jitter performance.

The Si5381/82A-E-EB has four independent input clocks and a total of 12 outputs with 4/2 PLLs. The Si5381/82A-E-EB also has four independent input clocks and a total of 12 outputs with 2 PLLs. The Si5381/82A-E-EB can be easily controlled and configured using Silicon Labs’ Clock Builder Pro™ (CBPro™) software tool.

The device revision is distinguished by a white 1 inch x 0.187 inch label with the text “Si5381/82A-E-EB” installed in the lower left hand corner of the board. (For ordering purposes only, the terms “EB” and “EVB” refer to the board and the kit respectively. For the purpose of this document, the terms are synonymous in context.)

EVB FEATURES

• Powered from USB port or external power supply

• Onboard 54 MHz XO provides holdover mode of operation on the Si5381/82

• CBPro GUI programmable VDDO supplies allow each of the ten primary outputs to have its own supply voltage selectable from 3.3, 2.5, or 1.8 V

• CBPro GUI-controlled voltage, current, and power measurements of VDD and all VDDO supplies

• Status LEDs for power supplies and control/status signals of Si5381/82

• SMA connectors for input clocks and output clocks

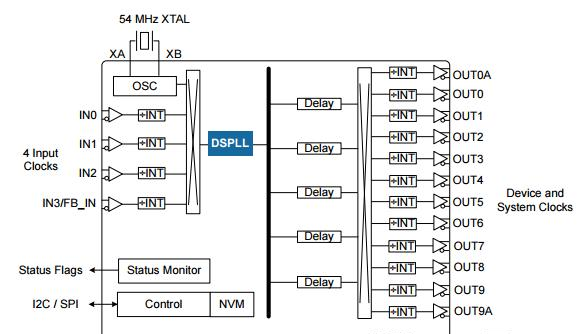

Si5381/82 Functional Block Diagram

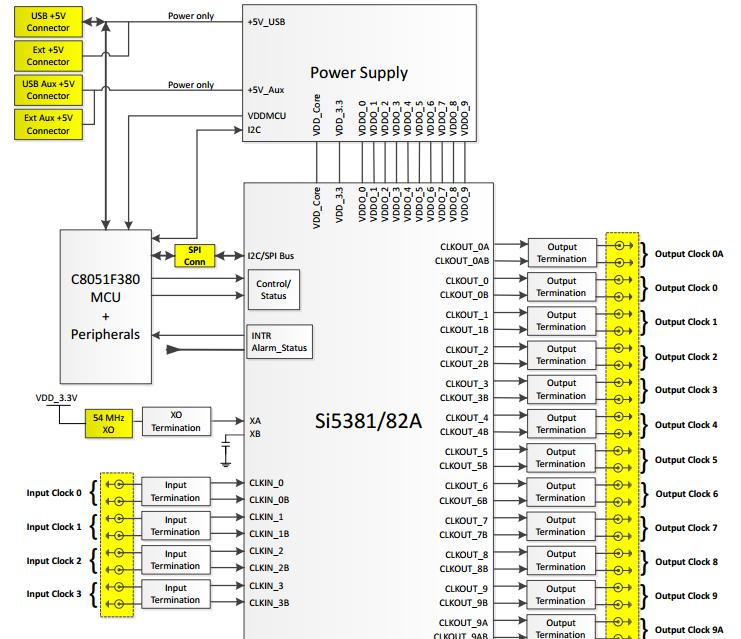

Below is a functional block diagram of the Si5381/82A-E-EB. This EB can be connected to a PC via the main USB connector for programming, control, and monitoring. See 2. Quick Start and Jumper Defaults or 6.1 Installing ClockBuilderPro (CBPro) Desktop Software for more information.

Note: All Si5381/82 schematics, BOMs, User’s Guides, and software can be found online at the following link: http://www.silabs.com/ si538x-4x-evb

Si5381/Si5382 Data Sheet

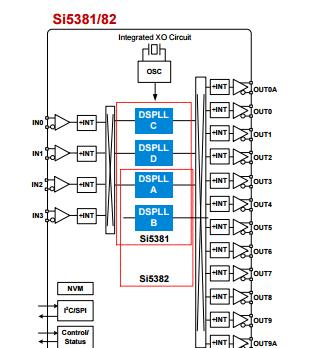

Multi-DSPLL Wireless Jitter Attenuating Clocks

The Si5381/82 is a wireless multi-PLL, jitter-attenuating clock that leverages Silicon Labs’ latest fourth-generation DSPLL technology to address the form factor, power, and performance requirements demanded by radio area network equipment, such as small cells, baseband units, and distributed antenna systems (DAS). The Si538x is the industry’s first multi-PLL wireless clock generator family capable of replacing discrete, highperformance, VCXO-based clocks with a fully integrated CMOS IC solution. The Si5381/82 features a multi-PLL architecture that supports independent timing paths for JESD wireless clocks with less than 85 fs typical phase jitter as well as Ethernet and other low-jitter, general-purpose clocks. DSPLL technology also supports free-run and holdover operation as well as automatic and hitless input clock switching. This unparalleled integration reduces power and size without compromising the stringent performance and reliability demanded in wireless applications.

KEY FEATURES

• Supports simultaneous wireless and general-purpose clocking in a single device

• Jitter performance: 85 fs RMS typ (12 kHz–20 MHz)

• Input frequency range:

• Differential: 8 kHz – 750 MHz

• LVCMOS: 8 kHz – 250 MHz

• Output frequency range:

• JESD204B: 480 kHz - 2.94912 GHz

• Differential: 1 Hz – 712.5 MHz Applications • LVCMOS: 480 kHz – 250 MHz

Applications

• Pico cells, small cells

• Mobile backhaul

• Multiservice Distributed Access Systems (MDAS)

Feature List

The Si5381/82 highlighted features are listed below.

• Digital frequency synthesis eliminates external VCXO and analog

loop filter components

• DSPLL_B supports high-frequency, wireless clocking. Remaining three DSPLLs support general-purposing clocking

• Integrated crystal option (Grade E)

• Input frequency range:

• Differential: 7.68 MHz–750 MHz

• LVCMOS: 10 MHz–250 MHz

• Output frequency range (DSPLL_B):

• Differential: up to 2.94912 GHz

• LVCMOS: up to 250 MHz

• Output frequency range (DSPLL_A/C/D):

• Differential: up to 735 MHz

• LVCMOS: up to 250 MHz

• Excellent jitter performance:

• DSPLL_B: 85 fs typ (12 kHz - 20 MHz)

• DSPLL_A/C/D: 150 fs typ (12 kHz - 20 MHz)

• Phase noise floor: –165 dBc/Hz

• Spur performance: –95 dBc max (relative to a 122.88 MHzcarrier)

• Flexible crosspoints route any input to any output clock

• Configurable outputs:

• Compatible with LVDS, LVPECL, LVCMOS, CML, HCSL

• Programmable signal amplitude

• Adjustable output-output delay: 68 ps/step, ±128 steps

• Independent output supply pins: 3.3, 2.5, or 1.8 V

• Core voltage:

• VDD = 1.8 V ±5%

• VDDA = 3.3 V ±5%

• Automatic free-run, lock, and holdover modes

• Digitally selectable loop bandwidth: DSPLL_B: 1 Hz to 4 kHz

• Hitless switching between input clocks

• Status monitoring (LOS, OOF, LOL)

• Serial interface: I2C or SPI in-circuit programmable with nonvolatileOTP memory

• ClockBuilderTM Pro software tool simplifies device configuration

• 4 input, 12 output, 64QFN

• Temperature range: –40 to +85 °C

• Pb-free, RoHS-6 compliant

Si5380是Silicon Labs推出的4G/LTE JESD204B标准时钟,支持下一代RRH设计应用,可以从14.7456GHz的频点任意整数整除分频输出,不需要外部VCXO或者环路滤波器,任意的抖动衰减,可配置电平格式输出和输出相位调整。此外,该款产品在封装尺寸、物料成本、功耗和性能等方面都具有明显的优势。

【Si5380】

Si5380 Rev D Data Sheet

Ultra-Low Phase Noise, 12-output JESD204B Clock Generator

The Si5380 is a high performance, integer-based (M/N) clock generator for small cell applications which demand the highest level of integration and phase noise performance. Based on Silicon Laboratories’ 4th generation DSPLL™ technology, the Si5380 combines frequency synthesis and jitter attenuation in a highly integrated digital solution that eliminates the need for external VCXO and loop filter components. A low-cost, fixed-frequency crystal provides frequency stability for free-run and holdover modes. This all-digital solution provides superior performance that is highly immune to external board disturbances such as power supply noise.

Applications:

• JESD204B clock generation

• Remote Radio Units (RRU), Remote Access Networks (RAN), picocells, small cells

• Wireless base stations (3G, GSM, W-CDMA, 4G/LTE, LTE-A)

• Remote Radio Head (RRH), wireless repeaters, wireless backhaul

• Data conversion sampling clocks (ADC, DAC, DDC, DUC)

KEY FEATURES

• DSPLL eliminates external VCXO and analog loop filter components

• Supports JESD204B clocking: DCLK and SYSREF

• Ultra-low jitter of 65 fs

• Input frequency range:

• External Crystal: 54 MHz

• Differential: 11.52 MHz to 737.28 MHz

• LVCMOS: 11.52 MHz to 245.76 MHz

• Output frequency range:

• Differential: 480 kHz to 1.47456 GHz

• LVCMOS: 480 kHz to 245.76 MHz

• Status monitoring

• Hitless switching

• Si5380: 4 input, 12 output, 64-QFN 9×9 mm

Feature List

The Si5380-D features are listed below:

• Digital frequency synthesis eliminates external VCXO and analog loop filter components

• Supports JESD204B clocking: DCLK and SYSREF

• Ultra-low jitter:

• 65 fs typ (12 kHz to 20 MHz)

• Input frequency range:

• Differential: 11.52 MHz to 737.28 MHz

• LVCMOS: 11.52 MHz to 245.76 MHz

• Output frequency range:

• Differential: up to 1.47456 GHz

• LVCMOS: up to 245.76 MHz

• Phase noise floor: –159 dBc/Hz

• Spur performance: –103 dBc max (relative to a 122.88 MHz carrier)

• Configurable outputs:

• Signal swing: 200 to 3200 mVpp

• Compatible with LVDS, LVPECL

• LVCMOS 3.3, 2.5, or 1.8 V

• Output-output skew using same N-divider: 65 ps (Max)

• Adjustable output-output delay: 68 ps/step, ±128 steps

• Optional Zero Delay mode

• Independent output clock supply pins: 3.3, 2.5, or 1.8 V

• Core voltage:

• VDD = 1.8 V ±5%

• VDDA = 3.3 V ±5%

• Automatic free-run, lock, and holdover modes

• Programmable jitter attenuation bandwidth: 0.1 Hz to 100 Hz

• Hitless input clock switching

• Status monitoring (LOS, OOF, LOL)

• Serial interface: I2C or SPI In-circuit programmable with nonvolatile OTP memory

• ClockBuilderTM Pro software tool simplifies device configuration

• Si5380: 4 input, 12 output, 64-QFN 9×9 mm

• Temperature range: –40 to +85 °C

• Pb-free, RoHS-6 compliant

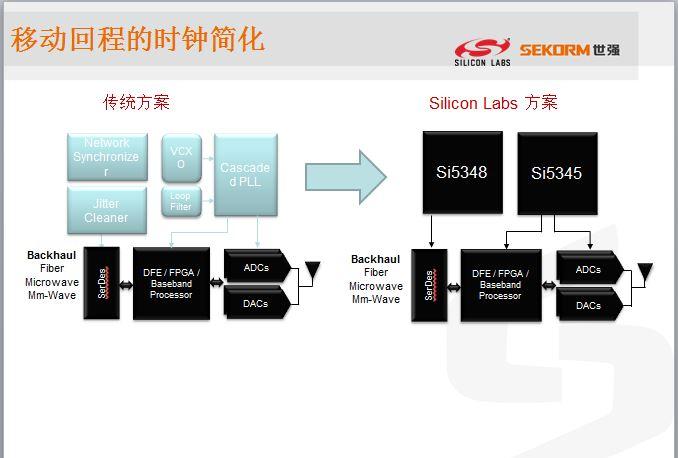

传统的基站移动回程方案不仅需要多个不同性能的时钟进行处理,并且采用PD(鉴相器)+VCO(压控振荡器)+LPF(低通滤波器)分离元件搭建的锁相环,会带入分离器件的噪声、漂移等因素,从而影响整个锁相环输出时钟的性能,同时需要搭建多个分离器件并占有PCB面积(如下图示)。针对上述繁冗设计,Silicon Labs推出Si5348+Si5345移动回程简化方案可规避这些缺点,其优势很明显:更小的BOM个数,低相噪/频率弹性,单芯片结构支持光纤、微波和毫米波等拓扑。

相关元件供应

型号:SI5380-D-EVB 品牌:SILICON LABS

【无线射频】

无线射频是20世纪90年代兴起的一种非接触式的自动识别技术。射频技术 相对于传统的磁卡及IC卡技术具有非接触、阅读速度快、无磨损等特点。 无线射频技术在阅读器和射频卡之间进行非接触双向数据传输,以达到目标识别和数据交换的目的。与传统的条型码、磁卡及IC卡相比,射频卡具有非接触、阅读速度快、无磨损、不受环境影响、寿命长、便于使用的特点和具有防冲突功能,能同时处理多张卡片。

RFID技术的基本工作原理并不复杂:标签进入磁场后,接收解读器发出的射频信号,凭借感应电流所获得的能量发送出存储在芯片中的产品信息(Passive Tag,无源标签或被动标签),或者主动发送某一频率的信号(Active Tag,有源标签或主动标签);解读器读取信息并解码后,送至中央信息系统进行有关数据处理。

一套完整的RFID系统, 是由阅读器(Reader)与电子标签(TAG)也就是所谓的应答器(Transponder)及应用软件系统三个部份所组成, 其工作原理是Reader 发射一特定频率的无线电波能量给Transponder, 用以驱动 Transponder电路将内部的数据送出,此时 Reader 便依序接收解读数据, 送给应用程序做相应的处理。

以RFID 卡片阅读器及电子标签之间的通讯及能量感应方式来看大致上可以分成, 感应偶合(Inductive Coupling) 及后向散射偶合(Backscatter Coupling)两种, 一般低频的RFID大都采用第一种式, 而较高频大多采用第二种方式。

阅读器根据使用的结构和技术不同可以是读或读/写装置,是RFID系统信息控制和处理中心。阅读器通常由耦合模块、收发模块、控制模块和接口单元组成。阅读器和应答器之间一般采用半双工通信方式进行信息交换,同时阅读器通过耦合给无源应答器提供能量和时序。 在实际应用中,可进一步通过Ethernet或WLAN等实现对物体识别信息的采集、处理及远程传送等管理功能。应答器是RFID系统的信息载体,目前应答器大多是由耦合原件(线圈、微带天线等)和微芯片组成无源单元。

责任编辑:Davia

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)