为什么以及如何使用Efinix FPGA进行AI/ML成像第2部分:图像捕获和处理

162

162

拍明芯城

拍明芯城

作者:Adam Taylor

编者注:FPGA 架构的新方法带来了更细粒度的控制和更大的灵活性,可以满足机器学习 (ML) 和人工智能 (AI) 的需求。这个由两部分组成的系列的第 1 部分介绍了Efinix的一种此类架构以及如何使用开发板开始使用它。在这里,第 2 部分讨论将开发板连接到外部设备和外设(例如相机),以及如何利用 FPGA 消除图像处理瓶颈。

FPGA 在许多应用中发挥着关键作用,从工业控制和安全到机器人、航空航天和汽车。由于可编程逻辑内核的灵活性及其广泛的接口功能,FPGA 的一个不断增长的用例是图像处理,可以在其中部署机器学习 (ML)。由于其并行逻辑结构,FPGA 非常适合实现具有多个高速摄像头接口的解决方案。此外,FPGA 还支持在逻辑中使用专用处理管道,从而消除与基于 CPU 或 GPU 的解决方案相关的共享资源瓶颈。

对 Efinix 的Titanium FPGA的第二次观察将检查 FPGA 的Ti180 M484开发板附带的参考图像处理应用程序。目的是了解设计的组成部分,并确定 FPGA 技术在哪些方面可以消除瓶颈或为开发人员带来其他好处。

基于 Ti180 M484 的参考设计

从概念上讲,参考设计(图 1)从多个移动行业处理器接口 (MIPI) 摄像头接收图像,在 LPDDR4x 中执行帧缓冲,然后将图像输出到高清多媒体接口 (HDMI) 显示器。 FPGA 夹层卡 (FMC) 和板上的四个Samtec QSE接口用于提供相机输入和 HDMI 输出。

图 1:从概念上讲,Ti180 M484 参考设计从多个 MIPI 相机接收图像,在 LPDDR4x 中执行帧缓冲,然后将图像输出到 HDMI 显示器。 >(图片来源:Efinix)

FMC至 QSE 扩展卡与 HDMI 子卡一起使用以提供输出视频路径,而三个 QSE 连接器用于连接 DFRobot SEN0494 MIPI相机。如果多个 MIPI 摄像头不可用,则可以通过环回单个摄像头通道来使用单个摄像头来模拟其他摄像头。

从高层次上看,此应用程序可能看起来很简单。然而,以高帧率接收多个高清 (HD) MIPI 流具有挑战性。这就是 FPGA 技术的优势所在,因为它允许设计人员并行利用多个 MIPI 流。

参考设计的架构利用 FPGA 的并行和顺序处理结构。并行结构用于实现图像处理流水线,而 RISC-V 处理器提供用于 FPGA 查找表 (LUT) 的顺序处理。

在许多基于 FPGA 的图像处理系统中,图像处理流水线可以分为两个元素,即输入流和输出流。输入流连接到相机/传感器接口,处理功能应用于传感器的输出。这些功能可以包括拜耳转换、自动白平衡和其他增强功能。在输出流中,图像已准备好显示。这包括更改颜色空间(例如,RGB 到 YUV)和对所需输出格式(例如 HDMI)的后处理。

通常,输入图像处理链以传感器像素时钟速率运行。这与以输出显示频率处理的输出链具有不同的时序。

帧缓冲区用于将输入连接到输出处理管道,通常存储在外部高性能存储器中,例如 LPDDR4x。该帧缓冲器在输入和输出管道之间解耦,允许以适当的时钟频率通过直接存储器访问来访问帧缓冲器。

Ti180 参考设计使用与上述概念类似的方法。输入图像处理管道实现了一个 MIPI 相机串行接口 2 (CSI-2) 接收器知识产权 (IP) 内核,它建立在 MIPI 物理层 (MIPI D-PHY) 的输入/输出 (I/O) 之上钛FPGA。 MIPI 是一个具有挑战性的接口,因为除了低速和高速通信之外,它还使用同一差分对上的单端和差分信号。在 FPGA I/O 中集成 MIPI D-PHY 降低了电路卡设计的复杂性,同时还减少了物料清单 (BOM)。

收到来自摄像头的图像流后,参考设计将 MIPI CSI-2 RX 的输出转换为高级可扩展接口 (AXI) 流。 AXI Stream 是一种单向高速接口,可提供从主机到从机的数据流。提供用于在主设备和从设备之间传输的握手信号(tvalid 和 tready)以及边带信号。这些边带信号可用于传送图像定时信息,例如帧开始和行结束。

AXI Stream 是图像处理应用的理想选择,使 Efinix 能够提供一系列图像处理 IP,然后可以根据应用的需要轻松集成到处理链中。

MIPI CSI-2图像数据和时序信号接收后,转换为AXI Stream,输入直接内存访问(DMA)模块,将图像帧写入LPDDR4x,作为帧缓存。

该 DMA 模块在蓝宝石片上系统 (SoC) 内的 FPGA 中的 RISC-V 内核的控制下运行。除了为 DMA 写入通道提供必要信息以将图像数据正确写入 LPDDR4x 之外,该 SoC 还提供停止和启动 DMA 写入等控制。这包括有关存储位置的信息以及以字节为单位定义的图像的宽度和高度。

参考设计中的输出通道在 RISC-V SoC 的控制下从 LPDDR4x 帧缓冲区读取图像信息。数据作为 AXI 流从 DMA IP 输出,然后从传感器提供的 RAW 格式转换为 RGB 格式(图 2),并准备通过板载 Analog Devices 的 ADV7511 HDMI 发射器 输出。

图 2:参考设计输出的示例图像。 (图片来源:亚当·泰勒)

DMA 的使用还使 Sapphire SoC RISC-V 能够访问存储在帧缓冲区中的图像,以及抽象统计数据和图像信息。 Sapphire SoC 还能够将叠加层写入 LPDDR4x,以便它们可以与输出视频流合并。

现代 CMOS 图像传感器 (CIS) 具有多种操作模式,可配置为提供片上处理,以及多种不同的输出格式和时钟方案。此配置通常通过 I²C 接口提供。在 Efinix 参考设计中,这种与 MIPI 相机的 I²C 通信由 Sapphire SoC RISC-V 处理器提供。

将 RISC-V 处理器集成到 Titanium FPGA 中可减少最终解决方案的整体尺寸,因为它无需实施会增加设计风险的复杂 FPGA 状态机,也无需实施会增加 BOM 的外部处理器。

包含处理器还支持使用额外的 IP 与 MicroSD 卡进行通信。这使得现实世界的应用程序可能需要存储图像以供以后分析。

总体而言,Ti180 参考设计的架构经过优化,可实现紧凑、低成本但高性能的解决方案,使开发人员能够通过系统集成降低 BOM 成本。

参考设计的主要优势之一是它们可用于在定制硬件上启动应用程序开发,使开发人员能够采用设计的关键元素并根据需要进行定制。这包括使用 Efinix 的 TinyML 流程来实现在 FPGA 上运行的基于视觉的 TinyML 应用程序的能力。这可以利用 FPGA 逻辑的并行特性和将自定义指令轻松添加到 RISC-V 处理器的能力,从而允许在 FPGA 逻辑中创建加速器。

执行

正如第 1 部分中所讨论的,Efinix 架构的独特之处在于它使用可交换逻辑和路由 (XLR) 单元来提供路由和逻辑功能。像参考设计这样的视频系统是一个混合系统,逻辑和布线都很繁重:需要大量的逻辑来实现图像处理功能,并且需要大量的布线来以所需的频率连接 IP 单元。

该参考设计在设备中使用了大约 42% 的 XLR 单元,为添加提供了充足的空间,包括自定义应用程序,例如 edge ML。

块 RAM 和数字信号处理 (DSP) 块的使用也非常高效,仅使用 640 个 DSP 块中的 4 个和 40% 的内存块(图 3)。

图 3:Efinix 架构上的资源分配显示仅使用了 42% 的 XLR 单元,为其他进程留下了充足的空间。 (图片来源:亚当·泰勒)

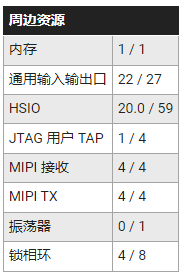

在设备 IO 上,LPDDR4x 的 DDR 接口用于为 Sapphire SoC 和图像帧缓冲区提供应用程序内存。所有设备专用的 MIPI 资源都与 50% 的锁相环一起使用(图 4)。

图 4:所用接口和 I/O 资源的快照。 (图片来源:亚当·泰勒)

通用 I/O (GPIO) 用于提供 I²C 通信以及连接到 Sapphire SoC 的多个接口,包括 NOR FLASH、USB UART 和 SD 卡。 HSIO 用于向 ADC7511 HDMI 发送器提供高速视频输出。

使用 FPGA 进行设计的关键要素之一不仅是在 FPGA 内实施和适配设计,而且能够将逻辑设计置于 FPGA 内并在布线时实现所需的时序性能。

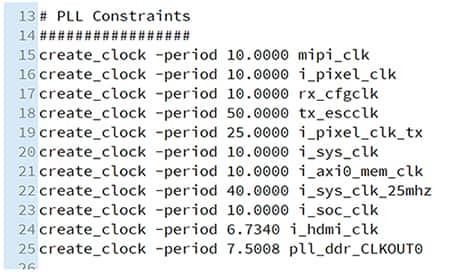

单时钟域 FPGA 设计的时代早已一去不复返了。 Ti180 参考设计中有几种不同的时钟,它们都以高频运行。最终时序表显示了系统内时钟达到的最大频率。这就是要求的时序性能也可以在约束中看到(图 5),HDMI 输出时钟的最大时钟频率为 148.5 兆赫兹 (MHz)。

图 5:参考设计的时钟约束。 (图片来源:亚当·泰勒)

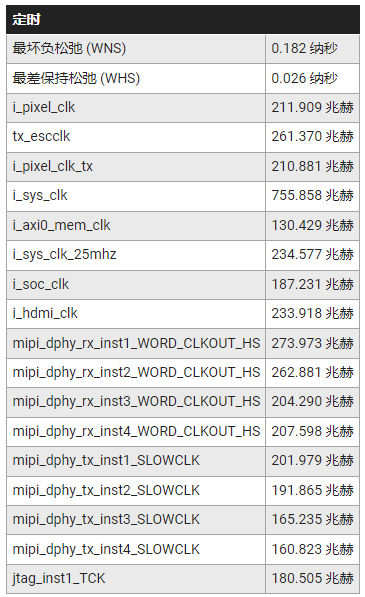

针对约束的时序实现显示了 Titanium FPGA XLR 结构的潜力,因为它减少了可能的路由延迟,从而提高了设计性能(图 6)。

图 6:针对约束的时序实现显示了 Titanium FPGA XLR 结构在减少可能的路由延迟方面的潜力,从而提高了设计性能。 (图片来源:亚当·泰勒)

结论

Ti180 M484 参考设计清楚地展示了 Efinix FPGA 的功能,尤其是 Ti180。该设计利用多个独特的 I/O 结构来实现支持多个传入 MIPI 流的复杂图像处理路径。该图像处理系统在软核蓝宝石 SoC 的控制下运行,该系统实现了应用程序的必要顺序处理元素。

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)