信号链基础知识之PGA驱动参考引脚的探讨

1

1

拍明

拍明

原标题:信号链基础知识之PGA驱动参考引脚的探讨

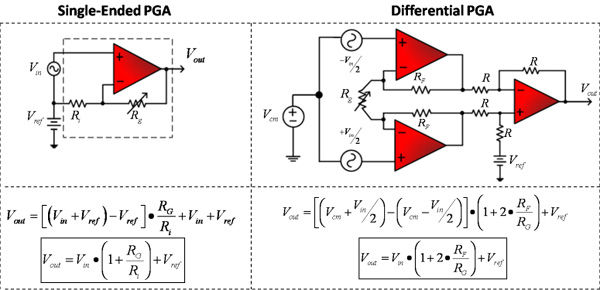

可编程增益放大器(PGA)是特殊的放大器结构(请参见图1),具有经过修整的内部电阻器网络,拥有比采用离散式电阻器组件的放大器更高的性能。正如图1中PGA传输函数所显示那样,PGA输出的误差与内部偏移电压(VOS)、增益精度和VREF精度有关。

图1:相应传输函数的PGA配置举例

在一些使用PGA的应用中,关键的DC规范为VOS、增益精度与偏移、噪声以及静态功耗。如果参考引脚VREF不以运算放大器缓冲电路驱动,则PGA传输函数的精度会受到极大影响。另外,从AC的角度来看,一个常见的难题是维持频率下的增益精度,其会受到参考引脚电压VREF以及对它起到缓冲作用的运算放大器的影响。

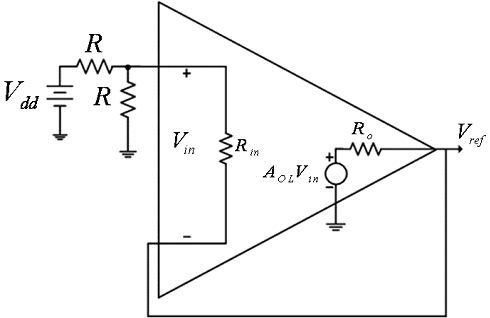

考虑到带宽、AOL(ω)、RO(ω) 和运算放大器缓冲电路的反馈系数 (β)(请参见图2)大小的情况下,我们便可以更好地理解运算放大器效应对VREF所产生的影响。

图2:Vref缓冲分压器电压

由于缓冲器本身β=1,因此输出电压VREF等于AOLVIN.VREF流入缓冲放大器反相输入端的输入偏置电流,决定了负载电流的大小程度。这一点非常重要,因为负载电流的大小会调节环路增益 (AOLβ) 和闭环输出阻抗ROUT.

图2显示了VREF缓冲器的闭环内部电路:Rout、Ro和AOL之间的重要关系如方程式1所示:

总之,随着频率不断增加,运算放大器通过减小AOL、增加Rout以及延长稳定时间来保持固定输出电压和低阻抗的能力下降。这会影响PGA增益误差的精度。

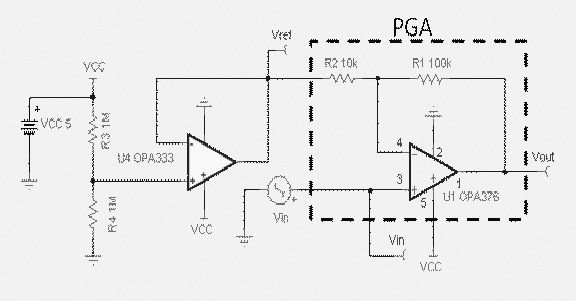

为了方便说明,请思考图3所示单端PGA之例。输入信号VIN有其DC组成部分(2.5V),而AC信号为一个200 mVpp、5 kHz正弦波:

图3:缓冲器单端PGA

万用表”功能对图5进行分析" src="https://supp.iczoom.com/images/public/202203/1646206377150059892.jpg" style="margin: 0px; padding: 0px; border: 0px; outline: 0px; vertical-align: middle; max-width: 800px;"/>

图4:以TINA Spice中的“万用表”功能对图5进行分析

我们可以利用TINA Spice中的“万用表”功能(请参见图4),获得输入电压对输出电压的RMS值,并用其计算总输出误差,具体计算方法如方程式2和3:

例如,微功耗精密运算放大器OPA333便拥有~350 kHz的增益带宽(GBW)积。因此,在5 kHz下,闭环特性会下降到造成第二个运算放大器(如OPA376)输出端产生0.08%误差的程度。若使用一个更高GBW的放大器(如:另一个精密运算放大器)便可减小这种误差。

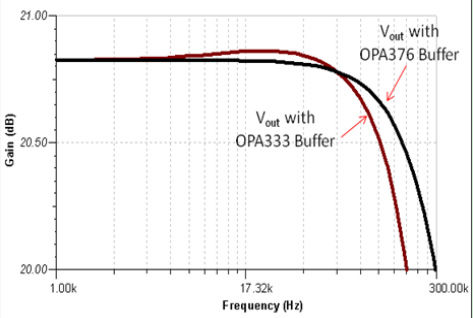

通过在TINA SPICE中绘制出传输函数(VOUT/VIN)与频率曲线图的关系图,我们可以直观地看到改变阻抗频率的效果(请参见图5)。请注意,相比OPA333,OPA376当作缓冲器时,增益与频率的关系更加恒定:

图5:OPA333和OPA376缓冲器比较图

结果表明,把一个带宽较高的运算放大器(例如:OPA376等)用作VREF缓冲放大器,可明显改善总输出误差。

责任编辑:

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)