Cadence® Sigrity™产品QIR2 新增功能

251

251

拍明

拍明

XtractIM

本节介绍Cadence® Sigrity™ 2017 QIR2版本中XtractIM™的新增功能。

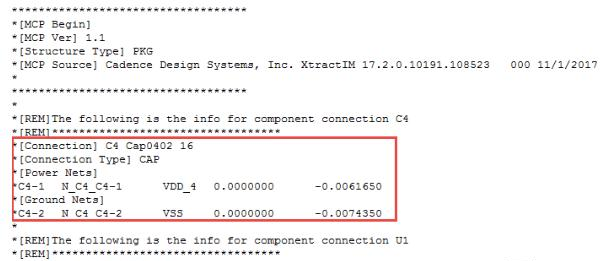

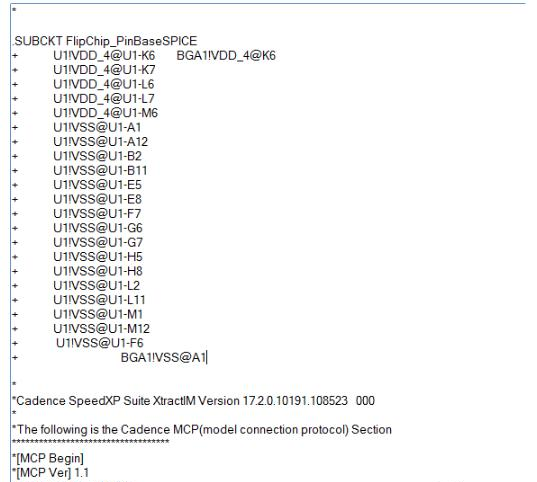

在MCP header中添加了去耦电容引脚

在该版本中,去耦电容的引脚信息被添加到由XtractIM生成的SPICE模型的MCPheader中。

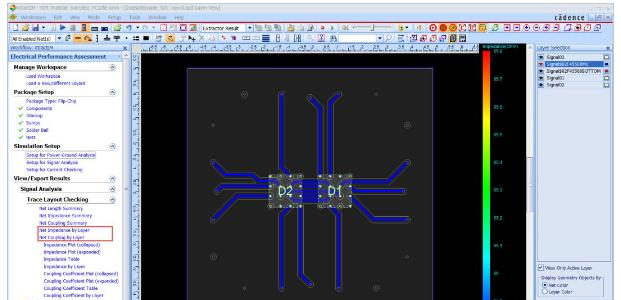

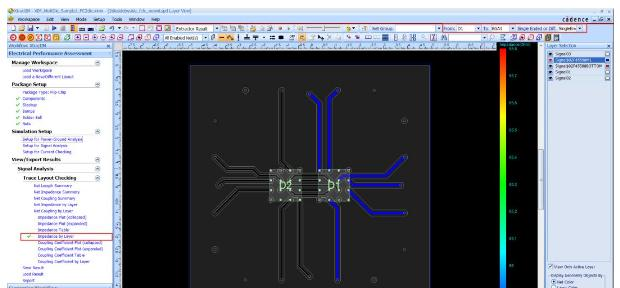

添加了新的选项来显示所有网络的阻抗和耦合结果,用于多Die封装设计

在该版本中,EPA模式中增加了一个新选项,用于显示多Die IC封装设计中所有网络的阻抗和耦合系数。

在以前的版本中,每层每次只能显示一个DIE到BGA的阻抗结果。

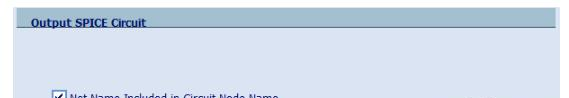

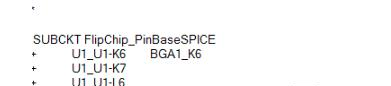

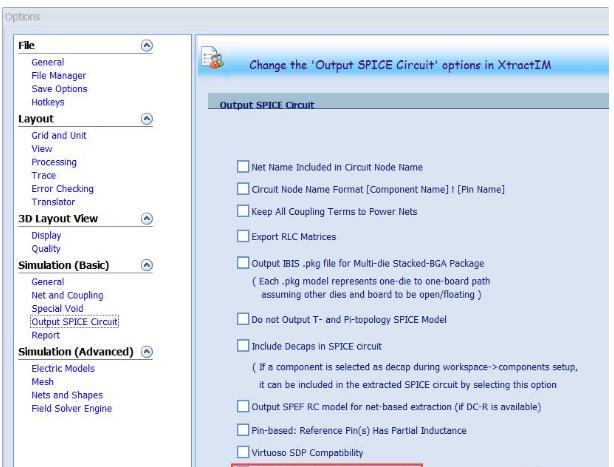

基于引脚的SPICE模型中增加了用于电路节点命名的新选项

在该版本中,添加了一个新的选项Circuit Node Name Format [Component] ! [Net Name] @ [Pin Name] 以提供另一种方法来定义电路节点名称的分隔符号。

选择此选项时,元器件名称和网络名称由!分隔,网络名称和引脚名称由@分隔。

在以前的版本中,基于引脚的SPICE模型中用于电路节点命名规则的分隔符号是下划线(_)。例如,U1_U1-A1。

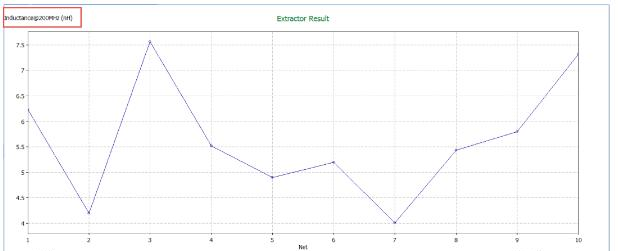

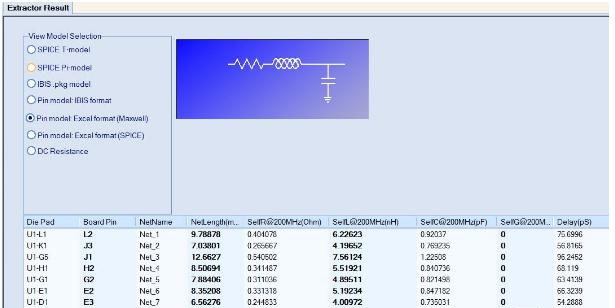

添加新选项用于在RLC报告中显示提取频率

新增加了在表格和图形结果中显示频率的选项,用于以GUI或者report方式查看仿真结果时,显示RLGC提取频率。

每个网络的RLC:

RLC表格:

添加了新的Tcl命令

模型提取模式中添加了以下新的Tcl命令:

导出耦合项的阈值

优化的带宽

电路拓扑

提取的频率范围

责任编辑:Davia

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)