基于TOSHIBA ApP Lite TZ2100人机界面HMI处理器的Voice Trigger智能冰箱解决方案

432

432

拍明

拍明

原标题:基于TOSHIBA ApP Lite TZ2100的Voice Trigger智能冰箱解决方案

TZ2100系列属于东芝ApP Lite家族产品 (ApP: Application Processor),应用范围含括工业设备、家用电器、娱乐和教育设备。此 Voice Trigger 完美的被嵌入在家电内形成智能冰箱,不用任何网络建置及使用上的相关支出,家中长辈/晚辈无需学习,也能无痛上手,轻松操作,与原始生活方式无异,提高便利。软件开放编写,与相关传感器搭配后,提供更多样化的可能性。

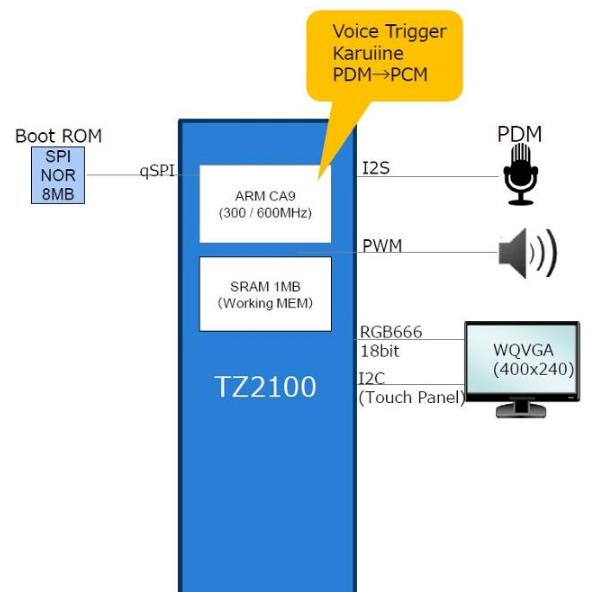

下图所示为一简单的范例,透过语音下达指令,即可完成相对应动作。

菜单 --> 冰箱 --> 打开 --> "打开冰箱"

场景应用图

产品实体图

展示板照片

方案方块图

核心技术优势

1、独立显示屏幕

2、全语音下达指令控制

3、依据语音控制选单完成相应动作

方案规格

1、PCB 尺寸 68 x 53 x 2 (mm)

2、PCB 重量 21.5 (g)

3、快速响应 (无网络延迟),高安全性

4、不需建置费 (包括网络费用),亦无运行成本

技术文档

| 类别 | 标题 | 档案 |

|---|---|---|

| 硬件 | Datasheet |

【TZ2100应用处理器】

人机界面(HMI)

处理器TZ2100

语音触发和文本语音朗读。

支持视频、图像和2D图形处理

相机并行接口

产品特点

TZ2100 Features

提供低BOM成本的语音控制解决方案

2D图形加速器

最高WVGA(800 x 480 pixel)@ 60fps

1MB的嵌入式大电容存储器(SRAM)

并行相机接口

以太网MAC:10/100Mbps

密码加速器

Arm® Cortex® -A9 300/600MHz

应用

Applications

工业设备、家用电器、娱乐设备和教育设备

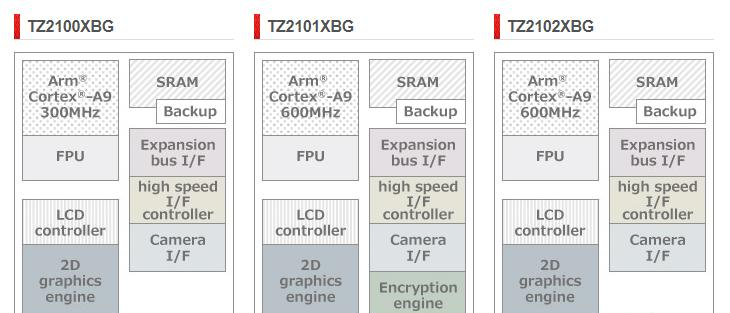

TZ2100系列

硬件规格

| 器件型号 | TZ2100XBG | TZ2101XBG | TZ2102XBG |

|---|---|---|---|

| 内核 | Arm® Cortex®-A9 MPCore L1I缓冲存储器:32kByte,L1D缓冲存储器:32kByte L2缓冲存储器:128kByte | ||

| 最大工作频率 | 300MHz | 600MHz | |

| FPU(浮点运算单元) | 集成 | ||

| 数据加密功能 | 不支持 | 支持 | 不支持 |

| RAM | 1MByte SRAM 32kByte SRAM(用于备份) | ||

| DRAM控制器 | DDR3/DDR3L × 16位 | ||

| 外部扩展总线接口 | 地址:27位,数据:32位 | ||

| 图形加速器 | 东芝原创的2D图形加速器 | ||

| LCD控制器 | WVGA(800 x 480像素)60fps,24位并行I/F | ||

| 高速接口控制器 | USB2.0主机接口、USB2.0设备接口、10/100以太网MAC | ||

| 外围功能 | DMA控制器、定时器/计数器、RTC | ||

| 外围 | 相机I/F,UART × 4,I2C × 4,I2S × 2,SPIM × 7,SPIB × 2,PWM × 6,12位ADC × 4,SDIO × 3,e-MMCx1,GPIO | ||

| 电源电压 | 内核=1.1V,I/O=3.3V | ||

| 封装 | LFBGA 310引脚,16mm x 16mm,0.8mm间距 | ||

| 状态 | 量产 | ||

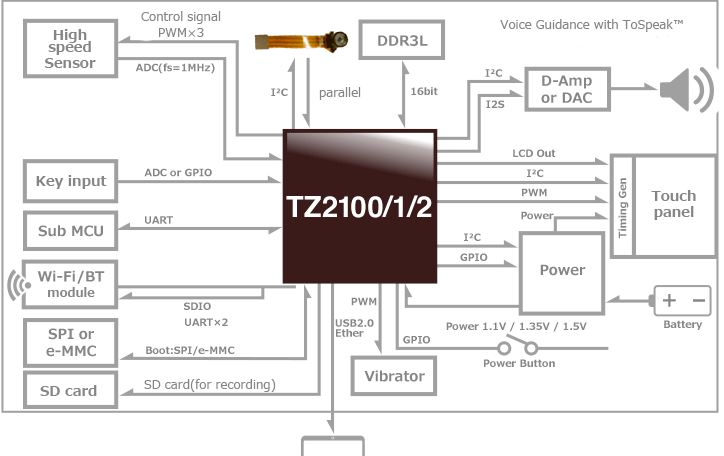

方框图

“配置引脚”设置举例

| TZ2100XBG | TZ2101XBG/TZ2102XBG | |||

|---|---|---|---|---|

| 设置举例 | 使用媒体I/F | 使用外部总线I/F | 使用媒体I/F | 使用外部总线I/F |

| CPU | Cortex-A9 300MHz +FPU L1I$ 32kB/L1D$ 32kB,L2$ 128kB | Cortex-A9 600MHz +FPU L1I$ 32kB/L1D$ 32kB,L2$ 128kB | ||

| 图形 | 2D图形(BitBLT) | - | 2D图形(BitBLT) | - |

| 安全性 (※可选) | - | 安全引擎(由TZ2101支持) | ||

| DRAM I/F | DDR3/3L x 16位 | DDR3/3L x 16位 | ||

| SRAM | 1MB 备份32kB | 1MB | ||

| 相机I/F | 8位并行相机 | - | 8位并行相机 | - |

| 外部总线I/F | - | A=27位,D=32位/16位/8位 | - | A=27位,D=32位/16位/8位 |

| LCD I/F | WVGA 60fps | - | WVGA 60fps 24位并行I/F | - |

| USB ※专用 | USB2.0主机/设备1通道(可选) | USB2.0主机/设备1通道 | ||

| 以太网 | 10/100以太网MAC | - | 10/100以太网MAC | - |

| RTC | 1 | 1 | ||

| SPIM(SPITX) SPIB SPIS | - 2通道 1通道 | 7通道 - - | - 2通道 1通道 | 7通道 - - |

| UART/PPI | 3ch | 4ch | 3通道 | 4ch |

| PWM | 6通道 | 6通道 | ||

| I2C | 4通道 | 2通道 | 4通道 | 2通道 |

| I2S | 2通道 | 2通道 | ||

| 定时器 WDT DMAC | 32位×9通道 1通道 8通道 | 32位×9通道 1通道 8通道 | ||

| ADC | 4通道 | 4通道 | ||

| SDIO/e-MMC/SD卡 | 3通道 | - | 3通道 | - |

| GPIO(MAX) | 128通道(专用4通道+共用124通道) | 128通道(专用4通道+共用124通道) | ||

| 封装 | BGA 310引脚(16mm × 16mm,0.8mm间距) | BGA 310引脚(16mm × 16mm,0.8mm间距) | ||

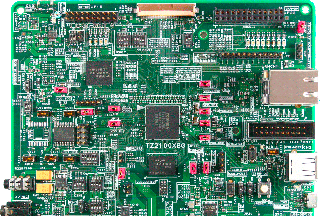

开发环境

TZ2100参考板是一种开发工具套件,包括用于评估TZ2100性能、软件急切评估和原型制作的评估板,通常与BSP(板支持包)结合使用。

评估板分为两种类型的板,一种可使用相机/LCD显示器,另一种可使用娱乐设备接口。至于BSP,根据不用的客户用途,有两种操作系统可供选择。

参考板概述

| 运输号 | RBTZ2100-1MA-A1 |

|---|---|

| CPU | TZ2102XBG |

| 概括 |  |

| 尺寸 | 150mm × 130mm |

| 主要功能 |

|

| 购买/租赁地点 | 请联系我们的销售部门 |

*1:http://www.ss-technologies.co.jp/en/index.html(将在新窗口中打开)

BSP(板支持包)规格

| 器件型号 | 操作系统 | 分配 | 设备驱动器 |

|---|---|---|---|

| RBTZ2100-1MA-A1 RBTZ2100-1MA-A2 | Linux® (Ubuntu®14.04 Arm hf) | gcc | 以太网,UART,SPIB,I2C,音频,GPIO,SPIM, USB(EHCI/OHCI),e-MMC,内存分配器,SD/SDIO |

| μ-ITRON | µC3/标准(eForce有限公司)**2 | 以太网,UART,SPIB,I2C,音频,GPIO,SPIM,内存分配器,SD/SDIO | |

| RBTZ2100-2MA-A2 | - | IAR嵌入式工作台EWARM(IAR系统®)*3 | UART,GPIO,I2C,SPIM,音频 |

*2:http://www.eforce.co.jp/products/microc3s(将在新窗口中打开)

*3:https://www.iar.com/iar-embedded-workbench/(将在新窗口中打开)

系统方框图举例

* Arm和Cortex是Arm有限公司(或其子公司)在美国和/或其它国家的商标或注册商标。

* Linux 是Linus Torvalds在美国和其它国家的注册商标。

* 所有其它商标和商品名称是它们各自所有者的财产。

【TZ2100XBG】

ApP Lite

产品概要

Feature | Arm®Cortex®-A9 Clock:300MHz(Max)/DDR3/3L I/F,1MB SRAM embeded/Graphics Acceleration,Camera input,LCD controller/Low power system technology,Long-term data retention/USB2.0/Ether |

Application Scope | Amusement system/Environment data mining system/Smart home appliance/User interface system |

RoHS Compatible Product(s)(#) | Available |

I/O | Camera input(Parallel)/DDR3/DDR3L/Ether/External Bus/I2C/I2S/LCD Output(Parallel)/SDIO/e∙MMC™/SPI/UART/USB2.0 |

CPU | Arm®Cortex®-A9 MPCore |

FPU | Available |

RAM | 1MByte SRAM/32kByte SRAM(Back-up) |

graphic engine | TOSHIBA original graphics accelerator |

Cache | L1D Cache:16kByte/L1I Cache:16kByte/L2 Cache:128kByte |

high speed interface controller | USB2.0 host interface/USB2.0 device interface/10/100 Ethernet MAC |

DRAM controller | DDR3/DDR3L×16bit |

LCD controller | WVGA(800×480)60fps,24bit Parallel I/F |

Expansion bus I/F | Address:27bit,Data:32bit |

Peripherals | DMA controller/Timer/counter/RTC |

Peripheral I/F | Camera I/F,UART×4,I2C×4,I2S×2,SPIM×7,SPIB×2,PWM×6,12bitADC×4,SDIO×3,eMMCx1,GPIO |

封装类型

Toshiba Package Name | P-LFBGA310-1616-0.80-001 |

Pins | 310 |

Package size | 16mm x 16mm x 1.6mm |

Pin pitch | 0.8mm |

Please refer to the link destination to check the detailed size.

Absolute Maximum Ratings

Characteristics | Symbol | Rating | Unit |

Operating frequency(max) | 300 | MHz | |

operating temperature(Tc) | -20 to 75 | ℃ |

产品特性

项目 | 符号 | 条件 | 数值 | 单位 |

power supply voltage | - | I/O:3.3V |

TZ2100 Series

Application Processor Lite ApP Lite

Overview

TZ2100 series are application processors utilizing a single 600 MHz Arm® Cortex® -A9 core with a floating point unit (FPU), a 2D graphics, a parallel LCD controller interface, camera input interface and an 1 MB of integrated SRAM. This device is highly integrated, as a main processor for various applications with integrated a USB host or device controller (optional), an Ethernet controller, an extended external buses, and rich interfaces.

The TZ2100 processors are supported a security service with an encryption and decryption capability (optional) to enable construction of a robust secure system. These products are suitable for various applications, in addition, an SRAM and a RTC for back-up mode of power state are incorporated.

The TZ2100 series are family products of ApP Lite.

Applications

This product is leveraged to meet needs of following applications; human machine interface, machine to machine interface, single-board computing and portable data terminal.

Features

●Host CPU

‒Arm® Cortex®-A9 MP Core (Revision r4p1) Up to 600 MHz operation frequency

‒Arm®v7-A instruction set architecture

‒Floating point unit (FPU)

‒32 KB L1 I cache/ D cache

‒128 KB L2 cache

‒Memory management unit: 128-entry TLB

‒Debug technology:

Arm® CoreSightTM (revision: r2p0-01)

v7 debug architecture, JTAG debug interface

‒Proprietary low power mode for WFI

●System contoller

‒System management unit (SMU):

Reset management, clock controller

‒Power management unit (PMU):

External and internal power management

‒Secure services (optional)

AES, SHA-1, SHA-256, RSA

Random number generator (RNG)

‒Interruption controller

●SDRAM controller

‒DDR3 / 3L memory interface (16-bit width)

‒Data rate: 800 Mbps

‒Memory size: up to 512 MB

‒ODT control

●Integrated SRAM

‒1 MB SRAM

‒32 KB SRAM for data backup

Low power dissipation for data retention

●Real time clock (RTC)

Low power dissipation

‒Clock frequency: 32.768 kHz

‒Clock timer, Calendar

‒Time adjustment, alarm interrupt, Periodic interrupt, BCD format

●DMA controller

‒AXI protocol DMA with DMA330 supported

‒Multiple transfer mode

Memory to Memory, Memory to Peripheral, and Peripheral to Memory

‒8 channels thread for DMA transfer and one channel thread for DMA management

●Timer

‒16 channels of 32-bit down counter enable one channel as watch dog timer

●2D graphics accelerator

‒Toshiba original graphics accelerator

‒Blitting, Rotation, Transforming, Drawing

●YUV to RGB converter

‒Input format: YUV 4:2:0 8bit, YUV 4:2:2 8bit

‒Input resolution: QVGA, VGA, up to 2048×2048

‒Output format: RGBA8888, ARGB8888, RGB565,

RGB888

●LCD controller

‒Parallel output: RGB 24 bits

‒Output resolution: up to WVGA

‒Frame rate: up to 60 fps

‒Input format: RGBA8888, ARGB8888, RGB565, ARGB1555

‒Alpha blending: up to five planes

●Camera input:

‒One channel

‒Parallel input: 8-bit Data

‒Frame rate: up to 60 fps

‒Resolution (by 8-pixel): up to 2048 × 2048

‒Input format: YUV 4:2:2 8-bit, RAW8, RGB565, ITU-RBT.656

●Audio interfaces

‒Two channels: 1 channel dedicated for output

1 channel for input and output

‒Format: I2S stereo, LR stereo, PCM monaural

‒Sampling clock: 192 kHz, 96 kHz, 48 kHz,

44.1 kHz, 32 kHz, etc.

●USB2.0 host interface (optional)

‒One port USB 2.0 (EHCI rev 1.0, OHCI)

‒Data transfer rate: 480 Mbps / 12 Mbps / 1.5 Mbps

‒Transmission mode: control, interrupt,

bulk, isochronous

●USB2.0 device interface (optional)

‒One port (exclusively used by Host / Device)

‒Data transfer rate: 480 Mbps / 12 Mbps / 1.5 Mbps

‒Transmission mode: control, interrupt,

bulk, isochronous

●10/100 Ethernet MAC

‒One Ethernet MAC channel for 10/100 Mbps

‒IEEE Standard 802.3,2000 Edition

‒Support full duplex/half duplex communication

‒RMII (10/100 Mbps) interface to Ethernet PHY device

‒IEEE802.3x flow control function

‒Support Jumbo Frame (up to 4 KB)

●eMMC / SD Card / SDIO interface

‒Two channels for 4-bit data width.

‒One channel for 8bit-data width.

‒Data transmission rate: 150 MHz (max)

‒Supported standard:

eMMC Ver. 4.5, SD Ver. 3.0, and SDIO Ver. 3.0 DS, HS, SDR12, SDR25, SDR50, SDR104 modes.

‒SD card control terminals

●SPI Flash Memory Controller interface

‒Chip select: 2-bit

‒Data bus width: Single, Dual or Quad mode interface

‒Data transmission rate: up to 50 MHz

‒Memory size: from 64 KB to 128 MB

●SPI interfaces (for master controller and transmission)

‒Seven channels for transmission or two for master controller can be selected.

Data transmission rate: up to 25 MHz

‒One channel for slave controller

Data transmission rate: up to 5 MHz

●External BUS interface

‒Data BUS width: 32 bits, 16 bits and 8 bits

- Coexistence is allowed.

‒Address BUS width: 27 bits

‒Memory capacity: up to 768 MB

‒Chip select: 4-bit

‒Asynchronous read/write, asynchronous page read, synchronous burst read/write.

‒Asynchronous boot devices are supported.

●UART interfaces

‒Four channels. One channel without flow control port.

‒Data transmission rate: up to 1.5 Mbps

‒Flow control ports

Compatible with UART 16550 data format Support external clock input.

Full duplex transmission mode and DMA transfer mode

●I2C bus interfaces

‒Four channels

‒Open drain output and Schmidt-trigger input

‒Support fast mode plus (up to 1000 kbps), Fast mode, Standard mode

‒A master (compatible with a multi-master) or a slave is selectable.

●Parallel port input interface

‒One channel

‒Data width: 8-bit

‒Data FIFO: 8-bit × 16-stage

●GPIO interface

‒Up to 128 channels

‒External inputs can be used as interrupt signals.

●AD converter inputs

‒Four input channels

‒12-bit successive AD converter

‒Sampling rate: up to 1.07 MHz

●PWM outputs

‒Six channels

‒Frequencies and duty ratios can be arbitrarily set.

List of Products

This table shows TZ2100 Series lineups. The following table shows the items which have a difference in specifications.

Product Number | Maximum CPU Operation Frequency (MHz) | Operating Temperature Range Ta (°C) | Internal Voltage Range (V) | Security service availability |

USB 2.0 Interface |

TZ2100XBG(O,2) | 300 | -40 to 85 | 1.00 to 1.20 | — | — |

TZ2100XBG(O,5) | 300 | -20 to 80 | 1.00 to 1.20 | — | Host / Device |

TZ2102XBG(O,3) | 600 | -20 to 80 | 1.06 to 1.21 | — | Host |

TZ2102XBG(O,6) | 600 | -40 to 85 | 1.10 to 1.20 | — | Host / Device |

TZ2101XBG(O,6) | 600 | -40 to 85 | 1.10 to 1.20 | Available | Host / Device |

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)