基于TMS320DM642/XC3S400AN/MT9V024/0V7960主控的360°可视全景泊车方案

333

333

拍明

拍明

原标题:360°可视全景泊车方案

方案介绍

目前,国内外尚未将三维成像技术成熟应用到监控产品上面,功能比较接近的产品是车辆智能全景监控系统。但它只能记录平面信息,不能全面地反映周围环境的具体情况。

今天为大家介绍的360度全景智能监控方案,正是在车辆智能全景监控系统发展而来的,是对车辆智能全景监控系统的改进。通过采用三维成像技术和语声混合算法,本系统一方面将周围物体的三维建模和尺度测量用3D技术来实现。另一方面,还将全部观测点的声音信息全部记录下来,使得记录的资料更加生动、形象和全面。

三维智能全景监控系统主要分为如下几部分:中央处理单元、显示与人机界面、专用摄像头(分布式安装)。

本系统的主体为中央处理单元,该部分主要包括:

(1)视频采集部件,采集系统所需视频,并将采集到的视频传送到视频合成部件。

(2)视频防抖部件,最大程度地预防在视频采集过程中的抖动,同时进行相应的视频补偿操作。

(3)视频合成部件,将采集到到视频内容进行无缝合成,形成全景视频,并输送到投影与映射单元。

(4)投影与映射部件,将合成的视频内容进行投影与映射,输出到相应的终端。

(5)目标检测部件,对周边的目标物体进行智能检测,按照预先设定的规则进行智能控制操作、综合障碍预警和多元导航信息等。

(6)GIS部件,对移动主体进行GIS定位功能。

选用的系统方案主要包括:

1.DSP核心处理器单元

2.FPGA协同处理器单元

3.图像采集单元(相机)

4.视频解码芯片

5.视频编码芯片

6.CAN模块

应用范围

1、中高档汽车。

2、工程机械。

3、港口船闸

4、水库大坝

5、金融场所

特色

TMS320C6000系列DSP选型及分析:

TMS320C6000系列DSP(Digital Signal Processor)n胡n¨是TI(TEXAS INSTRUMENTS)公司于1997年2月推向市场的高性能DSP,是目前在市场运用最广泛也是最成功的一款数字信号处理芯片之一,C6000系列DSP具有高性价比、功耗低等优点。

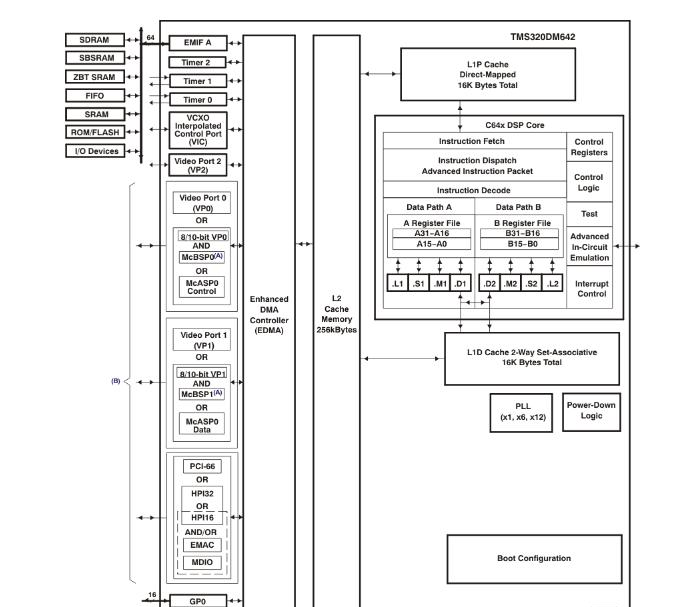

TMS320C6000系列包含两种类型的芯片分别为定点DSP和浮点DSP。TMS320DM642芯片是TI在2003年推出的一款32位定点数字信号处理器,是采用先进Veloci技术的VLIW构架,属于C6000系列DSP主要面向数字图像处理。

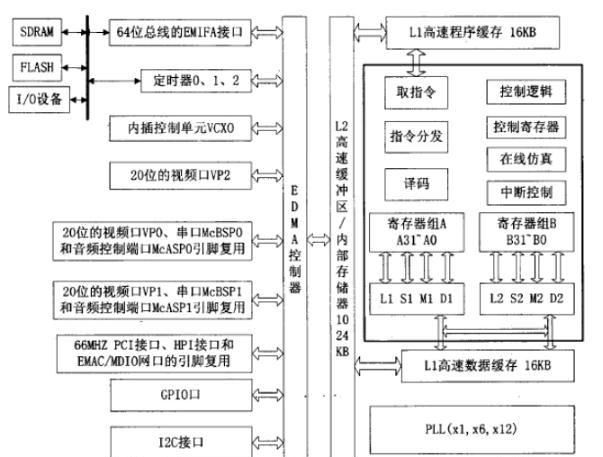

TMS320DM642处理器是在TMS320C6000平台上的高性能定点DSP。DM642是基于第二代高性能、先进Veloci TI技术的VLIW结构,这些特性使得此款DSP处理器被选为面向视频图像处理的最佳选择。DM642在理想状态下主频能达到720MHz,在此主频下处理速度能最高达到5760MIPS,C64x系列DSP内核有64个通用寄存器和8个独立的功能单元分别为2个乘法器和6个ALU。Veloci T11.2升级版,可以发挥功能单元的优势提升在实时图像处理方面的性能。DM642每个机器周期最多能提供4个16位多路累加运算(Multi—Accumulates.MAC),每秒可提供2880百万个MAC,或者8个8位MAC,每秒5760MMAC。DM642具有与其他类型DSP不同的硬件结构,与其他C6000系列DSP平台有相似的片上外设u 2|

FPGA的选型及分析:

Xilinx公司主要生产的FPGA有两大类型:一种是Spartan系列,另一种是Virtex系列,Spartan系列芯片主要针对中低端的消费电子应用领域,Virtex系列芯片主要应用于通信和网络终端等高端设备领域。

本方案选用的是拥有40万系统门数的Spartan一3AN系列XC3S400AN型号的芯片,所以着重介绍此款芯片的资源外设等相关信息n6|。

Spartan一3AN系列芯片为系统集成度非常高的非易失性FPGA,此款芯片有以下几项独特性能:FPGA有大量内部SRAM高性能资源、非易失性、缩小板卡空间和配置便捷等特点。

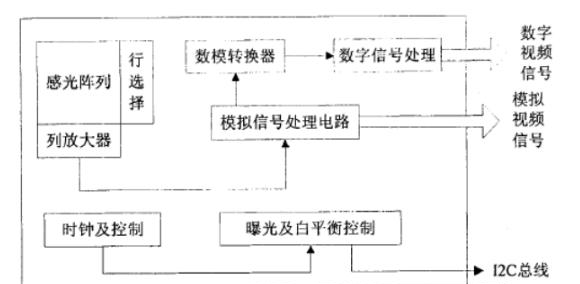

图像传感器的选型及分析

本方案的图像采集模块核心器件采用CMOS图像传感器,基于多图像传感器融合的全景泊车系统的构建需要4片图像传感器,由于本系统是主动安全驾驶辅助系统,对图像传感器的要求并不是太高,只要图像清晰、芯片适用于车载即可。

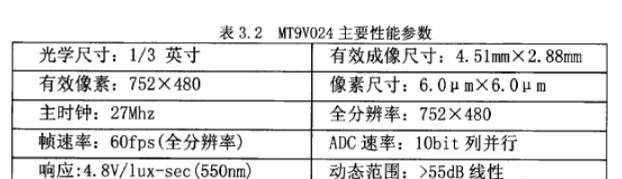

MT9V024图像传感器:MT9V024是像平面尺寸为1/3英寸、宽VGA模式的CMOS有源像素图像传感器,它采用TrueSNAP球形快门和高动态范围。该传感器专门为内外兼顾的汽车成像需求而设计,这使得它成为多种成像应用环境的理想芯片。

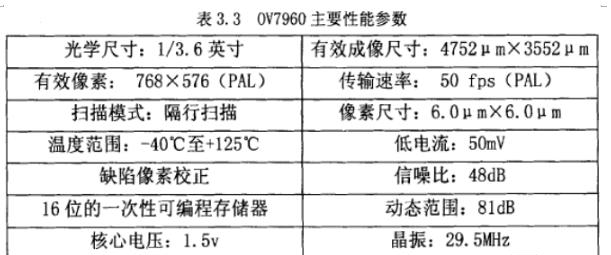

0V7960图像传感器:0V7960是OMNIVISION最近两年新推出的小尺寸图像传感器芯片,它的出现满足了汽车业对辅助驾驶系统应用要求(如倒车后视镜),开创了CMOS图像传感器在汽车安全辅助驾驶系统应用的新开端0V7960图像传感器的性能完全满足了汽车电子行业对图像传感器成像效果的特殊需求,1/4超小巧体积,在低光照下的也有良好的性能(<0.01LUX),并采用全球最小的CSP封装,体积比同类产品小50%,已经成为CMOS产品的领导者。

经过综合考虑本设计才用0V7960图像传感器作为相机的图像采集芯片。

相关电源电路设计请查看相关文档。

功能

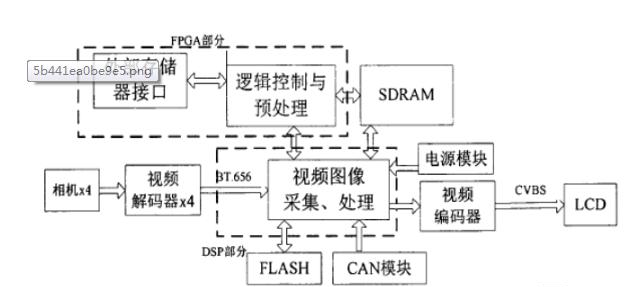

采用DSP作为本系统图像处理的核心处理器,FPGA作为协同处理器,充分发挥了两种不同处理器的各自优势。

FPGA主要负责整个系统的逻辑控制和视频图像的预处理,包括编/解码芯片的驱动、外部存储器的扩展和简单的图像预处理等,并预留有足够的逻辑资源空间以便以后复杂算法植入和功能扩展的需要。

DSP主要负责4路广角相机视频图像的采集、1路视频图像输出以及复杂图像处理算法的实现和接收CAN模块的信息。

系统方块图

核心器件

| 图片 | 数据手册 | 商品名称 | 产品型号 | 产品描述 | 品牌 |

|---|---|---|---|---|---|

| DSP(数字式信号处理器) | TMS320DM642AZNZ6 | IC FIXED-POINT DSP 548-FCBGA | TI | |

| FPGA(现场可编程门阵列) | XC3S400AN-4FGG400C | IC FPGA 311 I/O 400FBGA | Xilinx | |

| 电源管理芯片(PMIC) | TPS5430DDAR | IC REG BUCK ADJ 3A 8SOPWRPAD | TI |

相关文档

电源电路设计:

成功案例

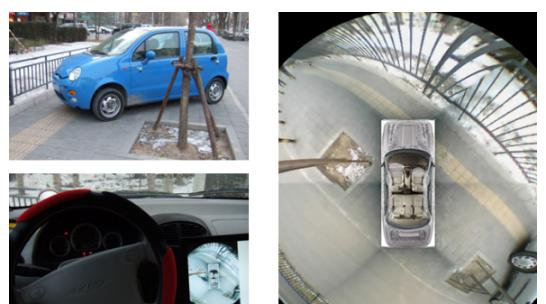

针对本系统在车辆的三维全景监控系统上进行了实践和应用。通过本系统进行视频合成虚拟出来的监控范围内有效区域的全景视图效果,并利用三维图像的形式进行显示,提供更加真实的虚拟现场。同时,本系统还可以实现关键部位的自动尺度测量,在必要的时候,主动进行报警。其效果演示图如下:

【TMS320DM642】

视频/成像定点数字信号处理器

描述

The TMS320C64x™ DSPs (including the TMS320DM642 device) are the highest-performance fixed-point DSP generation in the TMS320C6000™ DSP platform. The TMS320DM642 (DM642) device is based on the second-generation high-performance, advanced VelociTI™ very-long-instruction-word (VLIW) architecture (VelociTI.2™) developed by Texas Instruments (TI), making these DSPs an excellent choice for digital media applications. The C64x™ is a code-compatible member of the C6000™ DSP platform.

With performance of up to 5760 million instructions per second (MIPS) at a clock rate of 720 MHz, the DM642 device offers cost-effective solutions to high-performance DSP programming challenges. The DM642 DSP possesses the operational flexibility of high-speed controllers and the numerical capability of array processors. The C64x™ DSP core processor has 64 general-purpose registers of 32-bit word length and eight highly independent functional units-two multipliers for a 32-bit result and six arithmetic logic units (ALUs)- with VelociTI.2™ extensions. The VelociTI.2™ extensions in the eight functional units include new instructions to accelerate the performance in video and imaging applications and extend the parallelism of the VelociTI™ architecture. The DM642 can produce four 16-bit multiply-accumulates (MACs) per cycle for a total of 2880 million MACs per second (MMACS), or eight 8-bit MACs per cycle for a total of 5760 MMACS. The DM642 DSP also has application-specific hardware logic, on-chip memory, and additional on-chip peripherals similar to the other C6000™ DSP platform devices.

The DM642 uses a two-level cache-based architecture and has a powerful and diverse set of peripherals. The Level 1 program cache (L1P) is a 128-Kbit direct mapped cache and the Level 1 data cache (L1D) is a 128-Kbit 2-way set-associative cache. The Level 2 memory/cache (L2) consists of an 2-Mbit memory space that is shared between program and data space. L2 memory can be configured as mapped memory, cache, or combinations of the two. The peripheral set includes: three configurable video ports; a 10/100 Mb/s Ethernet MAC (EMAC); a management data input/output (MDIO) module; a VCXO interpolated control port (VIC); one multichannel buffered audio serial port (McASP0); an inter-integrated circuit (I2C) Bus module; two multichannel buffered serial ports (McBSPs); three 32-bit general-purpose timers; a user-configurable 16-bit or 32-bit host-port interface (HPI16/HPI32); a peripheral component interconnect (PCI); a 16-pin general-purpose input/output port (GP0) with programmable interrupt/event generation modes; and a 64-bit glueless external memory interface (EMIFA), which is capable of interfacing to synchronous and asynchronous memories and peripherals.

The DM642 device has three configurable video port peripherals (VP0, VP1, and VP2). These video port peripherals provide a glueless interface to common video decoder and encoder devices. The DM642 video port peripherals support multiple resolutions and video standards (e. g., CCIR601, ITU-BT.656, BT.1120, SMPTE 125M, 260M, 274M, and 296M).

These three video port peripherals are configurable and can support either video capture and/or video display modes. Each video port consists of two channels - A and B with a 5120-byte capture/display buffer that is splittable between the two channels.

For more details on the Video Port peripherals, see the TMS320C64x Video Port/VXCO Interpolated Control (VIC) Port Reference Guide (literature number SPRU629).

The McASP0 port supports one transmit and one receive clock zone, with eight serial data pins which can be individually allocated to any of the two zones. The serial port supports time-division multiplexing on each pin from 2 to 32 time slots. The DM642 has sufficient bandwidth to support all 8 serial data pins transmitting a 192-kHz stereo signal. Serial data in each zone may be transmitted and received on multiple serial data pins simultaneously and formatted in a multitude of variations on the Philips Inter-IC Sound (I2S) format.

In addition, the McASP0 transmitter may be programmed to output multiple S/PDIF, IEC60958, AES-3, CP-430 encoded data channels simultaneously, with a single RAM containing the full implementation of user data and channel status fields.

McASP0 also provides extensive error-checking and recovery features, such as the bad clock detection circuit for each high-frequency master clock which verifies that the master clock is within a programmed frequency range.

The VXCO interpolated control port (VIC) provides digital-to-analog conversion with resolution from 9-bits to up to 16-bits. The output of the VIC is a single bit interpolated D/A output. For more details on the VIC port, see the TMS320C64x Video Port/VXCO Interpolated Control (VIC) Port Reference Guide (literature number SPRU629).

The ethernet media access controller (EMAC) provides an efficient interface between the DM642 DSP core processor and the network. The DM642 EMAC support both 10Base-T and 100Base-TX, or 10 Mbits/second (Mbps) and 100 Mbps in either half- or full-duplex, with hardware flow control and quality of service (QOS) support. The DM642 EMAC makes use of a custom interface to the DSP core that allows efficient data transmission and reception. For more details on the EMAC, see the TMS320C6000 DSP Ethernet Media Access Controller (EMAC) / Management Data Input/Output (MDIO) Module Reference Guide (literature number SPRU628).

The management data input/output (MDIO) module continuously polls all 32 MDIO addresses in order to enumerate all PHY devices in the system. Once a PHY candidate has been selected by the DSP, the MDIO module transparently monitors its link state by reading the PHY status register. Link change events are stored in the MDIO module and can optionally interrupt the DSP, allowing the DSP to poll the link status of the device without continuously performing costly MDIO accesses. For more details on the MDIO, see the TMS320C6000 DSP Ethernet Media Access Controller (EMAC) / Management Data Input/Output (MDIO) Module Reference Guide (literature number SPRU628).

The I2C0 port on the TMS320DM642 allows the DSP to easily control peripheral devices, boot from a serial EEPROM, and communicate with a host processor. In addition, the standard multichannel buffered serial port (McBSP) may be used to communicate with serial peripheral interface (SPI) mode peripheral devices.

特性

High-Performance Digital Media Processor (TMS320DM642)

2-, 1.67-, 1.39-ns Instruction Cycle Time

500-, 600-, 720-MHz Clock Rate

Eight 32-Bit Instructions/Cycle

4000, 4800, 5760 MIPS

Fully Software-Compatible With C64x™

VelociTI.2™ Extensions to VelociTI™ Advanced Very-Long-Instruction-Word VLIW) TMS320C64x™ DSP Core

Eight Highly Independent Functional Units With VelociTI.2™ Extensions:

Six ALUs (32-/40-Bit), Each Supports Single 32-Bit, Dual 16-Bit, or Quad 8-Bit Arithmetic per Clock Cycle

Two Multipliers Support Four 16 x 16-Bit Multiplies (32-Bit Results) per Clock Cycle or Eight 8 x 8-Bit Multiplies (16-Bit Results) per Clock Cycle

Load-Store Architecture With Non-Aligned Support

64 32-Bit General-Purpose Registers

Instruction Packing Reduces Code Size

All Instructions Conditional

Instruction Set Features

Byte-Addressable (8-/16-/32-/64-Bit Data)

8-Bit Overflow Protection

Bit-Field Extract, Set, Clear

Normalization, Saturation, Bit-Counting

VelociTI.2™ Increased Orthogonality

L1/L2 Memory Architecture

128K-Bit (16K-Byte) L1P Program Cache (Direct Mapped)

128K-Bit (16K-Byte) L1D Data Cache (2-Way Set-Associative)

2M-Bit (256K-Byte) L2 Unified Mapped RAM/Cache (Flexible RAM/Cache Allocation)

Endianess: Little Endian, Big Endian

64-Bit External Memory Interface (EMIF)

Glueless Interface to Asynchronous Memories (SRAM and EPROM) and Synchronous Memories (SDRAM, SBSRAM, ZBT SRAM, and FIFO)

1024M-Byte Total Addressable External Memory Space

Enhanced Direct-Memory-Access (EDMA) Controller (64 Independent Channels)

10/100 Mb/s Ethernet MAC (EMAC)

IEEE 802.3 Compliant

Media Independent Interface (MII)

8 Independent Transmit (TX) Channels and 1 Receive (RX) Channel

Management Data Input/Output (MDIO)

Three Configurable Video Ports

Providing a Glueless I/F to Common Video Decoder and Encoder Devices

Supports Multiple Resolutions and Video Standards

VCXO Interpolated Control Port (VIC)

Supports Audio/Video Synchronization

Host-Port Interface (HPI) [32-/16-Bit]

32-Bit/66-MHz, 3.3-V Peripheral Component Interconnect (PCI) Master/Slave Interface Conforms to PCI Specification 2.2

Multichannel Audio Serial Port (McASP)

Eight Serial Data Pins

Wide Variety of I2S and Similar Bit Stream Format

Integrated Digital Audio I/F Transmitter Supports S/PDIF, IEC60958-1, AES-3, CP-430 Formats

Inter-Integrated Circuit (I2C) Bus™

Two Multichannel Buffered Serial Ports

Three 32-Bit General-Purpose Timers

Sixteen General-Purpose I/O (GPIO) Pins

Flexible PLL Clock Generator

IEEE-1149.1 (JTAG) Boundary-Scan-Compatible

548-Pin Ball Grid Array (BGA) Package (GDK and ZDK Suffixes), 0.8-mm Ball Pitch

548-Pin Ball Grid Array (BGA) Package (GNZ and ZNZ Suffixes), 1.0-mm Ball Pitch

0.13-µm/6-Level Cu Metal Process (CMOS)

3.3-V I/O, 1.2-V Internal (-500)

3.3-V I/O, 1.4-V Internal (A-500, A-600, -600, -720)

C64x, VelociTI.2, VelociTI, and TMS320C64x are trademarks of Texas Instruments.

All trademarks are the property of their respective owners.

TMS320C6000, and C6000 are trademarks of Texas Instruments.

Windows is a registered trademark of the Microsoft Corporation.

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)