基于ADI公司的AD9208双路14位3GSPS取样ADC评估方案

283

283

拍明

拍明

原标题:ADI AD9208双路14位3GSPS取样ADC评估方案

ADI公司的AD9208是双路14位3GSPS取样的模数转换器(ADC),具有低功耗小尺寸和容易使用等特点,宽输入-3dB带宽9GHz,取样模拟信号高达5GHz,噪音密度−152 dBFS/Hz,工作电压0.975 V, 1.9 V和2.5 V dc,双ADC核具有多级差分流水线型架构,ADC数据输出直接连接到四个数字下转换器(DDC),主要用在仪器仪表和测量,频谱/信号和网络分析,数据采集,电子测试和测量,通信和无线基础设施,宽带RF信号处理,软件定义无线电和航空航天和防务以及雷达等.本文介绍了AD9208产品亮点和主要特性,功能框图,以及评估板AD9208-3000EBZ主要特性,电路图和材料清单.

The AD9208 is a dual, 14-bit, 3 GSPS analog-to-digital converter (ADC). The device has an on-chip buffer and a sample-and- hold circuit designed for low power, small size, and ease of use. This product is designed to support communications applications capable of direct sampling wide bandwidth analog signals of up to 5 GHz. The −3 dB bandwidth of the ADC input is 9 GHz. The AD9208 is optimized for wide input bandwidth, high sampling rate, excellent linearity, and low power in a small package. The dual ADC cores feature a multistage, differential pipelined architecture with integrated output error correction logic. Each ADC features wide bandwidth inputs supporting a variety of user-selectable input ranges. An integrated voltage reference eases design considerations. The analog input and clock signals are differential inputs. The ADC data outputs are internally connected to four digital downconverters (DDCs) through a crossbar mux. Each DDC consists of up to five cascaded signal processing stages: a 48-bit frequency translator (numerically controlled oscillator (NCO)), and up to four half-band decimation filters. The NCO has the option to select preset bands over the general-purpose input/output (GPIO) pins, which enables the selection of up to three bands. Operation of the AD9208 between the DDC modes is selectable via SPI-programmable profiles. In addition to the DDC blocks, the AD9208 has several functions that simplify the automatic gain control (AGC) function in a communications receiver. The programmable threshold detector allows monitoring of the incoming signal power using the fast detect control bits in Register 0x0245 of the ADC. If the input signal level exceeds the programmable threshold, the fast detect indicator goes high. Because this threshold indicator has low latency, the user can quickly turn down the system gain to avoid an overrange condition at the ADC input. In addition to the fast detect outputs, the AD9208 also offers signal monitoringcapability. The signal monitoring block provides additional information about the signal being digitized by the ADC. The user can configure the Subclasss 1 JESD204B-based high speed serialized output in a variety of one-lane, two-lane, four- lane, and eight-lane configurations, depending on the DDC configuration and the acceptable lane rate of the receiving logic device. Multidevice synchronization is supported through the SYSREF± and SYNCINB± input pins. The AD9208 has flexible power-down options that allow significant power savings when desired. All of these features can be programmed using a 3-wire serial port interface (SPI). The AD9208 is available in a Pb-free, 196-ball BGA, specified over the −40°C to +85°C ambient temperature range. This product is protected by a U.S. patent. Note that throughout this data sheet, multifunction pins, such as FD_A/GPIO_A0, are referred to either by the entire pin name or by a single function of the pin, for example, FD_A, when only that function is relevant.

AD9208产品亮点:

1. Wide, input −3 dB bandwidth of 9 GHz supports direct radio frequency (RF) sampling of signals up to about 5 GHz.

2. Four integrated, wideband decimation filter and NCO blocks supporting multiband receivers.

3. Fast NCO switching enabled through the GPIO pins.

4. A SPI controls various product features and functions to meet specific system requirements.

5. Programmable fast overrange detection and signal monitoring.

6. On-chip temperature diode for system thermal management.

7. 12 mm × 12 mm, 196-ball BGA.

AD9208主要特性:

JESD204B (Subclass 1) coded serial digital outputs

Support for lane rates up to 16 Gbps per lane

1.65 W total power per channel at 3 GSPS (default settings)

Performance at −2 dBFS amplitude, 2.6 GHz input

SFDR = 70 dBFS

SNR = 57.2 dBFS

Performance at −9 dBFS amplitude, 2.6 GHz input

SFDR = 78 dBFS

SNR = 59.5 dBFS

Integrated input buffer

Noise density = −152 dBFS/Hz

0.975 V, 1.9 V, and 2.5 V dc supply operation

9 GHz analog input full power bandwidth (−3 dB)

Amplitude detect bits for efficient AGC implementation

2 integrated, wideband digital processors per channel

48-bit NCO

4 cascaded half-band filters

Phase coherent NCO switching

Up to 4 channels available

Serial port control

Integer clock with divide by 2 and divide by 4 options

Flexible JESD204B lane configurations

On-chip dither

AD9208应用:

Diversity multiband and multimode digital receivers

3G/4G, TD-SCDMA, W-CDMA, and GSM, LTE, LTE-A

Electronic test and measurement systems

Phased array radar and electronic warfare

DOCSIS 3.0 CMTS upstream receive paths

HFC digital reverse path receivers

图1. AD9208功能框图

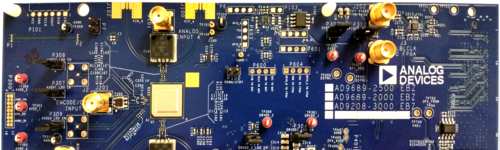

评估板AD9208-3000EBZ

This user guide describes the AD9208-3000EBZ evaluation board which provides all of the support circuitry required to operate the ADC in its various modes and configurations. This guide entails both the hardware and software setup needed to acquire data capture from the evaluation board. This guide assumes the usage of the accompanying ADS7-V2 EBZ High Speed Evaluation Board. The user guide for the ADS7-V2 provides additional information available for consultation during usage. Documents and software tools, where available, can be found at the HS-ADC Eval Board homepage.

The AD9208-3000EBZ supports the AD9208-3000, a 14-bit, 3GSPS dual analog-to-digital converter (ADC). The device has an on-chip buffer and a sample-and-hold circuit designed for low power, small size, and ease of use. This device is designed support direct RF sampling analog signals of up to 5 GHz. The 3 dB bandwidth of the ADC input is greater than 9 GHz. The AD9208 is optimized for wide input bandwidth, high sampling rate, excellent linearity, and low power in a small package.

This reference design provides all of the support circuitry required to operate the ADC in its various modes and configurations. It is designed to interface directly with the ADS7-V2EBZ data capture card, allowing users to download captured data for analysis. The device control and subsequent data analyses can now be done using the ACE software package.

图2.评估板AD9208-3000EBZ外形图(正面)

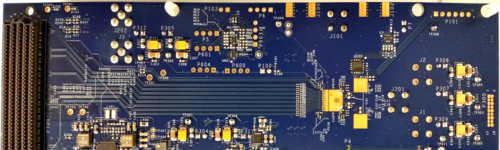

图3.评估板AD9208-3000EBZ外形图(背面)

评估板AD9208-3000EBZ主要特性:

Full featured evaluation board for the AD9208-3000EBZ.

JESD204B coded serial digital outputs with support for lane rates up to 16Gbps/lane.

Wide full power bandwidth supports IF sampling of signals up to 9GHz (-3dB point).

Four Integrated wide-band decimation filter and NCO blocks supporting multi-band receivers.

Fast NCO switching enabled through GPIO pins.

Flexible SPI interface controls various product features and functions to meet specific system requirements.

Programmable fast over range detection and signal monitoring.

On-chip temperature diode for system thermal management.

评估板AD9208-3000EBZ材料清单见:

详情请见:

责任编辑:HanFeng

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)