STM32G0B0CET6的usb的时钟只能用48MHz的晶振来实现吗?

7

7

拍明芯城

拍明芯城

STM32G0B0CET6 USB时钟源解析:为何48MHz晶振是优选,兼谈元器件选型与原理

在嵌入式系统设计中,USB(通用串行总线)作为一种高速、灵活的通信接口,其稳定可靠的工作至关重要。对于STM32G0B0CET6这款微控制器而言,USB模块的时钟源配置是确保其正常工作、达到USB全速(Full-Speed)或低速(Low-Speed)通信规范的关键。许多开发者在面对USB时钟源的选择时,往往会有一个疑问:STM32G0B0CET6的USB时钟是否只能通过48MHz的晶振来实现?答案并非绝对“只能”,但从性能、稳定性和兼容性角度考虑,48MHz晶振无疑是最优选,并且在绝大多数应用场景下都是推荐且实际使用的方案。

要理解为何48MHz晶振如此重要,我们首先需要深入剖析STM32G0B0CET6的USB时钟需求、其内部时钟树结构以及不同时钟源的优缺点。

STM32G0B0CET6 USB时钟需求与内部时钟树概览

USB全速通信要求一个精确的48MHz时钟源来驱动其PHY(物理层)和SIE(串行接口引擎)。这个48MHz时钟用于生成USB数据传输所需的同步信号、NRZI编码(Non-Return-to-Zero, Invert)、位填充(Bit Stuffing)等关键操作。USB通信对时钟的精度要求非常高,通常要求在±0.25%以内,以确保数据传输的完整性和可靠性。任何时钟的漂移或抖动都可能导致通信错误甚至连接中断。

STM32G0B0CET6内部拥有一个复杂而灵活的时钟树系统,它允许从多种时钟源生成各种系统时钟和外设时钟。USB模块的时钟源(USBCLK)可以从以下几个主要途径获取:

HSI48 (High-Speed Internal 48MHz Oscillator):这是一个内部RC振荡器,标称频率为48MHz。

PLL (Phase-Locked Loop):PLL可以作为时钟倍频器,将低频时钟源(如HSE外部高速晶振或HSI内部高速RC振荡器)倍频到所需的频率。对于USB,PLL的输出可以配置为48MHz。

HSE (High-Speed External Oscillator):一个外部晶体或陶瓷谐振器,通常用于提供高精度的主时钟源。如果使用HSE,它通常会作为PLL的输入,然后PLL输出48MHz供给USB。

理想情况下,无论采用哪种方式,最终提供给USB模块的时钟频率都必须是48MHz,并且满足USB规范对精度的严苛要求。

为何48MHz晶振是优选:精度、稳定性与兼容性

尽管STM32G0B0CET6提供了多种生成48MHz时钟的途径,但直接或间接通过**48MHz外部晶振(HSE)**来提供USB时钟(通常是通过PLL倍频或直接作为PLL输入,PLL输出48MHz)被认为是最佳实践,主要基于以下几个核心原因:

1. 卓越的时钟精度与稳定性

外部晶振,特别是石英晶体谐振器,因其固有的物理特性,能够提供比内部RC振荡器(如HSI48)高得多的频率精度和稳定性。

内部HSI48的局限性:尽管STM32G0B0CET6集成了HSI48,专门为USB设计,但在实际应用中,内部RC振荡器的频率会受到多种因素的影响,例如温度、电源电压变化和芯片制造工艺偏差。这些因素会导致HSI48的频率在宽温度范围内或不同批次芯片之间存在较大的漂移。虽然数据手册会给出HSI48的精度范围(例如,±1%),但这通常不足以满足USB全速通信±0.25%的严格要求。如果使用精度不足的时钟源,USB通信的数据包可能会因为时序误差而丢失,导致通信失败或数据损坏。

外部晶振的优势:高质量的外部48MHz晶振,其初始频率精度通常在±20 ppm(百万分之一)到±100 ppm之间,并且其频率随温度变化的漂移特性也远优于内部RC振荡器。例如,一个典型的48MHz晶振在整个工作温度范围内的总频率误差可以轻松保持在±0.1%以内,这远超USB规范的最低要求。这种高精度和高稳定性是确保USB通信长期可靠性的基石。

2. 抗干扰能力强

外部晶振通常与一个精确的负载电容网络配合使用,形成一个稳定的振荡电路。相比之下,内部RC振荡器更容易受到芯片内部噪声和外部电磁干扰(EMI)的影响,从而导致频率抖动。在复杂的电磁环境中,外部晶振能够提供更“纯净”的时钟信号,降低USB通信受干扰的风险。

3. 兼容性与互操作性

USB是一个全球性的标准,为了确保不同制造商的设备能够无缝连接和通信,所有USB设备都必须严格遵守其时序规范。使用高精度的外部晶振,能够最大限度地保证STM32G0B0CET6作为USB设备或主机时,其时序特性与USB标准完全兼容。如果时钟精度不足,可能会出现兼容性问题,例如在某些主机或设备上无法识别,或者在长时间通信后出现错误。

4. 启动与唤醒可靠性

对于需要USB唤醒功能的低功耗应用,晶振的快速启动和稳定工作能力也十分重要。虽然某些内部振荡器也支持低功耗模式下的快速唤醒,但晶振的长期稳定性在这些应用中更具优势。

小结

综上所述,虽然STM32G0B0CET6的USB模块在理论上可以通过HSI48或PLL(以HSI作为输入)获得48MHz时钟,但为了达到USB全速通信所需的±0.25%高精度和稳定性要求,外部48MHz晶振(通常作为HSE,然后通过PLL倍频到48MHz)是几乎唯一可靠的选择。 在实际产品开发中,为了避免USB通信故障和兼容性问题,工程师们普遍会选择外部晶振作为USB时钟的来源。

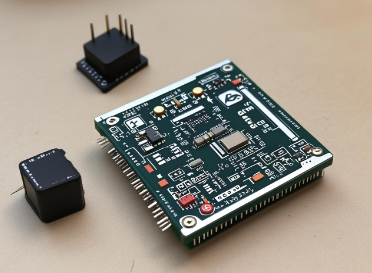

优选元器件型号:48MHz晶振及相关匹配元件

为了实现稳定可靠的USB功能,除了选择高质量的STM32G0B0CET6微控制器外,对其USB时钟源相关的外部元器件的选择同样至关重要。这里我们将详细探讨48MHz晶振及其配套元件的选择。

1. 48MHz晶振 (Crystal Oscillator)

作用: 提供高精度的48MHz基准频率。它是USB时钟链的源头,其精度和稳定性直接决定了USB通信的质量。

为何选择: 如前所述,相比内部RC振荡器,外部晶振具有更高的频率精度、更低的温度漂移和更好的长期稳定性,能够满足USB ±0.25%的严格时钟精度要求。

优选元器件型号示例:

标称频率 (Nominal Frequency): 48.000MHz。

频率稳定度 (Frequency Stability): 在整个工作温度范围内的最大频率偏差,通常表示为ppm或百分比。对于USB,建议选择±50 ppm甚至更低的晶振。

等效串联电阻 (ESR): 晶振的内部损耗,ESR越低越好,通常在几十欧姆到几百欧姆之间。低ESR有助于晶振更容易起振并降低功耗。

负载电容 (Load Capacitance): 晶振设计时指定的外部电容值,通常为8pF, 10pF, 12pF, 18pF等。这需要与微控制器内部或外部的匹配电容相匹配,以确保晶振在正确的频率下振荡。

封装类型 (Package Type): SMD(表面贴装器件)是主流,如3225 (3.2mm x 2.5mm), 2520 (2.5mm x 2.0mm) 甚至更小的1612 (1.6mm x 1.2mm),具体取决于PCB空间限制。

工作温度范围 (Operating Temperature Range): 根据产品应用环境选择,例如消费级(0∘C to +70∘C),工业级(−40∘C to +85∘C)或汽车级(−40∘C to +125∘C)。

ECS-200-20-4X-TR: 同样是一款常见的48MHz贴片晶振,其性能参数与TXC类似,也是市场上广泛使用的选择。

特点: 性价比高,尺寸紧凑,适合小型化设计。

8U-48.000MBA-T: 这是一款常用的48MHz贴片晶振,通常采用SMD封装(例如3.2mm x 2.5mm或2.5mm x 2.0mm),具有良好的频率稳定性和ESR(等效串联电阻)特性。TXC是知名的晶振制造商,产品质量可靠,供货稳定。

特点: 频率稳定度通常在±10 ppm至±30 ppm之间,工作温度范围广,适用于工业级应用。

TXC (台湾晶技):

ECS (ECS Inc. International):

Kyocera (京瓷), Epson (爱普生), Murata (村田): 这些也都是全球领先的晶振制造商,提供各种规格和封装的48MHz晶振。在选择时,应关注以下关键参数:

2. 晶振匹配电容 (Load Capacitors)

作用: 这些电容与晶振一起形成一个谐振电路,确保晶振在正确的频率下稳定振荡。它们通常连接在晶振的两个引脚与地之间。

为何选择:

确保精确频率: 晶振需要一个特定的负载电容才能在其标称频率下工作。负载电容不匹配会导致频率漂移,从而影响USB通信的可靠性。

优化起振特性: 适当的匹配电容有助于晶振电路快速稳定起振,并降低功耗。

抑制噪声: 它们还能对晶振引脚上的噪声起到一定的滤波作用。

优选元器件型号示例:

常见型号: GRM系列、CL系列、C系列等贴片陶瓷电容。

具体数值: 通常选择10pF至33pF之间的NPO/C0G特性陶瓷电容。实际值需要根据所选晶振的负载电容(CL)值和PCB寄生电容来精确计算。STM32的数据手册通常会给出推荐值或计算公式。

电容特性: 务必选择NPO/C0G介质的陶瓷电容。这种类型的电容具有极低的温度系数和电压系数,这意味着其容值受温度和电压变化的影响极小,能够提供稳定的负载电容,从而保证晶振频率的稳定性。相比之下,X7R、X5R等介质的电容虽然容量大,但其容值会随温度和电压变化而显著漂移,不适用于晶振匹配电路。

额定电压: 选择至少16V或更高额定电压的电容,以确保可靠性。

封装: 常见的有0402、0603等贴片封装。

Murata (村田), Samsung Electro-Mechanics (三星电机), TDK, Yageo (国巨):

负载电容计算: STM32微控制器的外部晶振振荡电路通常是一个并联谐振电路。晶振的负载电容CL由外部两个匹配电容C1、C2和微控制器内部引脚的寄生电容C_pin共同决定。理想情况下,晶振的负载电容CL应该等于: CL=(C1+C2)(C1×C2)+Cpin 由于STM32的晶振引脚设计通常是对称的,可以假设C1 = C2 = C_Lext。此时公式简化为: CL=2CLext+Cpin 因此,外部匹配电容C_Lext的值为: CLext=2×(CL−Cpin) 其中,Cpin的值可以参考STM32G0B0CET6的数据手册或应用笔记,通常为几pF。实际调试时,可能需要微调C1和C2的值以达到最佳频率和稳定性。

3. 去耦电容 (Decoupling Capacitors)

作用: 去耦电容放置在微控制器的电源引脚附近,用于滤除电源噪声,提供稳定的局部电源,并抑制高频干扰。

为何选择:

保证电源纯净: 晶振振荡电路对电源噪声非常敏感。纯净的电源能够确保晶振稳定工作,避免电源纹波引起频率抖动。

提高EMC性能: 有助于吸收芯片高速开关产生的瞬态电流,降低电磁辐射,提高系统的电磁兼容性(EMC)。

优选元器件型号示例:

常见型号: GRM系列、CL系列等贴片陶瓷电容。

具体数值: 多个不同容值的电容并联使用效果最佳。通常选用一个0.1$mu$F (100nF)的电容与一个1$mu$F(或更高,例如10$mu$F)的电容并联,并尽可能靠近STM32的电源引脚。

电容特性: 对于去耦电容,可以选择X7R或X5R介质的陶瓷电容,它们在容值和尺寸上更具优势。

额定电压: 至少16V或更高。

封装: 0402、0603或0805。

Murata (村田), Samsung Electro-Mechanics (三星电机), TDK, Yageo (国巨):

4. 串联电阻 (Damping Resistor - 可选)

作用: 有时会在晶振的输出端(通常是OSC_OUT或OSC_IN引脚,具体取决于微控制器设计)串联一个几十欧姆的电阻(例如22$Omega$ - 100$Omega$)。

为何选择:

限制振荡电流: 保护晶振免受过大激励功率的损坏,延长晶振寿命。

抑制高次谐波: 有助于抑制晶振在基频之外的高次谐波振荡,使波形更纯净。

改善EMC性能: 降低由高速开关引起的EMI。

优选元器件型号示例:

任何常规的贴片电阻: 例如Yageo (国巨), Rohm (罗姆), Panasonic (松下) 等制造商的0603或0402封装的普通贴片电阻。

具体数值: 通常在22$Omega$到100$Omega$之间,具体数值可以参考STM32的数据手册或相关应用笔记,或通过示波器观察晶振波形来确定最佳值。并非所有设计都必须包含此电阻,但对于追求更高稳定性和EMC性能的应用,这是一个值得考虑的选项。

STM32G0B0CET6内部时钟配置与USB时钟路径

理解了外部元器件的选择,接下来需要了解STM32G0B0CET6内部是如何配置和使用这些时钟源的。STM32G0B0CET6的时钟系统非常灵活,可以通过寄存器配置(或使用STM32CubeMX工具)来选择USB时钟源。

对于USB模块,其时钟源通常可以配置为:

HSE_DIV (HSE分频后直接或间接供给): 如果外部HSE晶振是48MHz,可以直接作为USB时钟源(这在STM32的某些系列中可行,但对于G0系列,通常需要经过PLL)。

PLLCLK_Q (PLL的Q路输出): 这是最常见和推荐的方式。通过将HSE(外部晶振)或HSI(内部RC振荡器)作为PLL的输入,然后通过PLL的倍频和分频器设置,将PLL的Q路输出配置为精确的48MHz。

HSI48 (内部48MHz RC振荡器): 仅在对USB时钟精度要求不高的调试或非关键应用中考虑,不推荐用于量产产品。

典型且推荐的USB时钟配置路径为:

外部HSE晶振 (例如8MHz或16MHz) → PLL输入 → PLL倍频至48MHz → PLLCLK_Q输出 → USB模块时钟源

或更直接的:

外部48MHz HSE晶振 → PLL输入 (直接或经过分频) → PLL倍频至48MHz → PLLCLK_Q输出 → USB模块时钟源

为什么通常选择通过PLL来生成USB 48MHz,而不是直接使用48MHz HSE?

虽然理论上可以直接使用48MHz HSE作为USB时钟(如果MCU支持且没有其他外设需要更高频率),但在STM32的设计中,通常会通过PLL来生成USB的48MHz。主要原因如下:

频率灵活性: 主系统时钟(SYSCLK)通常需要更高的频率(例如64MHz),而USB只需要48MHz。通过PLL,可以使用一个相对较低频率的HSE晶振(例如8MHz或16MHz)作为主时钟源,通过PLL同时生成高频的SYSCLK和精确的48MHz USBCLK,从而简化外部晶振的选择。

时钟树的统一性: PLL是STM32时钟树的核心,它能从一个或少数几个晶振源生成所有必要的时钟频率。将USB时钟集成到PLL的输出中,使得整个时钟管理更加统一和高效。

抖动抑制: 某些PLL设计具有一定的抖动抑制能力,可以进一步提高USB时钟的质量。

设计考虑与布局布线注意事项

除了选择合适的元器件,正确的PCB布局布线对于确保USB时钟的稳定性和信号完整性也至关重要。

1. 晶振布局

靠近MCU: 晶振应尽可能靠近STM32G0B0CET6的OSC_IN和OSC_OUT引脚。距离越短,引线寄生电感和电容越小,越有利于晶振稳定振荡和降低噪声。

独立接地层: 晶振的接地(包括匹配电容的接地)应该尽可能连接到MCU的独立模拟地平面,或至少是噪声最小的数字地平面。避免与其他高电流回路共享地线,以防止地弹噪声干扰。

隔离: 晶振电路应远离高频、大电流的走线和噪声源(如开关电源、大功率数字信号线),以减少电磁干扰。可以在晶振周围使用铺铜屏蔽。

对称性: 连接晶振和匹配电容的走线长度应尽可能对称,以确保两个引脚上的负载平衡。

2. 匹配电容布局

紧邻晶振引脚: 两个匹配电容应紧密放置在晶振的两个引脚旁边,并直接连接到地。

最短路径: 连接晶振和电容的走线应尽可能短而宽,以降低阻抗和寄生效应。

3. 去耦电容布局

靠近电源引脚: 去耦电容应紧密放置在STM32G0B0CET6的VCC和GND电源引脚旁边。

不同容值并联: 如前所述,通常会使用0.1$mu$F和1$mu$F(或更大)的电容并联,小容量电容滤除高频噪声,大容量电容提供瞬态电流。小容量电容应更靠近引脚。

低ESL/ESR: 选择低等效串联电感(ESL)和低等效串联电阻(ESR)的陶瓷电容,以提高去耦效果。

4. USB差分信号线

差分走线: USB_DP和USB_DM线必须进行差分走线,走线长度匹配,线宽和间距要严格控制,以满足90$Omega$(USB全速)或90$Omega$(USB高速)的差分阻抗要求。

远离噪声源: 差分线应远离其他高频数字信号和电源线。

完整地平面: USB差分线下方应有完整连续的参考地平面,以提供回流路径和屏蔽作用。

ESD保护: USB接口是容易受到静电放电(ESD)影响的区域。务必在USB数据线和电源线上增加ESD保护器件,例如瞬态电压抑制器(TVS)二极管阵列。

Littelfuse (力特): SP0503BAHT, SP1003-01ETG

STMicroelectronics (意法半导体): USBLC6-2SC6, ESDAVLC8-1BV2

Nexperia (安世半导体): PRTR5V0U2X, PESD5V0U1BL

功能: 这些器件能够在发生ESD事件时,将瞬态高压钳位到安全水平,保护STM32的USB引脚免受损坏。选择具有低钳位电压、低结电容(尤其是对于USB2.0高速信号)和快速响应时间的型号。对于USB全速,结电容一般不应超过5pF。

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)