基于16位20Msps LTC2270实现连接到高性能流水线adc的设计方案

108

108

拍明芯城

拍明芯城

高速adc使用由快速CMOS开关和采样电容组成的采样和保持输入结构。当CMOS开关闭合时,采样电容与前面的驱动电路共享其存储的电荷(电荷反打)。随着采样电容及其存储电荷的增大,驱动电路必须受到更多的关注。

流水线adc通常具有几个皮级的样品电容。相比之下,高性能16位20Msps LTC2270高速ADC使用17pf采样电容。相对较大的采样电容的优点是可以显著降低内部t /C噪声,从而获得更好的信噪比(SNR)。缺点是该部件变得更加难以驱动。每次CMOS开关闭合时,采样电容向驱动器回踢的电荷明显多于较小的采样电容。

驱动和ADC之间的接口滤波器需要特别注意。不合适的滤波器会影响信噪比和SFDR。该滤波器必须限制噪声,并充分解决电荷反流,以保护驱动器和ADC免受反射。本设计说明了如何为LTC2270设计合适的驱动器和10mhz接口滤波器。

司机选择

LTC2270具有84.1dB信噪比(46 μ VRMSinput参考噪声),基带SFDR为99dB。为了确保ltc2270的性能达到最佳,ADC驱动器必须能够承受较大的电荷反流,驱动相对较重的负载,并且具有较低的宽带噪声。

ADC输入端的共模终止是维持ADC低失真所必需的,这会给驱动器带来很大的负载。此外,司机必须极低的噪音。作为参考点,一个3nV/√赫兹在10MHz带宽上的放大器将使信噪比下降超过1dB。LTC6409是满足这些要求的一个很好的选择。它提供驱动和输出摆幅,以允许足够的共模终止和1.1nV/√的输入参考电压噪声赫兹.

滤波器的设计

高频流水线adc数字化了巨大的信息带宽。LTC2270具有200MHz的全功率带宽,使其能够数字化20Nyquist区域并集成宽带噪声失真,时钟频率和其他低频伪影。

接口滤波器限制了来自驱动器的宽带噪声,但如果不仔细设计,滤波器也会恶化SFDR。为了获得驱动器和ADC的最佳sfdr规格,请从这些广泛的指导方针开始:

ADC的输入阻抗应该很低。由于采样主要是一个共模效应,这个终止应该是共模的。

驱动器应该看到相对较高的阻抗,特别是当驱动ADC到满量程时。

具有吸收性(从不打开或短)特性的过滤器性能更好。

共模终端电容减轻了电荷反流对驱动器和ADC的影响。一个包含共模终止和适当解决电荷反流的滤波器将优化SFDR。

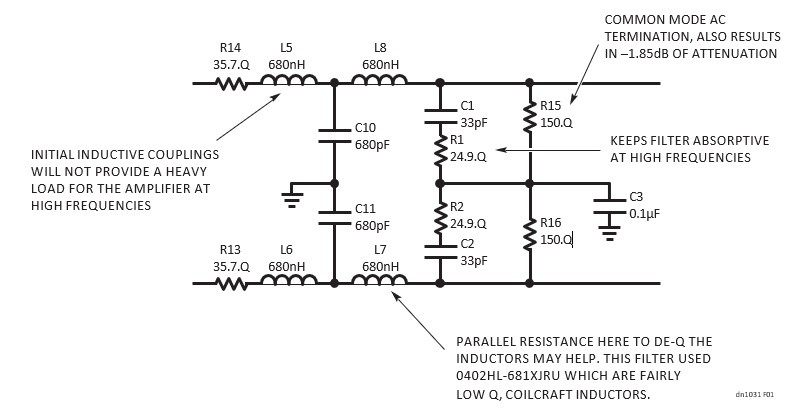

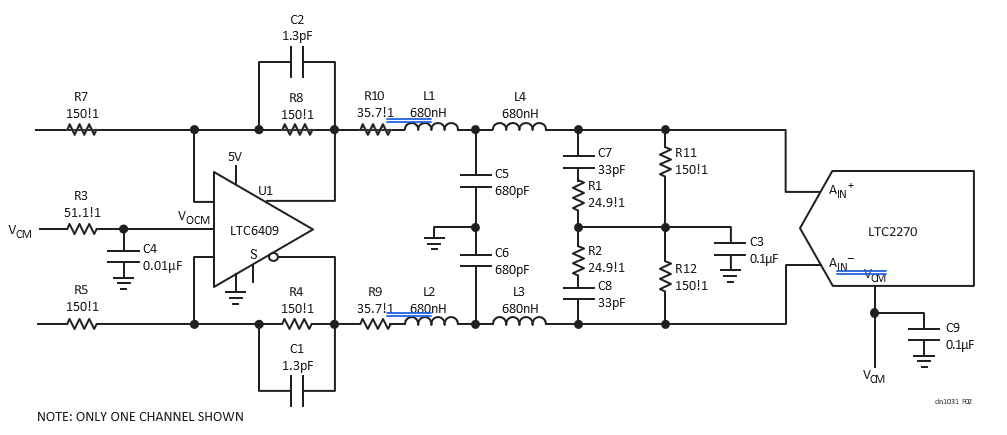

还有其他的接口过滤器设计准则,特别是关于布局的,但这些考虑提供了一些基本的方向。图1中的过滤器说明了这些规范,并且在实验室中表现良好。图2显示了完整的界面。

图1所示。LTC6409和LTC2270之间使用了大约10MHz的接口滤波器。 图2。完整的ADC接口包括LTC6409作为缓冲器,10MHz低通滤波器和LTC2270。

实验室测试

特定设计的适当滤波器和终止必须经过实验验证,因为没有单一的规则或方程涵盖所有设置。实验室测试确保滤波器可以承受这些电路现实,如电路板寄生。实验室测试也可以证明,电阻和无功端接对系统畸变有显著影响。

例如,图3显示了使用图2中的接口执行的双音测试。此外,图4显示了吸收端接和无输出端接之间的失真恶化。带内sfdr优于100dB,信噪比仅下降0.4dB。实验结果也可能显示意外的过量噪声或失真。在大多数情况下,一些调整是必要的。例如,减少带宽可能会增加信噪比,但往往以失真为代价。

图3。LTC2270的双音频谱。本底噪声增强是由信号发生器引起的。 图4。LTC2270以20Msps采样2.4MHz正弦波的频谱。(上)当所有输出终止从接口滤波器中移除时,SFDR非常差。(下)预期的滤波器在信噪比和失真方面显示接近数据表规格。

下面是一些设计界面过滤器时需要牢记的实用规则:

保持过滤器的值和布局对称

仅使用低失真电容器,如COG/NPO,去Q或使用低Q滤波器电感

提供共模滚转

结论

尽管LTC2270具有额外的采样电容,但合适的驱动器和10MHz滤波器几乎不会降低LTC2270的数据表规格。虽然LTC6409可以与ltc2270一起工作以数字化更高的频率,但滤波器设计可能不像用缩放值替换电感和电容器那样简单。最后,使用基准测试来产生经验证据来证明任何ADC接口的充分性。

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)