基于Si538x的首款满足4.5G设计的无线时钟器应用方案

275

275

拍明

拍明

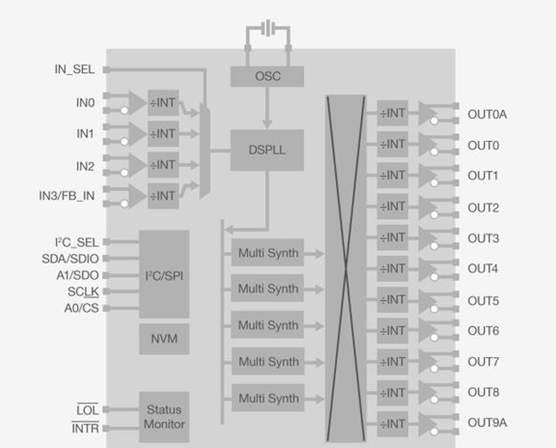

SiliconLabs最新发布的Si538x系列无线时钟发生器利用我们的最新第四代DSPLL®技术,可以满足针对4.5G移动通信标准或基于以太网的小型蜂窝网络、分布式天线系统(DAS)、μ-BTS,基带单元(BBU)、远程无线电头端(RRH)和前传/回传设备等无线区域网络设备对形状因数、功耗和性能的严苛要求。

设备的这种无与伦比的集成减少了功耗和尺寸,同时不影响无线应用对性能和可靠性的严苛要求。Si538x是业内首款无线时钟发生器,能够利用完全集成的CMOSIC解决方案替换离散的高性能VCXO时钟。该系列包括能够产生具有少100fs典型相位抖动的无线时钟和低抖动通用时钟的设备。

Si538x设计框图与性能优势

Si538x通过在单个IC中结合4G/LTE和以太网时钟,因而大大简化了HetNet设备中的时钟生成,可提供与竞争方案相比功耗降低55%、占板面积减小70%的突破性解决方案。

STA538

Features

■Up to 96dB dynamic range

■Sample rates from 8kHz to 192kHz

■FFXTM class-D driver

■1.5V to 1.95V digital power supply

■1.5V to 3.6V analog power supply

■18-bit audio processing and class-D FFXTM modulator

■Digital volume control:

–+36dB to 105dB in 0.5dB steps–Software volume update

■Individual channel and master gain/attenuation

■Automatic invalid input detect mute

■2-channel I2S input/output data interface

■Digitally controlled POP-free operation

■Input and output channel mapping

■250mΩ output CMOS Rdson

■> 90% efficiency

■2 x 1.3W (10% THD) on 4Ω at 3.6V

■2 x 0.7W (10% THD) on 8Ω at 3.3V

■Stereo headphone plus mono speaker application:

–50mW stereo into 32Ω headphone,1.2W mono into 4Ω speaker at 3.3V–100mW stereo into 16Ω headphone, 1.2W mono into 4Ω speaker at 3.3V

The Si5381/82is a wireless multi-PLL, jitter-attenuating clock that leverages SiliconLabs’ latest fourth-generation DSPLL technology to address the form factor, power, andperformance requirements demanded by radio area network equipment, such as small cells, baseband units, and distributed antenna systems (DAS). The Si538x is the indus-try’s first multi-PLL wireless clock generator family capable of replacing discrete, high-performance, VCXO-based clocks with a fully integrated CMOS IC solution. TheSi5381/82 features a multi-PLL architecture that supports independent timing paths forJESD wireless clocks with less than 85 fs typical phase jitter as well as Ethernet and oth-er low-jitter, general-purpose clocks. DSPLL technology also supports free-run and hold-over operation as well as automatic and hitless input clock switching. This unparalleledintegration reduces power and size without compromising the stringent performance andreliability demanded in wireless applications

责任编辑:Davia

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)