基于NANDFLASH 存储芯片K9WBG08U1M+DSP芯片BF533+FPGA芯片EP2C35的大容量视频存储系统的设计方案的大容量视频存储系统的设计方案

20

20

拍明

拍明

原标题:基于NANDFLASH的大容量视频存储系统的设计方案

引言

科技的发展,尤其是航空、航天、航海技术的发展,对于科研设备所拍摄的视频数据以及设备运行情况的监视录像,都迫切地需要一种容量大、速度快、存储性能可靠的图像存储设备。传统的存储介质主要以早期的磁带机和其后的磁盘为主,由于磁带机存储密度低,存储内容不易査找,已经退出了历史舞台。而磁盘受到强烈震动后容易丢失数据,严重制约了它在航空、航天、航海领域中的应用。与传统的硬盘相比,NADNFLASH作为一种新兴的半导体存储器件具有存储密度高、可靠性高、体积小、质量轻、功耗小、寿命长、无噪声、抗震动、能适应恶劣的力学和温度环境等优点。由此可见,基于NADNFLASH的大容量存储系统的研究具有更为重要的意义。

1 系统概述

本系统以ADI公司的高性能DSP芯片BF533为核心,用并行外围接口(PPD来接收中心控制板的视频数据和控制命令,并将处理结果和存储在介质中的视频数据传输给中心控制板;以Sumsung公司的NANDFLASH芯片K9WBG08U1M为存储介质;用Altera公司的FPGA芯片EP2C35来实现对FLASH的时序控制。根据实际需求,本系统使用了100片K9WBG08U1M芯片,存储深度可达400GB,其安全存储速率可达5MB/s。该系统的视频数据釆用文件的形式来管理,即每个视频文件都有一个文件表项,里面包含文件名称、文件地址以及文件大小等信息,此表项存放在FLASH的文件列表中,在进行存储、下载、剪切、删除等操作时,都需要将文件列表读到DSP的SDRAM中,以确定目标文件的地址,从而进行后续处理。

2 系统硬件设计

2.1 芯片的选择

K9WBGO8U1M芯片通过8位复用的I/O总线多周期输入寻址,即共分5个周期,前2个周期输入A0〜All的页内地址(列地址),后3个周期输入A12〜A30的页地址(行地址)。其单片存储容量为(4G十128M)B,内部由两片K9KAGO8UOM芯片构成,而K9KAG08U0M芯片又分为8192块,每块64页,每页(4K+128)B。该芯片以页为单位来进行编程和读操作,典型编程时间为200倨,最大编程时间为700Ms,最小写周期为25ns,最小串行读周期为50ns;以块为单位进行擦除,典型擦除时间为1.5ms。其内部有一个页寄存器,在进行编程和读操作时,先将要写或要读的一页数据缓存到页寄存器中,然后写入编程命令开始页编程或发送读使能信号开始串行读。由此可以计算出FLASH的最快写入速率为4096B/(200俸十4096X25ns)^13Mb/s,安全写入速率为4096B/(700fzs+4096X25ns)^5Mb/so考虑到数据的安全写入,我们选取了最大编程时间700”,即安全写入速率为5MB/so

2.2 系统硬件结构框图

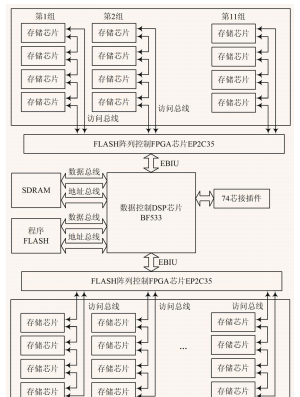

本系统作为网络视频存储系统的子系统,通过DSP的半双工接口PPI与中心控制板进行通信。首先将接收到的数据缓存在SDRAM中,然后对缓存下来的数据进行分析,辨别命令类型后进行与命令相应的操作,同时通过UART这个低速通道向中心控制板返回实时状态信息。其硬件结构框图如图1所示。

FPGA作为DSP的异步外设连接到DSP的系统总线上,DSP通过存储器DMA的方式向FPGA发送数据和读取FPGA内部RAM中的数据。考虑到FPGA自身I/O引脚数量的限制和引脚驱动能力,本系统采用两片FPGA来驱动100片FLASH,FLASH阵列分为25组,每组4片FLASH,共用一套数据/地址总线和控制总线,各片FLASH通过片选信号来选中。

DSP的PPI接口接收到的视频数据是经过MPEG-4格式压缩过的,其最大bit流速率为4Mb/s。PPI的总线时钟频率最大可达133MHz,也就是数据传输速率最大可达133MX16b/s,所以对于4Mb/s的视频数据完全可以满足要求。视频数据到达存储板后,由FPGA负责写入存储器,存储芯片K9WBG08U1M的写入速率为5MB/s,每路视频数据率为4Mb/s=0.5MB/s,故存储芯片K9WBG08U1M也可以达到存储速率的要求。

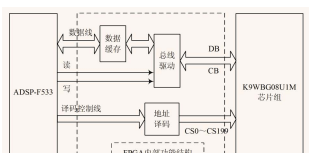

2.3 FLASH的驱动设计

本系统采用FPGA给FLASH提供总线驱动和译码逻辑,以其中一片FPGA为例,其具体实现图如图2所示。

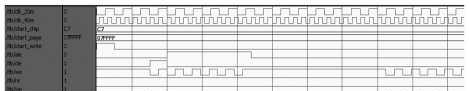

在FPGA内部构建两个双口RAM,一个用于存储操作,一个用于下载操作。当进行存储操作时,FPGA首先接收DSP发送的数据(包含地址信息)存储在双口RAM中,此过程采用MDMA的方式。数据接收完成后,DSP给FPGA发送启动信号,此时FPGA开始产生FLASH控制时序将存储在双口RAM中的数据写入FLASH中,同时根据地址信息译码产生相应的片选信号来选中某一片FLASH芯片。在编程过程中,只要保证下一次MDMA结束前当前页编程已经结束,就可以产生一个脉冲通知DSP准备下一页写入操作,这样可以让MDMA与编程同时进行,从而提高写入速率;同理,在进行下载操作时,先将FLASH中的数据缓存到双口RAM中,然后通知DSP进行MDAM操作即可。图3给出了存储操作的功能仿真波形。从图中可以看出完全满足FLASH的写入时序,经验证,此模块实现的存储

效果非常好。

图3 存储模块的功能仿真波形

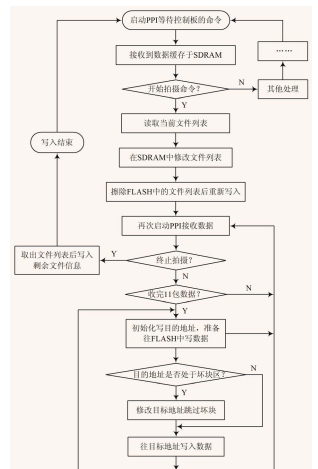

3 系统软件设计

系统上电复位加载完程序之后,程序对寄存器初始化完成后就进入循环等待状态,准备接收中心控制发送的命令。当通过PPI接收到命令后,就对命令进行分析,判断中心控制板要存储板完成什么操作,如视频文件存储、下载、剪切、复制或删除等等。文件存储流程图如图4所示。

当上位机通过网络给中心控制板发送开始命令后,中心控制板首先发送开始拍摄命令和拍摄视频参数给前端视频压缩系统,建立TCP链接,然后发送开始命令给存储板。存储板接收到中心控制分系统发送过来的命令后,首先读取文件列表到DSP的SDRAM当中,DSP检索出其中的文件个数和最后一个文件的存储地址,在SDRAM中添加新文件表项到当前的文件列表,然后擦除先前存储在FLASH中的文件列表后重新写入修改过后的文件列表。根据系统压缩的要求,如果前端压缩后的码流速度为2Mb/s,为了使得DSP集中处理数据,我们拟定中心控制板和存储板之间每4s传输一次数据。由于每次压缩后的数据长度不是一个既定数,因此只能按照最大数据长度来传输,即每次传输1MB。由于PPI接口寄存器位宽的限制,每次传输数据长度不能超过(128K-DB,我们设定每次传输长度为100KB,则DSP通过PPI接收的数据需要通过11次才能接收完毕。中心控制分系统把有效数据长度作为一个参数放置在数据的末尾,存储板按照这个参数对缓存到SDRAM中的数据进行处理,剩余无效数据抛掉。

4 坏块的检测处理

由于制作工艺等原因,NANDFLASH在出厂时会存在随机分布的坏块,另外FLASH在使用过程中也会造成坏块。如果冒然对坏块进行操作,会造成数据的丢失,影响数据的完整性。另外,在检测编程和擦除结束标志时,FLASH的I/O返回的状态不稳定,会导致程序进入无限等待状态,这样会大大影响整个系统的性能。因此,有必要对FLASH进行坏块检测和处理。

检测坏块的方法有两种:一种方法是利用芯片出厂时厂家给的坏块信息,它被厂家标记在坏块的第一页和第二页的备用空间的首字节中,即页内地址(列地址)为4096的字节中。如果这两个字节都是OxFF,则表明当前块不是坏块,否则为坏块。另一种方法是将当前块先擦除,然后读出当前块的数据,如果读出的数据不全是OxFF,则表明此块为坏块(考虑到不使用备用空间)。

由于坏块与有效块相互独立,互不影响,所以对FLASH进行操作时只要将坏块跳过即可。考虑到本系统的视频数据采用文件的形式存储,也就是说在读写操作之前DSP需要准确知道文件的存储地址,包括文件的开始地址和结束地址,所以必须要将检测出来的坏块表存储在DSP的存储器中。如果将坏块列表存放在NANDFLASH中,会存在一个问题:存放坏块列表的地方本身就在坏块区该如何处理,如果做特殊处理的话会影响程序的一致性。另外,每次搜索之前都得把坏块列表从NANDFLASH中读出来,这样的话程序会进入好几次中断,从而影响整个程序的流程。考虑到程序烧写FLASH有16Mb,而DSP程序不超过20KB,于是可以将坏块列表放在程序烧写FLASH中,也就是说程序烧写FLASH既存放程序,又存放坏块列表。这样,DSP可以对坏块列表进行直接访问。

5 结语

在整个系统的测试过程中,本部分工作正常,对NANDFLASH的访问能跳过坏块,保证数据的正确性和完整性。另外,如何采用流水线方式提高存储速率是今后研究的重点。

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)