A/D转换器外部支持电路设计方案

21

21

拍明

拍明

原标题:A/D转换器外部支持电路设计方案

该应用笔记介绍了测量和最大化 120 dB、24 位和 96 kHz 模数转换器集成电路性能的技术。它介绍了 ADC 架构、输入缓冲器设计及其噪声要求、噪声计算和噪声分析。它还描述了外部支持电路设计和一些示例结果。

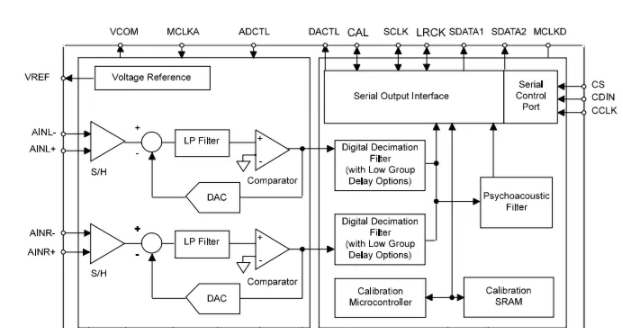

A/D 转换器架构

本次讨论中使用的 A/D 转换器由一个模拟 delta sigma 调制器芯片和一个数字滤波器芯片组成,封装在单个 28 引脚 SOIC 塑料封装中。图 1 显示了该设备的框图。delta-sigma 调制器设计的亮点包括使用三电平调制器,校准后可产生出色的线性度,调制器输出数据的新颖编码方案,可消除数据信号边沿数量和极性的数据相关变化,以及全差分设计,产生低失真和良好的共模抑制。抽取滤波器包括多个字长输出选项,以及可选的心理声学噪声整形。还包括实时使用的低群延迟。

A/D 转换器框图

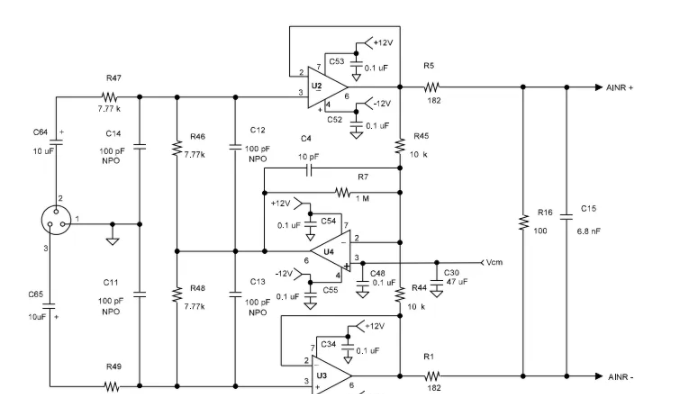

输入缓冲器设计

A/D 转换器的输入缓冲电路必须满足几个严格的要求。这些包括:可忽略的噪声贡献、DC 电平从通常以零伏为中心的输入信号转移到以 A/D 转换器的共模电压为中心的输出信号、将缓冲放大器与开关电容器电流瞬变隔离,同时保持低输出阻抗,以免引起失真,并提供适合调制器采样率的抗混叠滤波。

输入缓冲器电路图

图 2 显示了为此应用选择的伺服平衡差分输入缓冲电路。该电路通过输入端子上任一极性的差分或单端信号提供所需的差分输出。输入缓冲器的增益结构旨在衰减产生 0 dBFS 数字输出所需的 25.5 dBu (1.414 Vrms)。缓冲器输入结构中的 6 dB 衰减之后是 A/S 转换器输入处的电阻网络,它提供额外的 13.3 dB 衰减

外部支持电路设计

A/D 转换器的这种性能可能会因外部环境设计不当而降低。本节介绍 A/D 转换器周围的直接环境,包括接地层推荐、去耦电容器选择、正确的时钟发生器连接和过压保护。

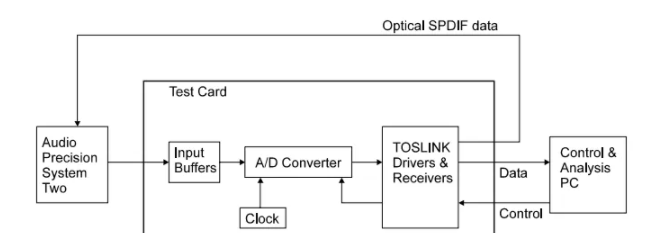

测试设置说明

测试设置信号流

图 3 显示了测试设置的主要组件。这种设置的目标是提供尽可能有利的环境,使 A/D 转换器能够发挥其最佳性能。Audio Precision System 2 用作模拟测试信号发生器,并在 48 kHz 采样率下确认一些测量结果。PC 用于通过其控制端口控制 A/D 转换器,还用于收集 96 kHz 的 A/D 转换器输出数据。在 PC 上运行的定制软件允许控制 A/D 转换器和输出数据的 FET 分析。

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)