基于TMS320C6414 DSP处理器+XC2V6000 FPGA芯片实现通用FPGA测试平台的搭建方案

40

40

拍明

拍明

原标题:基于TMS320C6414 DSP处理器实现通用FPGA测试平台的搭建方案

1 引言

随着通信系统向高速度、低功耗、低电压和多媒体、网络化、移动化方向的发展,其对电路的要求日益提高,传统的单一功能的集成电路技术已经无法满足需要。而FPGA由于其固有的特性,被日益广泛的应用于通信系统中。FPGA可以方便的修改逻辑结果,完成对系统和设备的升级,以便迅速适应市场的变化;同时,FPGA可以支持多种通信协议和接口标准,并可以随着标准和协议的演变而方便的改变。

在结束对算法的代码编写以后,为了验证设计的正确性与可靠性,通常采用逻辑分析仪进行测试,测试的流程如下:

编写模块代码-》产生需要的激励-》将所需激励变成数据文件存储到FPGA的内部RAM中-》连接逻辑分析仪进行测试。

该方法主要缺点是:

1)器件存储器容量很有限,无法满足通信系统数据量大这一要求。以802.16e MIMO 2x2无线通信系统的信道估计算法为例,存储一个下行数据帧的信道值约需要3,500Kbit,就目前高性能FPGA的存储能力而言是难以完成的。例如Xilinx公司最先进的XC2V8000型FPGA仅有3,024Kbit的存储空间。

2)对于高速率的系统,现有的数字电路测试工具(如逻辑分析仪等)无法同时存储长时间的数据。较新型的逻辑分析仪,如Tektronix公司的TLA700系列,也仅能存储2ms内的测试数据,通信系统的数据传输一般以帧为单位,为了对通信系统进行完整的测试,常常需要同时观测一帧内所有的数据,仍然以802.16e MIMO 2x2无线通信系统为例,一帧的时间长度为5ms,普通的逻辑分析仪无法满足上述无线通信系统的测试需要。

为了能够发挥FPGA处理速度快的优势同时克服其测试上存在缺陷,本文介绍了一种硬件测试平台的设计方案。该平台由DSP处理器和FPGA芯片通过通信接口连接而构成,通过控制模块可以观测算法测试的结果并且能对测试的过程进行控制。由于DSP可以及时将测试结果导入PC主机,从而解决了大数据、长时间测试困难的问题。除此,该测试平台不仅可以应用于算法的硬件测试,由于其解决了DSP与FPGA接口通信困难的问题,实现了处理器间高速率的通信,通过小的改动可以将该平台扩展,应用于通信系统的设计。

2 硬件测试平台的设计

2.1. 平台硬件结构及模块功能描述

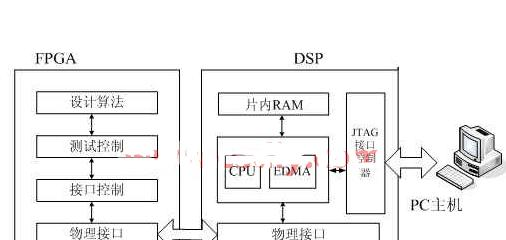

平台的实现采用Xilinx公司的XC2V6000 FPGA芯片和TI公司的TMS320C6414 DSP处理器。底层的物理接口使用C6414的外部存储器接口(External Memory Interface,以下简称EMIF),在数据传输时采用异步工作方式。测试控制模块、接口控制模块均在FPGA中完成。DSP的直接存储器访问(Extended Direct Memory Access,以下简称EDMA)控制 器,负责EMIF接口的数据传输。DSP与PC主机的交互通过JTAG口完成。

平台的模块化设计如图1:

硬件测试平台在FPGA中处理待测算法。测试控制模块向上控制算法运行的开始、结束,向下控制何时需要导入新的测试数据、何时需将处理结果导出至DSP。接口控制模块受控于测试控制模块,完成接口的时序控制和匹配。DSP处理器负责存储测试数据和处理结果并将数据导入PC主机,同时DSP还负责向FPGA和外部扩展存储器提供无缝接口。

该硬件平台的优势在于依托PC主机海量的存储空间,可以无限制的增大测试的数据量和测试时间,使得硬件平台下算法的测试不再受器件存储大小的限制。

平台对于不同的算法具有通用性。在FPGA中,无需重写接口控制模块和测试控制模块,就可以完成针对不同算法的硬件测试。在DSP端,其对存储器件和接口时序的控制对于具体算法来说是透明的,不同的算法测试不要求DSP中的模块作任何修改。

2.2. DSP端的配置

2.2.1. EMIF接口的配置

C64x系列DSP对外部存储器件提供了无缝接口,该接口数据总线宽度为64bit,同时也提供对32bit/ 16bit/ 8bit 的读写支持。

异步读写模式

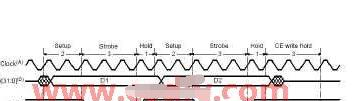

C64x异步接口时序的可编程性高,使用灵活,可以适应不同的设计需要,故平台的接口传输采用异步模式。异步模式每个读/写周期由3个阶段构成:建立时间(Setup)、触发时间(Strobe)、和保持时间(Hold)。其中建立时间是指从存储器访问周期开始到读/写选通有效之前;触发时间为读写选通信号自有效到无效的时间段;保持时间指从读/写信号无效到该次访问周期结束。该模式可稳定工作在50MHz的外部时钟下,其最大的数据速率为1.6Gbit/s。下图给出了一个典型写操作时序的例子:

图中,当触发时间开始时,异步写使能

![]()

在触发时间开始时有效,在保持时间开始时无效,在

![]()

有效期内完成一次异步写操作。

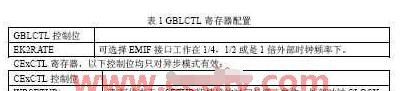

控制寄存器配置[4]

异步模式下,C64x EMIF接口时序由全局控制寄存器(Global Control Register)GBLCTL和一组存储器映射的寄存器CExCTL进行控制与维护,详细的配置情况如下表:

2.2.2. EDMA控制器的使用

在系统中使用硬件中断启动DSP的EDMA,并由EDMA控制器控制EMIF接口接收或发送数据,就可以实现FPGA与EMIF接口间的数据传输。

EDMA控制寄存器设置

数据传输开始前必须完成一系列控制寄存器的设置。首先是事件寄存器ER(Event Register),通过对某些比特位置“0” ,该寄存器负责捕获相应比特位代表的中断事件;进一步设置事件使能寄存器EER(Event Enable Register),控制每一事件的使能/禁止,设置方法与ER相同。

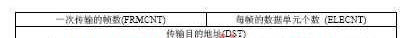

通道参数RAM配置

对于每一条通道,为了使数据符合设计的传输格式,必须对该通道的参数RAM写入一定的控制字。

2.2.3. DSP与主机的通信方式

平台使用DSP开发工具CCS(Code Composer Studio)集成的数据导入/导出功能实现DSP与PC主机间的数据传输。

在一次测试开始前或结束后,需要由PC主机导入新的测试数据或向主机导出处理结果,而数据导入/导出功能则是由CCS内部的探针(Probe)实现的。通过在代码中插入探针,并将数据文件与相应探针关联,CPU运行至探针所在代码处便会通过JTAG控制器自动完成数据IO的功能。使用DSP的JTAG接口与PC主机通信,能在测试过程中及时的更新输入数据或将运算结果,从而解决了传统方法无法完成大数据量、长时间硬件测试的问题。

2.3. FPGA端的配置

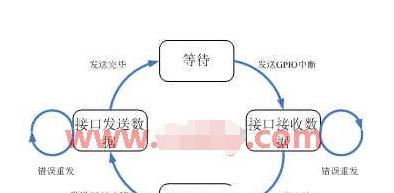

FPGA对于测试过程的控制可以表示为一*状态的状态机,其工作原理可以表述为以下过程:

① 等待状态:FPGA发送GPIO中断,告知DSP端将测试数据导入;

② 接收状态:在此状态下,FPGA接收来自EMIF接口的测试数据,并且通过计数器判断数据是否接收完毕,如完毕,转入算法处理状态,否则重复接收;

③ 发送状态:类似接收状态,FPGA向DSP发送处理结果,如完毕转入下一等待状态,否则返回发送状态;

④ 算法处理状态:此状态下,FPGA处理待测算法,由于收发状态的转移均有FPGA控制,故此状态不可能被新的收发状态打断;处理完毕后,转入发送状态;

状态转移图如下:

图3 FPGA控制模块状态转移图

3 测试平台的通用性

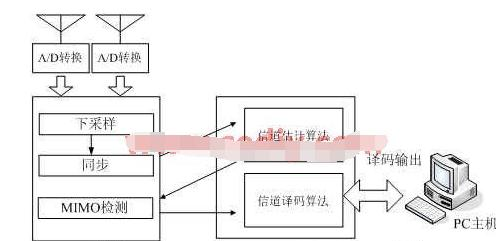

由于实现了DSP与FPGA间高速率接口,并且实现了处理器的协同工作,该平台在通信系统的设计中也有实用价值。

如前述802.16e MIMO 2x2无线通信系统中,使用上述平台的硬件结构实现接收端的功能,算法层的结构模型如图4 :

图4 802.16e MIMO 2x2无线通信系统接收端结构图

4 结语

本文介绍的硬件测试平台实现了DSP和FPGA的交互,既满足算法对平台高实时性、高速率的要求,又能完成通信系统大数据量测试的要求,构建了可应用于测试各种FPGA算法的硬件测试环境。同时,在该平台DSP端加入信号处理算法,可将平台扩展为FPGA、DSP协同工作的信号处理系统。

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)