基于AD9650的高速数据采集系统的设计方案

31

31

拍明

拍明

原标题:基于AD9650的高速数据采集系统的设计方案

摘要:在高杂波环境下工作的雷达系统要求大的瞬时动态范围,才能实现对弱目标信号的录取,迫切需要设计实现高动态范围的高速数据采集系统。鉴于此,本文在研究了ADC芯片选型、时钟设计和前端电路设计对数据采集系统动态范围的影响,提出了基于AD9650的高速数据采集系统的设计方案。经论证该设计方案实现了一个16 b,65 MSPS的高速数据采集系统,用于实现对高杂波环境下雷达回波信号的采集。

0 引言

随着数字信号处理技术的发展,越来越多的信号处理环节可以通过后端的软件处理完成,但这反而使得电子设备对前端数据采集系统的要求不断提高。因为后端软件的处理效果归根结底依赖于数据中所包含的信息量,只有提高数据采集的动态性能,才能保障后端处理的效果。长期以来,在数据采集领域,高速大动态范围ADC系统的设计与实现始终是研究的热点。当雷达工作在高杂波的电磁环境中,探测对象的RCS或多普勒信息非常微弱时,就对设计实现高速大动态范围数据采集系统提出了迫切的需求。

目前,国内对高速大动态范围ADC数据采集系统设计主要依赖于芯片的指标而缺乏系统的研究和总结。本设计旨在通过优化系统设计,结合动态性能优越的模数转换芯片,实现一个高速大动态范围数据采集系统。

1 系统性能指标要求

本系统需完成的主要功能为:雷达同步控制;中频数据采集,数字正交解调;信号预处理。同时为了降低便携设备的功耗,预处理器拟采用低功耗处理器。由于要求动态范围大,中频采集需采用高精度的数据采集芯片,设计为2个通道,要求单通道量化位数不小于14 b,有效位数不小于12 b,输入信号范围2 Vp-p,且满足低功耗要求。

2 关键技术

如何保证大动态范围是设计中的关键点,同时也是难点所在,设计中从如下几方面进行考虑。

2.1 ADC芯片的选型

为了获得高速度、大动态范围,数据采集系统对ADC 的速度和量化精度的要求越来越高,而ADC 的速度和量化精度与其结构紧密相关。

目前常用的高速ADC类型主要有快闪型和流水线型。快闪型ADC 由于采用了全并行结构,具有超高速、宽输入带宽的优点,但其硬件规模随分辨率的增加呈指数增长,分辨率一般为4~8位,且存在高功耗、高成本、“闪烁码”等问题,将它应用于数据采集系统将会造成分辨率低、成本高、能耗大等弊端。而流水线型ADC具有较高的分辨率,量化位数一般为12~16位,较高的采样速率,一般为1~250 MSPS.流水线型ADC 将ADC与DAC结合,采用多级流水结构,解决了快闪式ADC无法达到较高分辨率的缺点,同时兼顾了快闪式ADC 的转换速度。因此,本文选择流水线型结构的ADC 芯片来实现高速大动态范围数据采集系统设计。

本文选择了AD公司的AD9650系列芯片。AD9650是一款双通道、16位流水线结构模数转换器,为解决高频(300 MHz)、大动态范围信号的数字化而设计。

它具有集成ADC 采样保持输入、可选择片上Dither 模式、集成输入时钟1~8 分频等诸多特点。AD9650 输出信号模式可选择,默认输出为1.8 V CMOS,通过3线SPI接口,可配置工作模式,实现输出1.8 V电平的LVDS数字信号。它具有灵活的掉电选项、采用1.8 V单电压供电,提供了重要的节能特性。片上Dither选项能够提高低电平模拟输入的无杂散动态范围(Spurious Free Dy-namic Range,SFDR)。AD9650的主要性能指标见表1.

2.2 系统采样时钟性能

ADC 芯片受时钟控制进行采样,时钟质量对采样精度影响大,制约着系统所能达到的有效位。系统时钟主要性能指标包括时钟抖动和相位噪声。下面分别讨论两个指标对采样系统的影响。

时钟抖动表征了模拟输入实际采样时采样时间的不确定性。由于抖动会降低宽带ADC 的噪声性能,因此,ADC噪声性能的下降将反映出时钟抖动情况。与系统信噪比(Signal-to-Noise Rate,SNR)边界值(单位:

dB)之间存在的关系如式(1)所示:

式中:fanalog表示模拟输入频率;tjitter表示时钟抖动,整理公式(1)得:

ADC有效位数(Effect Number of Bit,ENOB)与SNR的关系:

由式(1)和式(3)可得系统有效位数与模拟输入频率及系统时钟抖动的关系图,如图1所示。

忽略其他因素,仅考虑时钟抖动对ADC性能的影响,由式(1)可知,若要对20 MHz的中频信号进行采样,同时保证74 dB以上的SNR,则要求时钟抖动为1.588 ps RMS.且ADC电路的时钟抖动(tjitter)与采样时钟抖动(tjitter_clk)和ADC器件自身孔径抖动(tjitter_adc)之间存在如下关系:

另外,采样时钟的相位噪声对ADC 性能有着重要影响。若采样过程用单位圆来表示,则每通过零相位,ADC 进行采样。采样时钟上的噪声将对相应矢量的顶点位置进行调制,从而改变发生过零的位置,造成采样过程提前或编码过程延迟。而采样时钟上的噪声矢量可能是相位噪声所导致的。如图2所示。

图2 中,理想情况下时钟信号应为单谱线。然而,受电源噪声、时钟抖动等因素影响,频域中存在大量能量分布在理想频率附近,代表相位噪声的能量。由于相位噪声往往可能扩展至极高频率,所以,它会使ADC的性能下降[6].采样过程实质是一个采样时钟与模拟输入信号的频域卷积过程,这个卷积过程在整个频谱域有效,同时在微观上也同样有效。因而,图2所示的时钟频率周围集中的相位噪声也将与模拟输入进行卷积,造成输出的数字信号频谱失真。

采样时钟相位噪声通常以单边带相位噪声来衡量,即:

由此可以计算出采样时钟相位噪声,作为系统设计的依据。

在本系统中,为保证时钟特性,时钟源由高精度晶振提供,时钟抖动控制在1.2 ps RMS以内,相位基底噪声为-165 dBc/Hz.板上时钟转换选用AD 公司的AD9513,其附加的时钟抖动为300 fs,输出的时钟信号性能满足要求。它实现对单路时钟转两路LVDS信号,给AD9650 提供采样时钟,同时给FPGA 提供同步控制时钟。图3给出了时钟电路设计原理图。

2.3 前端电路设计

ADC前端电路主要完成对模拟输入幅度、信号形式的调整。它采用交流耦合方式,通过差分放大器,实现对信号幅度调整,同时实现单端输入信号转差分信号。并且,通过后续的滤波器实现信号的滤波。其结构如图4所示。

虽然差分运放是有源器件,使用中会消耗功率,且产生噪声,但它的性能限制比变压器少,可以在必须保留直流电平时应用,而且放大器增益设置简单灵活,且通带范围内提供平坦的响应,而没有由于变压器寄生交互作用引起的纹波。

ADC的 S (N + D) (信号噪声失真比)是决定驱动放大器的关键因素。如果在目标频率范围内,驱动放大器的THD ( 总谐波失真加性噪声) 总是优于ADC 的S (N + D) 值 6~10 dB,那 么 所 有 由 放 大 器 造 成 的S (N + D)降低将相应限制在接近0.5~1 dB.

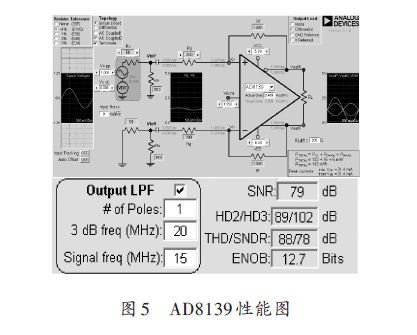

利用ADI 公司提供的ADI DiffAmp Calculator 软件可得到前端电路仿真图,如图5所示。由文献[3]可知在输入信号为15 MHz时,AD9650的 S (N + D) 为82 dB,而图5 中AD8139 的THD 为88 dB,满足上述要求。综合考虑增益及通带内响应及输入阻抗等因素,前端电路采用ADI公司的差分运放AD8139.

3 方案设计系统结构及实物

根据系统要求,设计的高速大动态范围ADC 数据采集系统,结构如图6所示,主要包括模数转换模块、数字信号预处理模块、数据传输模块和嵌入式单板机等。

模数转换模块是信号采集系统重要的组成部分。它主要包括ADC、前端电路和时钟电路等。主要完成的功能是实现对模拟中频输入信号的数字化,以用于后续的数字信号处理。

数字信号预处理模块采用较为成熟的FPGA+DSP结构,主要实现对数字信号的FFT、数字正交解调等,同时实现对原始数据传输。信号预处理主要在DSP中完成,而FPGA内部搭建两个FIFO来实现数据传输,同时完成对收发单元等的控制功能。FPGA采用Xilinx的低功耗高性能产品Spartan6,DSP 采用Analog Device公司的低功耗DSP产品ADSP21479.

数据传输模块采用Cypress 公司的CY7C68014,通过USB 接口完成由FPGA 向嵌入式单板机的数据传输。嵌入式单板机具备各种符合计算机协议的数据接口,包括与电子硬盘的存储接口,与上位机的网络通信接口,以及与预处理卡的USB通信接口。

数据采集系统硬件电路实物,如图7所示。系统分成两块电路板,即模拟ADC板和FPGA+DSP数字板,两者通过PMC插件连接。

4 结语

本文研究了影响数据采集系统动态范围的关键因素,给出了在采集系统设计时选择芯片、设计时钟和前端电路的依据,以此为基础提出了一种高速数据采集系统的设计方案。论证分析表明,该设计方案能够满足雷达数据采集系统高速大动态范围的要求。

责任编辑:

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)