基于STM32F205RBT6主控芯片的core205r开发板/核心板解决方案

335

335

拍明

拍明

原标题:STM32F205RBT6为主控芯片的核心板方案

应用领域:电子元器件

方案类型:成品

主要芯片:STM;

方案概述

它的主要特点是:

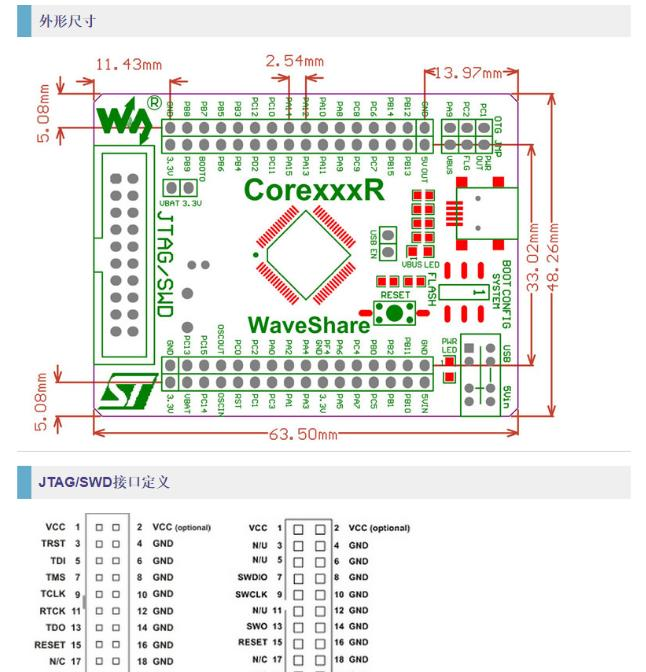

板载MCU的基本电路,包括晶振电路,USB电源管理电路,USB接口等

引出了所有I/O资源

带JTAG/SWD调试下载接口

排针间距2.54mm,体积较小,适合接入用户系统

包括如下内容:

原理图

示例程序(C程序、μC/OS-II)

STM32开发软件(KEIL等软件)

STM32器件手册

STM32开发资料

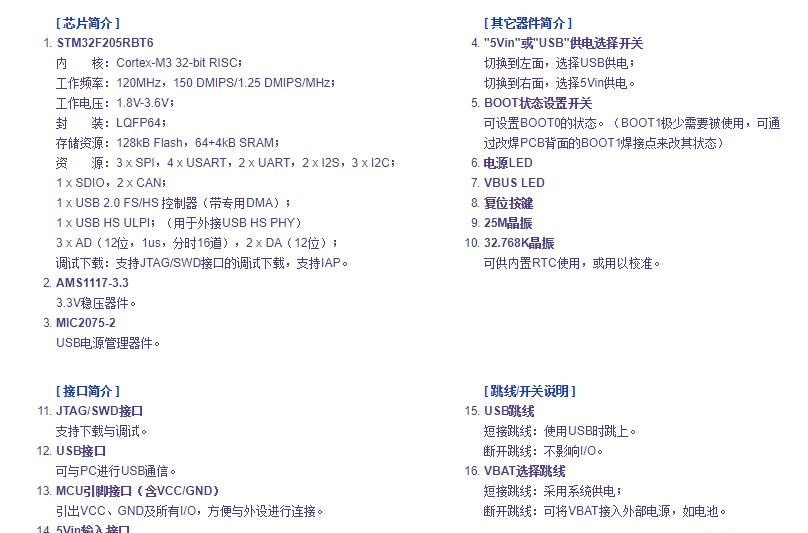

【STM32F205RBT6】

High-performance Arm Cortex-M3 MCU with 128 Kbytes Flash, 120 MHz CPU, ART Accelerator

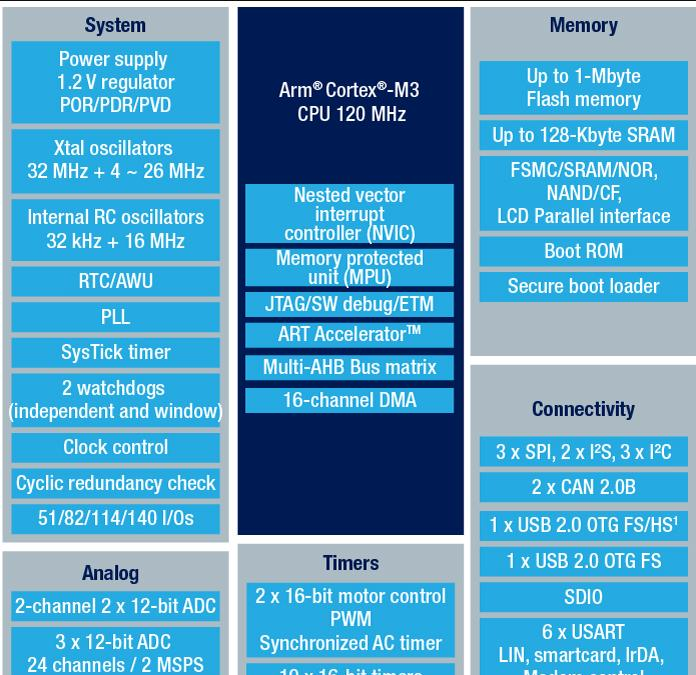

The STM32F20x family is based on the high-performance ARM®Cortex®-M3 32-bit RISC core operating at a frequency of up to 120 MHz. The family incorporates high-speed embedded memories (Flash memory up to 1 Mbyte, up to 128 Kbytes of system SRAM), up to 4 Kbytes of backup SRAM, and an extensive range of enhanced I/Os and peripherals connected to two APB buses, three AHB buses and a 32-bit multi-AHB bus matrix.

The devices also feature an adaptive real-time memory accelerator (ART Accelerator™) that allows to achieve a performance equivalent to 0 wait state program execution from Flash memory at a CPU frequency up to 120 MHz. This performance has been validated using the CoreMark® benchmark.

All devices offer three 12-bit ADCs, two DACs, a low-power RTC, twelve general-purpose 16-bit timers including two PWM timers for motor control, two general-purpose 32-bit timers. a true number random generator (RNG). They also feature standard and advanced communication interfaces. New advanced peripherals include an SDIO, an enhanced flexible static memory control (FSMC) interface (for devices offered in packages of 100 pins and more), and a camera interface for CMOS sensors. The devices also feature standard peripherals.

Key Features

Core: ARM® 32-bit Cortex®-M3 CPU (120 MHz max) with Adaptive real-time accelerator (ART Accelerator™) allowing 0-wait state execution performance from Flash memory, MPU, 150 DMIPS/1.25 DMIPS/MHz (Dhrystone 2.1)

Memories

Up to 1 Mbyte of Flash memory

512 bytes of OTP memory

Up to 128 + 4 Kbytes of SRAM

Flexible static memory controller that supports Compact Flash, SRAM, PSRAM, NOR and NAND memories

LCD parallel interface, 8080/6800 modes

Clock, reset and supply management

From 1.8 to 3.6 V application supply + I/Os

POR, PDR, PVD and BOR

4 to 26 MHz crystal oscillator

Internal 16 MHz factory-trimmed RC

32 kHz oscillator for RTC with calibration

Internal 32 kHz RC with calibration

Low-power modes

Sleep, Stop and Standby modes

VBATsupply for RTC, 20 × 32 bit backup registers, and optional 4 KB backup SRAM

3 × 12-bit, 0.5 μs ADCs with up to 24 channels and up to 6 MSPS in triple interleaved mode

2 × 12-bit D/A converters

General-purpose DMA: 16-stream controller with centralized FIFOs and burst support

Up to 17 timers

Up to twelve 16-bit and two 32-bit timers, up to 120 MHz, each with up to four IC/OC/PWM or pulse counter and quadrature (incremental) encoder input

Debug mode: Serial wire debug (SWD), JTAG, and Cortex®-M3 Embedded Trace Macrocell™

Up to 140 I/O ports with interrupt capability:

Up to 136 fast I/Os up to 60 MHz

Up to 138 5 V-tolerant I/Os

Up to 15 communication interfaces

Up to 3 × I2C interfaces (SMBus/PMBus)

Up to four USARTs and two UARTs (7.5 Mbit/s, ISO 7816 interface, LIN, IrDA, modem control)

Up to three SPIs (30 Mbit/s), two with muxed I2S to achieve audio class accuracy via audio PLL or external PLL

2 × CAN interfaces (2.0B Active)

SDIO interface

Advanced connectivity

USB 2.0 full-speed device/host/OTG controller with on-chip PHY

USB 2.0 high-speed/full-speed device/host/OTG controller with dedicated DMA, on-chip full-speed PHY and ULPI

10/100 Ethernet MAC with dedicated DMA: supports IEEE 1588v2 hardware, MII/RMII

8- to 14-bit parallel camera interface (48 Mbyte/s max.)

CRC calculation unit

96-bit unique ID

STM32F205RBT6 CIRCUIT DIAGRAM

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)