74hc165引脚图及功能

1

1

拍明芯城

拍明芯城

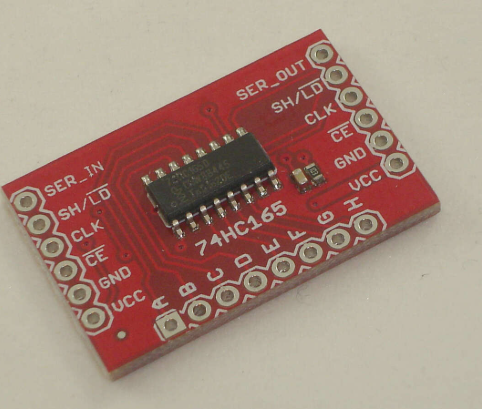

74HC165并行输入/串行输出移位寄存器:引脚图与功能详解

74HC165是一款高性能CMOS并行输入、串行输出8位移位寄存器,广泛应用于各种需要将并行数据转换为串行数据进行传输的场景。它在数据采集、传感器接口、扩展I/O端口以及与微控制器通信等方面发挥着重要作用。理解其引脚功能对于正确使用该芯片至关重要。

1. 74HC165引脚图

74HC165通常采用16引脚的DIP(双列直插)或SOIC(小外形集成电路)封装。以下是其典型引脚分配及功能描述:

2. 引脚功能详解

电源与地

VCC (引脚16): 电源正极。通常连接到+2V到+6V的直流电源。为芯片内部逻辑电路提供工作电压。稳定的电源是确保芯片正常工作和数据完整性的基础。

GND (引脚8): 地。通常连接到电路的公共地线。作为所有内部逻辑电路的参考电位。正确的接地对于抑制噪声和确保信号完整性至关重要。

并行数据输入引脚

74HC165拥有8个并行数据输入引脚,允许同时加载8位数据。这些引脚通常连接到需要转换成串行数据的并行数据源,例如传感器的输出、开关阵列或微控制器的并行端口。

P0 (引脚11)

P1 (引脚12)

P2 (引脚13)

P3 (引脚14)

P4 (引脚3)

P5 (引脚4)

P6 (引脚5)

P7 (引脚6)这八个引脚是并行数据输入端口。当加载脉冲($overline{PL}$为低电平)时,输入到这些引脚的8位并行数据会被同时加载到内部寄存器中。每个引脚对应一位数据,P0为最低有效位(LSB),P7为最高有效位(MSB)。这些输入引脚具有高阻抗特性,可以与其他逻辑门兼容,并允许直接连接到各种数字信号源。

时钟与控制引脚

这些引脚负责控制数据的加载、移位操作以及输出使能。它们是74HC165实现其并行到串行转换功能的关键。

CLK (引脚2) / CP (Clock Pulse): 时钟输入。这是移位寄存器的主要时钟输入。在串行移位模式下,数据的移位操作是在CLK引脚的上升沿(或下降沿,具体取决于芯片型号和手册说明,但74HC系列通常为上升沿)触发的。每一次时钟脉冲都会使内部寄存器中的数据向串行输出端(QH)移位一位。因此,要读取全部8位数据,需要发送8个时钟脉冲。

PL (引脚1) / PL (Parallel Load) / SH/LD (Shift/Load): 并行加载使能(低电平有效)。当此引脚为低电平时,并行输入引脚(P0-P7)上的数据将被异步加载到内部8位寄存器中。一旦数据加载完成,$overline{PL}应被置为高电平,以便进行移位操作。如果overline{PL}$一直保持低电平,那么移位功能将被禁用。这是一个非常重要的控制信号,它决定了芯片是在加载并行数据还是在进行串行移位。

CE (引脚15) / CLK INH (Clock Inhibit) / CE (Clock Enable): 时钟禁止(高电平有效)。当此引脚为高电平时,它会禁止CLK引脚的时钟信号,阻止数据的移位。换句话说,即使CLK引脚有脉冲,只要CE为高电平,移位操作就不会发生。当CE为低电平时,CLK引脚才能正常工作,数据才能进行移位。这个引脚常用于暂停移位操作,或者在不希望进行数据移位时保持输出稳定。

串行数据输出引脚

这是74HC165转换后的串行数据输出端口。

QH (引脚9): 串行数据输出。这是移位寄存器的串行数据输出引脚。在CLK的每个有效沿,最高有效位(MSB)的数据会从QH引脚输出。数据位P7最先被移出,接着是P6,以此类推,直到P0被移出。通过监测QH引脚并同步CLK信号,可以逐位读取并行输入的数据。

QH (引脚7): 串行数据反向输出(低电平有效)。此引脚提供QH引脚的非门输出。它与QH的逻辑状态相反。虽然不是所有应用都必需,但在某些特定电路设计中,提供反向输出可以简化外部逻辑。

3. 工作原理概述

74HC165的工作流程可以概括为两个主要阶段:

a. 并行数据加载

要将并行数据输入到74HC165中,首先需要将**PL引脚置为低电平(0)。此时,无论CLK和CE的状态如何,并行输入引脚P0到P7上的数据会立即被加载到内部的8位寄存器中。一旦数据加载完成,PL**引脚应立即恢复到高电平(1),以防止在移位过程中意外加载新的数据。这个过程是异步的,意味着它不依赖于时钟信号。

b. 串行数据移位

在并行数据加载完成后,并且**PL引脚恢复到高电平后,芯片就可以开始进行串行移位操作了。要使能移位功能,CE引脚必须保持为低电平(0)。此时,每当CLK**引脚接收到一个有效的时钟脉冲(通常是上升沿),内部寄存器中的数据就会向右(从P0向P7的方向,然后从P7移出QH)移动一位。

具体来说,每次时钟脉冲,寄存器中的最高位数据(当前在P7位置的数据)会通过QH引脚输出。同时,次高位的数据会移动到最高位的位置,依此类推,直到P0的数据移动到P1的位置。为了读取全部8位数据,需要发送8个连续的时钟脉冲。在移位的过程中,最低位(P0)通常会被填充为0(具体行为可能因制造商和数据手册而异,但通常移位寄存器会从一端移入0或上次移位的结果)。

数据输出顺序

需要特别注意的是,74HC165将并行输入的数据从P7到P0依次移出QH。这意味着,如果您输入了8位数据(例如D7 D6 D5 D4 D3 D2 D1 D0),在进行8个时钟脉冲后,您将从QH依次读取到D7, D6, D5, D4, D3, D2, D1, D0。这在与微控制器或其他串行设备通信时,需要特别注意数据的位顺序。

4. 典型应用场景

74HC165由于其简单而有效的功能,在许多数字电路设计中都有广泛应用:

输入扩展: 微控制器的GPIO引脚数量有限,通过使用74HC165,可以将多个并行输入(如键盘矩阵、传感器阵列)转换为串行数据,只用少数几个微控制器引脚即可读取,从而大大扩展输入能力。例如,将16个开关连接到两片74HC165,再通过SPI或其他串行协议与微控制器通信,大大节省了I/O口。

数据采集: 在需要同时采样多路并行数据,并将其以串行方式传输给主控制器进行处理时,74HC165是理想的选择。例如,多路模拟量通过ADC转换成并行数字量后,再通过74HC165串行发送。

通信接口: 作为串行通信协议(如SPI)的一部分,74HC165可以作为从设备,接收并行数据并将其转换为串行流发送给主设备。它常与74HC595(串行输入/并行输出移位寄存器)配对使用,实现全双工的并行到串行和串行到并行的数据转换。

LED显示驱动: 虽然不如74HC595直接用于LED驱动常见,但74HC165可以用于读取多个按钮的状态,然后将这些状态串行传输给微控制器,再由微控制器控制LED显示。

线缆节约: 在长距离数据传输中,使用74HC165将并行数据转换为串行数据可以显著减少所需的传输线数量,从而降低线缆成本和布线复杂性,并减少信号干扰的可能性。

数字开关阵列读取: 当有大量开关或按钮需要读取状态时,例如在复杂的控制面板上,74HC165可以将这些开关的并行状态转换成串行数据流,方便微控制器进行扫描和处理。

5. 与微控制器连接示例

连接74HC165与微控制器(如Arduino或STM32)通常需要以下几个引脚:

74HC165 VCC -> 微控制器 VCC

74HC165 GND -> 微控制器 GND

74HC165 P0-P7 -> 待读取的并行输入源

74HC165 PL -> 微控制器 GPIO (用于加载数据)

74HC165 CE -> 微控制器 GPIO (通常连接到GND,或用于使能/禁用时钟)

74HC165 CLK -> 微控制器 GPIO (时钟输出)

74HC165 QH -> 微控制器 GPIO (数据输入)

时序要求

在使用74HC165时,严格遵守其时序图至关重要。这包括:

加载脉冲宽度(tPLW): $overline{PL}$引脚保持低电平的时间,必须足够长以确保数据被正确加载。

数据保持时间(tsu(D)): 数据在$overline{PL}$上升沿之前必须保持稳定的时间。

时钟脉冲宽度(tCLW): CLK脉冲的高电平和低电平持续时间。

数据建立时间(tsu(CE)): CE引脚在CLK有效沿之前必须稳定的时间。

传播延迟(tpd): 从CLK有效沿到QH输出数据有效的时间。

这些时序参数在74HC165的数据手册中都有详细说明,确保微控制器输出的控制信号满足这些要求是实现可靠通信的关键。

6. 总结

74HC165是一款功能强大且易于使用的并行输入、串行输出移位寄存器。通过其简单的引脚接口和明确的工作原理,它为数字电路设计提供了高效的数据转换解决方案。无论是扩展输入、数据采集还是构建串行通信链路,74HC165都能发挥其独特的作用,帮助工程师更有效地管理和传输数据。深入理解其引脚功能、工作时序和应用场景,将有助于您在各种电子项目中充分利用其优势。

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

相关资讯

:

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)