n25q128a13ese40f芯片资料

1

1

拍明芯城

拍明芯城

美光N25Q128A13ESE40F串行NOR闪存芯片深度解析

美光(Micron)N25Q系列闪存产品以其高性能、高可靠性和灵活性在嵌入式系统、消费电子、工业控制和汽车电子等领域得到广泛应用。其中,N25Q128A13ESE40F作为该系列中的一款128兆位(Mbit)串行NOR闪存,凭借其卓越的特性,如高速SPI接口、多I/O支持、执行就地(XiP)模式以及丰富的保护机制,成为了许多复杂系统设计的理想选择。本文将对N25Q128A13ESE40F芯片进行全面、深入的剖析,旨在为工程师和技术爱好者提供一份详尽的参考资料。

第一章 芯片概述与核心特性

N25Q128A13ESE40F是美光推出的一款128Mbit(兆位)串行NOR闪存芯片。它采用先进的3V技术,并支持多种I/O模式,包括标准的单I/O SPI、双I/O SPI和四I/O SPI,极大地提升了数据传输带宽和系统吞吐量。该芯片特别针对需要快速启动和高性能代码执行的应用场景进行了优化,其执行就地(Execute-in-Place, XiP)功能允许处理器直接从闪存中读取代码并执行,无需将代码首先加载到RAM中,从而显著减少了系统启动时间并降低了对RAM容量的需求。

1.1 产品型号解析

N25Q128A13ESE40F的型号编码包含了丰富的芯片信息:

N25Q: 表示美光的串行NOR闪存产品系列。

128: 指芯片的存储容量为128兆位(Mbit)。128Mbit 等同于16兆字节(MB),即 16×1024×1024 字节。

A: 通常表示该系列中的特定世代或修订版本。

13: 指示芯片的核心电源电压范围,这里通常表示2.7V至3.6V的宽电压操作范围,使其能适应多种系统电源设计。

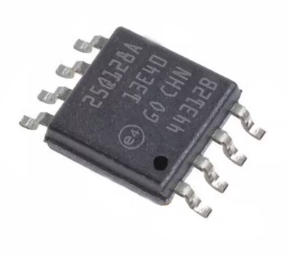

ESE: 指示封装类型为SO8W(SOP2-8,208mil宽体)。

40F: 这部分编码通常表示特定的工厂选项、温度范围或测试等级。对于N25Q128A13ESE40F,它通常指的是工业温度范围(-40°C至+85°C)和标准测试流程。

1.2 核心特性概览

N25Q128A13ESE40F集成了多项关键特性,使其在性能、灵活性和可靠性方面表现出色。

1.2.1 高速串行接口

芯片支持SPI兼容的串行总线接口,最高时钟频率可达108 MHz。通过双I/O和四I/O指令,数据吞吐量可以进一步提高,有效时钟频率可达432 MHz,这对于需要快速加载代码或处理大量数据的应用至关重要。

1.2.2 宽电压操作

N25Q128A13ESE40F设计用于2.7V至3.6V的单电源供电,这使得它能够兼容多种主控制器和系统电源轨,简化了电源管理设计。

1.2.3 执行就地(XiP)模式

XiP是该芯片的一个显著特点。它允许CPU直接从闪存中执行代码,无需预先将代码加载到RAM中。这对于启动时间敏感的应用(如汽车电子、工业自动化设备)具有决定性意义,因为它能大幅缩短系统上电到功能可用的时间。XiP模式可通过挥发性或非挥发性寄存器配置,甚至可以在上电后立即进入XiP模式。

1.2.4 灵活的存储管理

擦除粒度: 芯片支持多种擦除粒度,包括:

子扇区擦除: 4KB(千字节)统一粒度块,提供了精细的擦除控制。

扇区擦除: 64KB(千字节)统一粒度块,适用于较大规模的数据更新。

全芯片擦除: 清除整个存储器内容。

程序/擦除挂起与恢复: 支持在程序或擦除操作进行中暂停,以允许系统执行其他关键任务,然后恢复操作,提高了系统响应能力和实时性。

连续读取: 支持通过单个命令对整个存储器进行连续读取,包括快速读取、双输出快速读取、四输出快速读取以及双I/O和四I/O快速读取,进一步优化了数据访问效率。

1.2.5 强大的写保护机制

为了确保数据的完整性和安全性,N25Q128A13ESE40F提供了多层次的写保护功能:

软件写保护: 可通过挥发性锁定位(volatile lock bit)对每个64KB扇区进行软件写保护,灵活控制哪些区域可被写入。

硬件写保护: 通过五个非挥发性位(BP0, BP1, BP2, BP3, TB)定义受保护区域的大小,这种保护在上电后即生效,具有更高的安全性。

智能保护: 提供额外的智能保护机制(需特定配置或定制),进一步增强数据安全性。

1.2.6 专用OTP区域

芯片包含一个64字节的用户可锁定的一次性可编程(OTP)专用区域。这个区域可以用于存储重要的、不可更改的信息,如设备序列号、校准数据或安全密钥。一旦编程并锁定,其内容就不能再被修改,提供了高级别的安全保障。

1.2.7 电子签名与唯一ID

JEDEC标准签名: 包含JEDEC标准的2字节制造商和设备ID(BA18h),便于系统识别芯片。

唯一ID(UID): 包含17字节的只读唯一ID代码,其中包含两个额外的扩展设备ID(EDID)字节,用于识别设备工厂选项,以及14字节的定制工厂数据。这个UID为每个芯片提供了独特的身份标识,在防伪和追溯方面具有重要价值。

1.2.8 高可靠性

N25Q128A13ESE40F设计符合高可靠性标准:

擦写寿命: 每个扇区至少100,000次擦除周期。

数据保持时间: 数据保持能力超过20年。 这些指标确保了芯片在长期运行中的稳定性和可靠性,适合对数据完整性要求严苛的应用。

1.2.9 封装选项与环境合规

该芯片提供多种JEDEC标准封装,包括SO8W (SOP2-8 208mil宽体),所有封装均符合RoHS标准,满足环保要求。

第二章 存储器组织与寻址

N25Q128A13ESE40F作为一款128兆位的NOR闪存,其内部存储器被精心组织成层次结构,以便于高效的数据访问和管理。理解其存储器组织是有效利用芯片性能的关键。

2.1 存储器容量与位组织

N25Q128A13ESE40F的总存储容量为128Mbit。由于1字节(Byte)等于8位(Bit),所以其字节容量为 128 Mbits/8=16 MBytes。这意味着芯片可以存储 16×1024×1024 字节的数据。

芯片的内部存储器被组织成16M x 8的形式,即16兆个字节单元,每个字节单元可以存储8位数据。这种8位数据宽度对于大多数微控制器和处理器来说是理想的,因为它们通常以字节为基本单位进行数据处理。

2.2 扇区与子扇区结构

为了实现灵活的擦除操作和存储器管理,N25Q128A13ESE40F的存储器被划分为扇区(Sectors)和子扇区(Subsectors)。

扇区: 芯片包含256个均匀的64KB扇区。每个扇区的大小为 64×1024 字节。这是进行大规模数据擦除的基本单位。

子扇区: 每个64KB扇区又进一步划分为16个4KB的子扇区。这意味着总共有 256 sectors×16 subsectors/sector=4096 个4KB子扇区。4KB子扇区是最小的擦除单位,允许用户对存储器进行更精细的擦除操作,而无需擦除整个64KB扇区,这在更新小块数据时非常有用。

2.3 地址映射

128Mbit的存储容量需要24位的地址线来寻址每一个字节。因为 224=16,777,216 字节,这正好对应16MB的存储空间。

字节地址: 0x000000 到 0xFFFFFF。

子扇区地址: 每个子扇区的大小为4KB,即 212 字节。因此,子扇区地址由高位地址决定。

扇区地址: 每个扇区的大小为64KB,即 216 字节。因此,扇区地址由更高位的地址决定。

这种分层的存储器组织结构,结合SPI接口的特性,使得N25Q128A13ESE40F能够支持高效的随机访问和批量数据操作。

2.4 OTP区域的组织

N25Q128A13ESE40F除了主存储区外,还包含一个专门的64字节OTP(一次性可编程)区域。这个区域的地址空间与主存储区是独立的,通常通过特定的指令进行访问。

OTP地址: 通常有单独的地址范围,或者通过特殊命令和寄存器来选择访问OTP区域。

编程与锁定: OTP区域的数据可以被编程一次,然后被永久锁定,防止后续的修改。这对于存储设备唯一的识别码、加密密钥或制造批次信息等永久性数据非常有用。

2.5 寄存器区域

除了存储数据和代码的主存储器区域外,N25Q128A13ESE40F还包含多个控制和状态寄存器。这些寄存器用于配置芯片的操作模式、检查操作状态、设置写保护等。

状态寄存器(Status Register): 提供芯片的当前状态信息,例如写操作是否完成、擦除操作是否完成、写保护状态等。

非挥发性配置寄存器(Nonvolatile Configuration Register): 存储上电后保持的配置信息,如硬件写保护设置、XiP模式的默认配置等。

挥发性配置寄存器(Volatile Configuration Register): 存储临时配置信息,在断电后会丢失,用于动态调整芯片行为,例如虚拟写保护设置。

标志状态寄存器(Flag Status Register): 提供更详细的操作状态和错误标志,便于系统进行故障诊断和异常处理。

通过对这些寄存器进行读写操作,主控制器可以精细地控制N25Q128A13ESE40F的行为,并根据应用需求进行动态调整。

第三章 串行外设接口(SPI)

N25Q128A13ESE40F通过一个高速SPI兼容的串行总线接口与主控制器进行通信。SPI接口以其简单、高效的特点,在嵌入式系统中被广泛采用。该芯片支持标准SPI、双I/O SPI和四I/O SPI模式,以满足不同应用对吞吐量的需求。

3.1 SPI接口引脚定义

N25Q128A13ESE40F的SO8W封装(通常为8引脚)的典型SPI引脚包括:

SCK (Serial Clock): 串行时钟输入,由主控制器提供,用于同步数据传输。

CS# (Chip Select): 片选信号,低电平有效。当CS#为低电平时,芯片被选中并准备好接收命令;当CS#为高电平时,芯片处于待机状态,不响应任何输入。

SI / IO0 (Serial Input / Input/Output 0): 在标准SPI模式下作为串行数据输入(SI);在双I/O和四I/O模式下作为I/O线0。

SO / IO1 (Serial Output / Input/Output 1): 在标准SPI模式下作为串行数据输出(SO);在双I/O和四I/O模式下作为I/O线1。

WP# / IO2 (Write Protect / Input/Output 2): 写保护引脚,低电平有效。在标准SPI模式下,它可以用于硬件写保护;在四I/O模式下,作为I/O线2。

HOLD# / IO3 (Hold / Input/Output 3): 保持引脚,低电平有效。用于暂停当前操作,允许主控制器处理其他任务,然后恢复;在四I/O模式下,作为I/O线3。

VCC: 供电电压输入。

VSS: 接地。

需要注意的是,WP#和HOLD#引脚在多I/O模式下会复用为数据I/O线,这要求系统设计者在选择多I/O模式时,需要通过软件命令禁用这些引脚的专用功能,以避免冲突。

3.2 SPI操作模式

SPI接口支持四种基本的时钟极性(CPOL)和时钟相位(CPHA)组合,通常称为SPI模式0、1、2、3。N25Q128A13ESE40F通常兼容其中的两种或更多模式,最常见的是模式0和模式3。

模式0 (CPOL=0, CPHA=0): SCK空闲时为低电平,数据在SCK上升沿采样,在SCK下降沿输出。

模式3 (CPOL=1, CPHA=1): SCK空闲时为高电平,数据在SCK下降沿采样,在SCK上升沿输出。

确保主控制器和N25Q128A13ESE40F之间的SPI模式匹配是正确通信的基础。

3.3 数据传输协议

SPI通信通常涉及以下步骤:

片选激活: 主控制器将CS#引脚拉低,选中N25Q128A13ESE40F。

发送指令: 主控制器通过SI/IO0线发送一个8位的指令码。

发送地址(如果需要): 对于读取或编程操作,主控制器会接着发送一个24位的地址。

发送/接收数据: 根据指令的不同,芯片会接收数据(编程操作)或发送数据(读取操作)。

片选去激活: 数据传输完成后,主控制器将CS#引脚拉高,取消选中芯片。这通常标志着一次SPI事务的结束,并使芯片进入空闲状态,准备处理内部操作或接收下一个命令。

3.4 多I/O操作

N25Q128A13ESE40F支持双I/O(Dual I/O)和四I/O(Quad I/O)操作,显著提高了数据传输速率。

双I/O模式: 利用SI/IO0和SO/IO1两条数据线进行数据传输,可以将数据吞吐量提高一倍。在某些指令中,地址和数据可以并行传输,进一步减少传输时间。

四I/O模式: 进一步利用WP#/IO2和HOLD#/IO3两条数据线,总共使用四条数据线(IO0-IO3)进行并行数据传输。这可以将吞吐量提高四倍,理论上在108MHz时钟频率下实现432MHz的有效数据传输速率。四I/O模式对于需要快速加载大量代码或数据的XiP应用尤其重要。

为了进入和退出双/四I/O模式,需要发送特定的SPI指令。通常,这些模式在读取数据时效果最为显著,因为它们允许一次性传输更多的数据位。

3.5 XIP(Execute-in-Place)模式下的SPI操作

XiP模式是N25Q128A13ESE40F的一项重要功能,它允许处理器直接从闪存中执行代码,而无需将代码预先加载到RAM中。在XiP模式下,SPI接口的行为有所不同,以优化代码执行效率。

连续读取: XiP模式下的读取操作通常是连续的,一旦进入XiP读取模式,主控制器可以持续发送时钟信号,芯片会源源不断地输出数据,模拟RAM的访问方式。

灵活的Dummy Cycles: 为了适应不同的主控制器和时序要求,N25Q128A13ESE40F允许配置读取操作中的虚拟周期(Dummy Cycles)。这些虚拟周期是在地址发送后、数据输出前插入的额外时钟周期,用于确保主控制器有足够的时间来设置其输入寄存器,并等待闪存内部的数据准备好。正确配置Dummy Cycles对于优化XiP性能至关重要。

输出缓冲器配置: 芯片的输出缓冲器也可以配置,以优化信号完整性和驱动能力,适应不同的系统负载。

XiP模式的配置可以通过设置芯片的非挥发性或挥发性寄存器来实现,允许用户在系统启动时选择默认的XiP行为,或在运行时动态调整。

第四章 指令集

N25Q128A13ESE40F的强大功能通过一套丰富而灵活的指令集来实现。这些指令允许主控制器对闪存进行各种操作,包括读取、编程、擦除、状态查询、配置和安全管理。理解这些指令是正确操作N25Q128A13ESE40F的基础。

4.1 基本操作指令

4.1.1 写使能 (Write Enable - WREN)

指令码: 0x06h

描述: 在执行任何编程、擦除或写状态寄存器的操作之前,必须先发送此指令。WREN指令将内部写使能锁存器(WEL)设置为1,表示芯片已准备好进行写入操作。WEL位会在任何写入操作(如编程、擦除、写状态寄存器)完成后自动复位为0,或者在芯片上电后复位为0,以防止意外写入。

4.1.2 写禁止 (Write Disable - WRDI)

指令码: 0x04h

描述: 此指令将WEL设置为0,禁止所有编程、擦除和写状态寄存器的操作。通常在需要确保数据不被意外修改时使用。

4.1.3 读取状态寄存器 (Read Status Register - RDSR)

指令码: 0x05h

描述: 读取8位状态寄存器的内容。状态寄存器包含了芯片的当前状态信息,例如:

BUSY (位0): 指示芯片是否正在执行编程或擦除操作(1表示忙碌,0表示空闲)。

WEL (位1): 写使能锁存器状态(1表示已使能写入,0表示已禁止写入)。

BPx (位2-4): 块保护位,用于指示硬件写保护区域的大小。

TB (位5): 顶部/底部块保护位。

SRP0 (位7): 状态寄存器保护位0。

4.1.4 写入状态寄存器 (Write Status Register - WRSR)

指令码: 0x01h

描述: 写入8位状态寄存器的内容。通过此指令,可以配置块保护位(BPx, TB)以及其他一些可写位,从而实现软件写保护和硬件写保护区域的定义。在执行此指令前,需要先发送WREN指令。

4.1.5 读取数据 (Read Data - READ)

指令码: 0x03h

描述: 最基本的读取指令。主控制器发送指令码和24位地址,芯片在几个时钟周期(通常为8个时钟周期)后开始在SO线上输出数据。适用于需要低速读取或进行少量数据读取的场景。

4.1.6 快速读取 (Fast Read - FAST_READ)

指令码: 0x0Bh

描述: 相比READ指令,FAST_READ允许在更高频率下读取数据。它需要额外的虚拟周期(Dummy Cycles)在地址和数据输出之间,以给芯片内部电路足够的时间进行数据准备。主控制器发送指令码、24位地址和虚拟周期,然后芯片开始输出数据。此指令是XiP模式的基础。

4.2 高级I/O操作指令

为了提升数据吞吐量,N25Q128A13ESE40F支持双I/O和四I/O的快速读取指令。

4.2.1 双输出快速读取 (Dual Output Fast Read - DOFR)

指令码: 0x3Bh

描述: 利用SI/IO0和SO/IO1两条数据线进行数据输出。主控制器发送指令码和24位地址(通过SI/IO0),然后发送虚拟周期。之后,芯片通过IO0和IO1两条线同时输出数据,每次传输2位数据,显著提升读取速度。

4.2.2 双I/O快速读取 (Dual I/O Fast Read - DIOFR)

指令码: 0xBBh

描述: 更高效的双I/O读取模式。指令码和地址通过两条I/O线并行输入,然后是虚拟周期,最后数据通过两条I/O线并行输出。这进一步优化了整个读周期。

4.2.3 四输出快速读取 (Quad Output Fast Read - QOFR)

指令码: 0x6Bh

描述: 利用IO0、IO1、IO2(WP#)和IO3(HOLD#)四条数据线进行数据输出。主控制器发送指令码和24位地址(通过SI/IO0),然后发送虚拟周期。之后,芯片通过四条I/O线同时输出数据,每次传输4位数据,实现最高的读取吞吐量。

4.2.4 四I/O快速读取 (Quad I/O Fast Read - QIOFR)

指令码: 0xEBh

描述: 最高效的四I/O读取模式。指令码和地址通过四条I/O线并行输入,然后是虚拟周期,最后数据通过四条I/O线并行输出。这是实现最高XiP性能的关键指令。

4.3 编程操作指令

4.3.1 页编程 (Page Program - PP)

指令码: 0x02h

描述: 用于将数据编程到闪存页面中。N25Q128A13ESE40F支持256字节的页面编程。主控制器发送指令码、24位地址,然后发送最多256字节的数据。在发送数据之前,必须先发送WREN指令。编程操作完成后,芯片进入忙碌状态,可以通过RDSR指令检查BUSY位来判断编程是否完成。

4.3.2 四I/O页编程 (Quad I/O Page Program - QIPP)

指令码: 0x32h (有时也用0x38h)

描述: 利用四条I/O线并行输入数据,实现更快的页编程速度。主控制器发送指令码和24位地址(通过四I/O线),然后并行发送最多256字节的数据。在发送数据之前,必须先发送WREN指令。

4.4 擦除操作指令

擦除操作会清除指定区域内的所有位,将其设置为逻辑1(0xFF)。

4.4.1 子扇区擦除 (Subsector Erase - SSE)

指令码: 0x20h

描述: 擦除一个4KB的子扇区。主控制器发送指令码和该子扇区内的任何一个地址。在执行此指令前,必须先发送WREN指令。擦除操作会持续一段时间,可以通过RDSR指令检查BUSY位。

4.4.2 扇区擦除 (Sector Erase - SE)

指令码: 0xD8h

描述: 擦除一个64KB的扇区。主控制器发送指令码和该扇区内的任何一个地址。在执行此指令前,必须先发送WREN指令。

4.4.3 全芯片擦除 (Bulk Erase - BE)

指令码: 0xC7h 或 0x60h

描述: 擦除整个芯片的所有数据。这是耗时最长的操作。在执行此指令前,必须先发送WREN指令。

4.5 挂起与恢复操作指令

4.5.1 程序/擦除挂起 (Program/Erase Suspend - PES)

指令码: 0x75h

描述: 当芯片正在执行页编程或扇区/子扇区擦除操作时,可以发送此指令暂停当前操作。这允许主控制器在闪存操作期间访问其他闪存区域或执行其他任务。挂起后,芯片仍处于忙碌状态,但可以通过读取命令访问非正在操作的区域。

4.5.2 程序/擦除恢复 (Program/Erase Resume - PER)

指令码: 0x7Ah

描述: 在程序或擦除操作被挂起后,发送此指令可以恢复之前暂停的操作。

4.6 识别与安全指令

4.6.1 读取ID (Read ID - RDID)

指令码: 0x9Fh

描述: 读取JEDEC标准的制造商ID(Manufacturer ID)和设备ID(Device ID)。对于美光N25Q系列,制造商ID通常是0x20,设备ID根据具体型号而定,对于N25Q128A,可能是0xBA18。

4.6.2 读取电子签名 (Read Electronic Signature - RES)

指令码: 0xABh

描述: 读取N25Q系列特有的电子签名,通常包含制造商ID、设备类型和容量信息。

4.6.3 读取唯一ID (Read Unique ID - RUID)

指令码: 0x4Bh

描述: 读取芯片的17字节唯一ID。这个ID是每个芯片独有的,包含了工厂数据和扩展设备ID,可用于产品追溯和防伪。

4.6.4 读取OTP区域 (Read OTP Area)

指令码: 0x4Bh (与RUID相同指令,但通常通过地址区分)

描述: 用于读取64字节OTP区域的内容。

4.6.5 编程OTP区域 (Program OTP Area)

指令码: 0x42h

描述: 用于向OTP区域编程数据。在编程后,可以通过后续指令或熔丝位将OTP区域锁定,使其内容永久不可修改。

4.6.6 软件复位 (Software Reset)

指令码: 0x66h (复位使能) 紧接着 0x99h (复位)

描述: 允许通过软件命令对芯片进行复位,使其回到上电状态。这对于系统故障恢复或重新初始化芯片非常有用。

4.7 配置寄存器指令

除了状态寄存器,N25Q128A13ESE40F还有其他配置寄存器用于高级设置。

4.7.1 读取非挥发性配置寄存器 (Read Nonvolatile Configuration Register - RDNVCR)

指令码: 0xB5h

描述: 读取非挥发性配置寄存器的内容。此寄存器存储了在芯片上电后仍然保留的配置选项,如默认的XiP模式设置、硬件写保护区域的详细配置等。

4.7.2 写入非挥发性配置寄存器 (Write Nonvolatile Configuration Register - WRNVCR)

指令码: 0xB1h

描述: 写入非挥发性配置寄存器的内容。此操作通常需要先发送WREN指令。修改此寄存器会影响芯片上电后的默认行为。

4.7.3 读取挥发性配置寄存器 (Read Volatile Configuration Register - RDVCR)

指令码: 0x85h

描述: 读取挥发性配置寄存器的内容。此寄存器存储了临时配置选项,在断电后会丢失。例如,可以在运行时临时调整XiP模式的虚拟周期数量或输出驱动强度。

4.7.4 写入挥发性配置寄存器 (Write Volatile Configuration Register - WRVCR)

指令码: 0x81h

描述: 写入挥发性配置寄存器的内容。此操作通常需要先发送WREN指令。

4.7.5 清除标志状态寄存器 (Clear Flag Status Register - CLFSR)

指令码: 0x50h

描述: 清除标志状态寄存器中的某些标志位,例如擦除错误标志、编程错误标志等。这对于在处理错误后重新启动操作非常重要。

4.7.6 读取标志状态寄存器 (Read Flag Status Register - RDFSR)

指令码: 0x70h

描述: 读取标志状态寄存器的内容。此寄存器提供了更详细的错误和状态信息,例如编程错误、擦除错误、擦除/编程暂停状态等。

4.8 编程和擦除操作时序与状态监控

所有编程和擦除操作都是耗时的。在这些操作期间,芯片的BUSY位(状态寄存器中的位0)将被置1。主控制器必须轮询BUSY位直到其变为0,才能确定操作完成。

编程时间: 页编程时间通常在毫秒级(如0.7ms)。

擦除时间: 扇区擦除时间通常在几十到几百毫秒级(如64KB扇区擦除可能需要150ms),而全芯片擦除可能需要数秒到数十秒(如30秒)。

正确的时序控制和状态监控对于确保数据完整性至关重要。在编程或擦除操作进行期间,除了读取状态寄存器外,所有其他操作(包括读取数据)都将被阻塞,直到当前操作完成。

第五章 写保护机制与安全特性

数据完整性和安全性是闪存芯片设计的核心考量。N25Q128A13ESE40F提供了多层次的写保护机制,以防止数据被意外或恶意修改。

5.1 硬件写保护

N25Q128A13ESE40F的硬件写保护功能主要通过WP#引脚和状态寄存器中的**块保护位(BPx)以及顶部/底部块保护位(TB)**来实现。

5.1.1 WP# 引脚

当WP#引脚被拉低(逻辑0)时,并且状态寄存器中的SRP0(状态寄存器保护位0)也设置为1时,状态寄存器本身将受到硬件保护,不能被写入。这意味着,如果状态寄存器被保护,通过WRSR指令修改BPx和TB位将无效。这为最关键的保护设置提供了额外的安全层。

在四I/O模式下,WP#引脚被复用为IO2,其硬件写保护功能需要通过软件禁用。

5.1.2 块保护位 (BP0, BP1, BP2, BP3)

状态寄存器中的BP0、BP1、BP2、BP3是非挥发性位,它们结合顶部/底部块保护位(TB)共同定义了受硬件保护的存储区域。这些位的值决定了存储器中从最低地址(或最高地址,取决于TB位)开始的一个连续块的写保护状态。

配置: BPx位可以通过WRSR指令进行配置。一旦这些位被设置,它们将保留其值,直到被再次修改。如果SRP0被设置并且WP#为低电平,这些位将无法被修改。

保护区域: 下表是一个简化示例,说明BPx位如何定义保护区域(实际数据手册会有详细表格):

| BP3 | BP2 | BP1 | BP0 | 保护区域(示例,具体请参考数据手册) |

| 0 | 0 | 0 | 0 | 无保护 |

| 0 | 0 | 0 | 1 | 保护最顶部的1/64(2个扇区) |

| 1 | 1 | 1 | 1 | 保护整个芯片 |

TB位是一个非挥发性位,它决定了由BPx位定义的写保护区域是从存储器的最高地址开始(TB=1),还是从最低地址开始(TB=0)。这提供了极大的灵活性,可以保护启动代码(通常位于最低地址)或用户数据(可能位于最高地址)。

硬件写保护的优点是其设置在断电后仍然有效,并且可以通过外部引脚或组合内部寄存器提供额外的安全性,特别适合保护固件代码或重要配置参数。

5.2 软件写保护

N25Q128A13ESE40F还提供了更灵活的软件写保护机制,主要通过**挥发性锁定位(Volatile Lock Bit)和非挥发性配置寄存器(NVCR)**来实现。

5.2.1 挥发性锁定位

每个64KB扇区都有一个对应的挥发性锁定位。这些锁定位存在于内部RAM中,因此在断电后会丢失。

配置: 主控制器可以通过特定的指令(如WRVCR或相关命令)来设置或清除这些锁定位,从而在运行时动态地对单个或多个扇区进行写保护。

用途: 这种保护适用于在系统运行期间需要临时保护某些数据区域,但又不需要永久保护的场景。例如,当系统正在更新一部分固件时,可以临时锁定其他部分,防止意外修改。

5.2.2 非挥发性配置寄存器 (NVCR)

NVCR中包含一些位,可以影响写保护机制的默认行为,例如配置在XiP模式下或上电后的初始保护状态。这些位也是非挥发性的,即在断电后保留其设置。

锁定寄存器 (Lock Register): N25Q128A可能包含一个特殊的锁定寄存器,用于进一步锁定状态寄存器和配置寄存器,防止其被修改。这为芯片的关键配置提供了终极保护。

5.3 智能保护机制

除了标准的硬件和软件写保护外,美光N25Q系列芯片可能还提供了一些“智能保护”功能,这些功能通常在数据手册中以高级特性或特殊定制选项的形式提及。这些可能包括:

区域锁定: 允许更细粒度的锁定,例如将某些子扇区指定为永久只读。

安全认证: 结合加密功能,只有通过特定认证的命令或数据才能对芯片进行写入或擦除操作。

电压保护: 当电源电压超出安全范围时,自动禁止写入操作。

5.4 OTP区域的安全性

N25Q128A13ESE40F的64字节OTP区域本身就是一个重要的安全特性。

一次性编程: OTP区域只能被编程一次。一旦数据写入,它就不能被擦除或再次编程。

永久锁定: 在编程数据后,可以通过特定的指令或熔丝位将OTP区域永久锁定。一旦锁定,该区域将变为只读,任何试图修改其内容的尝试都将被忽略或导致错误。

应用: OTP区域非常适合存储安全密钥、设备序列号、产品批次信息、校准数据或任何需要永久性和不可更改性的关键信息。这对于知识产权保护、产品识别和安全启动等应用至关重要。

5.5 数据保持与擦写寿命

这些参数直接关系到芯片的长期可靠性和数据完整性:

数据保持时间(Data Retention): N25Q128A13ESE40F保证数据保持超过20年。这意味着即使在没有电源的情况下,芯片中的数据也能在很长一段时间内保持有效。

擦写寿命(Endurance): 每个扇区至少100,000次擦除周期。这是一个关键指标,表明芯片在反复擦写后仍能保持其功能。对于频繁更新数据的应用,需要仔细考虑擦写寿命,并可能需要实施磨损均衡(wear-leveling)算法来延长闪存的整体寿命。

通过结合上述多种写保护机制,N25Q128A13ESE40F能够为不同应用场景提供高度灵活和可靠的数据保护方案,从防止意外修改到抵御恶意攻击,都能提供坚实的保障。

第六章 电气特性与时序

了解N25Q128A13ESE40F的电气特性和时序参数对于正确的硬件设计和软件驱动开发至关重要。这些参数定义了芯片在不同操作条件下的性能和行为。

6.1 绝对最大额定值

绝对最大额定值是芯片可以承受的极限值,超出这些值可能会导致芯片永久性损坏。在设计电路时,必须确保任何信号或电源电压都不会超过这些限制。

VCC (电源电压): -0.6V 到 +4.0V

所有I/O引脚电压: -0.6V 到 VCC+0.5V (最大+4.0V)

存储温度: -65°C 到 +150°C

焊接温度: 260°C (符合JEDEC标准)

ESD (静电放电) 保护:

人体模型(HBM): 2000V

机器模型(MM): 200V

充电器件模型(CDM): 500V

重要提示: 即使芯片在绝对最大额定值内,也不应长时间在此条件下工作,否则会影响芯片的可靠性。应始终在推荐的操作条件范围内使用。

6.2 推荐操作条件

推荐操作条件是芯片能够保证正常功能和性能的范围。

电源电压 (VCC): 2.7V 到 3.6V (通常标称3V)

工作温度 (TA): -40°C 到 +85°C (工业级)

对于特殊型号,可能存在更宽的温度范围,如汽车级(-40°C到+125°C)。N25Q128A13ESE40F中的"40F"通常指示工业温度范围。

6.3 直流电气特性

直流电气特性描述了芯片在稳态条件下的电流和电压行为。

静态电流 (IDD_STANDBY): 芯片在待机模式下消耗的电流,通常非常低,如几微安(µA),有助于延长电池寿命。

读取电流 (IDD_READ): 芯片在执行读取操作时消耗的电流,通常在几毫安(mA)范围。例如,快速读取可能消耗20mA。

编程电流 (IDD_PROG): 芯片在编程操作期间消耗的电流,通常高于读取电流。

擦除电流 (IDD_ERASE): 芯片在擦除操作期间消耗的电流,也通常较高。

输入高电平电压 (VIH): 识别为逻辑高电平的最小输入电压。

输入低电平电压 (VIL): 识别为逻辑低电平的最大输入电压。

输出高电平电压 (VOH): 输出逻辑高电平时的最小电压。

输出低电平电压 (VOL): 输出逻辑低电平时的最大电压。

输入泄漏电流 (ILI): 未被驱动的输入引脚上的微小电流。

这些参数对于电源设计、信号完整性分析和I/O接口匹配至关重要。

6.4 交流电气特性与时序

交流电气特性描述了芯片在动态操作(如时钟频率、数据建立/保持时间)下的性能。这些参数对于确保SPI总线通信的正确时序至关重要。

6.4.1 时钟频率

fSCK: SPI串行时钟频率。N25Q128A13ESE40F通常支持高达108 MHz的SCK频率。在双I/O和四I/O模式下,有效数据速率可以达到 2×fSCK 或 4×fSCK。

6.4.2 片选时序

tCS (Chip Select setup time): CS#信号在SCK第一个上升沿到来之前必须保持低电平的时间。

tCH (Chip Select hold time): CS#信号在SCK最后一个时钟沿之后必须保持低电平的时间。

tSHSL (SCK high before CS# low): CS#从高到低之前,SCK必须保持高电平的时间。

tSLCH (CS# low before SCK high): CS#从低到高之前,SCK必须保持低电平的时间。

6.4.3 数据输入/输出时序

tDI (Data In setup time): 数据输入在SCK时钟沿到来之前必须保持稳定的时间。

tDH (Data In hold time): 数据输入在SCK时钟沿之后必须保持稳定的时间。

tV (Clock to output valid): 从SCK时钟沿到数据输出有效的时间。

tHO (Output hold time): 数据输出在SCK时钟沿之后保持有效的时间。

tHZ (Output high-impedance time): SO(或IOx)从低电平有效切换到高阻态的时间,通常在CS#被拉高后发生。

6.4.4 复位时序

tRST (Reset pulse width): 软件复位指令的有效脉冲宽度。

tREADY (Reset to ready): 从复位完成到芯片准备好接受命令的时间。

6.4.5 编程/擦除时间

这些参数在指令集章节已提及,但作为交流电气特性的一部分,它们是操作延迟的关键指标。

tPP (Page Program time): 单页编程所需时间。

tSSE (Subsector Erase time): 4KB子扇区擦除所需时间。

tSE (Sector Erase time): 64KB扇区擦除所需时间。

tBE (Bulk Erase time): 全芯片擦除所需时间。

tSUS (Suspend time): 从发出挂起指令到操作真正暂停的时间。

tRES (Resume time): 从发出恢复指令到操作真正恢复的时间。

所有这些时序参数都会根据电源电压和工作温度的变化而有所不同。在设计时,应始终参考数据手册中提供的最小和最大时序值,并留出足够的裕量。

6.5 热特性

热阻 (Thermal Resistance):

RθJA (结到环境的热阻): 描述芯片内部结温与外部环境温度之间的温升关系。

RθJC (结到外壳的热阻): 描述芯片内部结温与封装外壳温度之间的温升关系。 这些参数对于评估芯片在不同工作负载下的发热情况以及是否需要散热措施非常重要,尤其是在高温环境下或高频持续工作时。

6.6 功耗管理

N25Q128A13ESE40F具备低功耗特性,以适应电池供电或功耗敏感的应用。

深度掉电模式 (Deep Power-Down Mode): 通过发送特定指令进入此模式,芯片功耗会降至最低(通常为几百纳安),几乎不消耗电流,但芯片不响应任何命令,唤醒时间较长。

待机模式 (Standby Mode): 在没有片选信号或空闲时,芯片自动进入待机模式,功耗较低,响应命令的速度快。

通过合理利用这些功耗模式,系统可以根据实际需求在性能和功耗之间取得最佳平衡。例如,在长时间不访问闪存时进入深度掉电模式,在短时间间隔访问时保持待机模式。

第七章 典型应用场景

美光N25Q128A13ESE40F因其高性能、大容量、XiP功能和强大的保护机制,在广泛的嵌入式和消费电子应用中表现出色。

7.1 嵌入式系统启动存储

N25Q128A13ESE40F非常适合作为嵌入式系统的启动代码存储器。

快速启动: XiP功能允许处理器直接从闪存中执行启动代码(如BIOS、RTOS内核或Bootloader),无需等待代码从闪存传输到RAM,从而显著缩短了设备从上电到可操作状态的时间。这对于需要即时响应的设备(如汽车信息娱乐系统、工业控制器、智能家电)至关重要。

代码更新: 结合其扇区/子扇区擦除和页编程能力,固件更新可以高效进行。系统可以在运行时更新部分固件,同时不影响其他关键功能的执行(通过挂起/恢复操作)。

安全启动: 利用OTP区域存储安全密钥或启动校验码,并结合硬件写保护,可以实现安全启动流程,确保只有经过认证的固件才能被执行,防止恶意篡改。

7.2 消费电子产品

在各种消费电子设备中,N25Q128A13ESE40F可以提供高容量、高可靠性的存储解决方案。

智能电视和机顶盒: 存储操作系统、应用程序、用户配置和媒体内容。其高速读取能力确保了流畅的用户体验和快速的应用加载。

路由器和网络设备: 存储固件、网络配置、日志文件。高可靠性和长数据保持时间对于需要长时间稳定运行的网络设备非常重要。

智能家居设备: 如智能音箱、智能门锁、智能照明控制器等,用于存储固件、设备配置和OTA(Over-The-Air)更新包。

数码相机和摄像机: 存储固件和用户设置,支持快速启动和图片/视频处理。

7.3 工业控制与自动化

工业环境对设备的可靠性和数据完整性有着极高的要求,N25Q128A13ESE40F能够很好地满足这些需求。

PLC (可编程逻辑控制器): 存储控制程序、配置数据和生产参数。其高擦写寿命和数据保持能力确保了在恶劣工业环境中的长期稳定运行。

HMI (人机界面): 存储操作界面、图像资源、系统日志和配置数据。快速启动和数据访问对于操作员的即时响应至关重要。

工业物联网 (IIoT) 网关: 存储操作系统、边缘计算应用程序和传感器数据。安全特性可用于保护敏感的工业数据。

智能仪表和传感器: 存储固件和校准数据,提供可靠的数据记录功能。

7.4 汽车电子

汽车电子系统对器件的温度范围、可靠性、安全性和启动时间有非常严格的要求,N25Q128A13ESE40F符合这些高标准。

车载信息娱乐系统: 存储操作系统、导航地图、多媒体内容和应用程序。高速读取和XiP功能确保了系统快速启动和流畅的用户体验。

高级驾驶辅助系统 (ADAS): 存储控制算法、传感器校准数据和地图信息。其高可靠性对于确保车辆安全至关重要。

仪表盘和显示器: 存储固件、图形界面和车辆信息。

车身控制模块 (BCM): 存储控制逻辑和配置参数。

发动机控制单元 (ECU): 作为备份存储或配置存储,其高可靠性至关重要。

7.5 医疗设备

在医疗设备中,数据完整性和系统可靠性是生命攸关的,N25Q128A13ESE40F能够提供满足这些要求的存储解决方案。

便携式医疗设备: 存储固件、用户界面和患者数据。低功耗特性有助于延长电池寿命。

诊断设备: 存储校准数据、程序和结果。

监测设备: 存储日志数据和报警配置。

7.6 数据日志与数据存储

虽然NOR闪存通常用于存储代码和配置数据,但N25Q128A13ESE40F的128Mbit容量和页编程能力也使其适用于中小型数据日志应用。

传感器数据记录: 存储温度、湿度、压力等传感器数据。

事件日志: 记录系统事件、错误和操作历史。 为了延长芯片寿命,在数据日志应用中,通常需要结合磨损均衡算法,以确保所有扇区的擦写次数均匀分布。

7.7 固件更新与OTA

N25Q128A13ESE40F是实现固件空中下载(OTA)更新的理想选择。

系统可以将新的固件包下载到芯片的空闲区域。

利用擦除/编程挂起和恢复功能,可以在不中断关键系统功能的情况下,分阶段地写入新固件。

通过软件或硬件写保护机制,可以确保在更新过程中,当前正在运行的固件不会被破坏,并在更新完成后无缝切换到新固件。

OTP区域可用于存储设备版本或更新状态,确保更新的正确性。

7.8 其他新兴应用

随着物联网(IoT)和人工智能(AI)边缘计算的兴起,N25Q128A13ESE40F的应用范围将进一步扩大。

AI边缘设备: 存储轻量级AI模型和推理代码。

可穿戴设备: 存储操作系统和用户数据,要求低功耗和紧凑封装。

总而言之,N25Q128A13ESE40F凭借其全面的功能集和优越性能,为需要高性能、高可靠性和安全性的嵌入式存储应用提供了灵活且强大的解决方案。

第八章 封装信息

芯片的封装对于其在PCB上的集成、散热性能、可靠性以及最终产品的尺寸和成本都至关重要。N25Q128A13ESE40F的"ESE"后缀指示其采用**SO8W (SOP2-8, 208mil body width)**封装。

8.1 SO8W封装概述

SO8W (Small Outline Package, 8-pin, Wide body) 是一种标准的表面贴装(SMD)封装,通常用于集成电路。

8引脚: 封装有8个外部引脚,这些引脚从封装两侧延伸出来,呈鸥翼形(gull-wing),便于焊接在PCB表面。

208mil body width: "W"代表“宽体”(Wide),与"N"(窄体)相对。208mil(约5.3mm)是封装本体的宽度,这比窄体SOIC(通常为150mil)更宽,提供了更好的散热性能和更大的内部芯片空间。

标准间距: 引脚间距通常为1.27mm (50mil)。

8.2 SO8W封装的特点与优势

成熟且广泛应用: SO8W是一种非常成熟且广泛使用的封装类型,兼容性好,供应链稳定,相关工具和生产设备普及。

成本效益: 相对于更复杂或更小的封装,SO8W通常具有较低的成本,适用于批量生产。

易于焊接: 较大的引脚间距和鸥翼形引脚使其更容易进行手工焊接或自动化焊接(如回流焊),也方便了目视检查和返修。

尺寸适中: 虽然不像更小的DFN/QFN封装那样紧凑,但SO8W的尺寸对于许多空间受限的应用仍然是可接受的,并在尺寸和易用性之间取得了良好的平衡。

散热性能: 相对于窄体SOIC,宽体SO8W提供了更大的封装表面积,有助于芯片在工作时更好地散发热量,尤其是在较高频率或持续读写操作下。

8.3 封装尺寸与引脚排列

详细的封装尺寸(长度、宽度、高度、引脚间距、引脚宽度等)和引脚排列图会在芯片的完整数据手册中提供。在PCB设计阶段,工程师需要严格参照这些尺寸来设计封装焊盘,以确保可靠的焊接和电气连接。

例如,对于SO8W封装,引脚排列通常遵循一定的行业标准,例如引脚1通常有标记点或凹槽来指示方向。SPI接口的引脚分配(如SCK, CS#, SI/IO0, SO/IO1, WP#/IO2, HOLD#/IO3, VCC, VSS)会根据具体型号和封装进行映射。

8.4 封装材料与环境合规性

封装材料: 通常由环氧树脂模塑料(epoxy molding compound)制成,具有良好的绝缘性和机械保护性。内部连接使用金线或铜线。

RoHS compliant: N25Q128A13ESE40F及其SO8W封装均符合RoHS(限制使用有害物质)指令,不含铅、汞、镉、六价铬、多溴联苯和多溴二苯醚等有害物质,满足全球环保法规要求。

MSL (Moisture Sensitivity Level) 等级: 芯片通常会有一个MSL等级,指示其对潮湿的敏感程度。这对于存储和处理芯片至关重要,以避免在回流焊过程中因封装内部水分膨胀而导致的分层或爆米花效应。

8.5 存储和处理注意事项

防静电 (ESD): 闪存芯片对静电非常敏感。在处理N25Q128A13ESE40F时,必须采取严格的防静电措施,包括佩戴防静电腕带、使用防静电台垫、穿防静电服等,以防止静电放电损坏芯片。

潮湿敏感性: 芯片在长时间暴露于空气中后会吸收水分。在进行回流焊前,可能需要进行烘烤以去除水分,防止焊接过程中发生问题。请参照数据手册中的MSL等级和相关处理指南。

储存条件: 芯片应储存在干燥、控温的环境中,并使用防潮袋密封。

正确理解和处理芯片的封装信息是确保产品可靠性和制造效率的关键环节。

第九章 编程、擦除与测试

对N25Q128A13ESE40F进行编程、擦除和测试是其在生产和维护环节中不可或缺的步骤。这通常需要专用的编程器或通过系统内(In-System Programming, ISP)方式进行。

9.1 编程操作

对N25Q128A13ESE40F进行编程,即写入数据,需要遵循特定的流程和时序要求。

准备阶段: 确保芯片上电并处于稳定状态。检查VCC电压是否在推荐范围内。

写使能: 每次编程操作(页编程)前,必须先发送**写使能(WREN, 0x06h)**指令。这将设置芯片内部的WEL位。

发送编程指令: 发送**页编程(Page Program, 0x02h)指令,或四I/O页编程(Quad I/O Page Program, 0x32h)**指令。

发送地址: 紧接着发送24位的目标地址,该地址必须是256字节页的起始地址。

发送数据: 随后发送最多256字节的数据。数据会按照地址顺序写入到页中。

片选去激活: 数据发送完毕后,将CS#信号拉高。芯片会进入忙碌状态,执行内部编程操作。

状态查询: 主控制器应持续轮询状态寄存器(Status Register, RDSR, 0x05h),检查BUSY位(位0)。当BUSY位从1变为0时,表示页编程操作已完成。

错误检查: 可以通过读取**标志状态寄存器(Flag Status Register, RDFSR, 0x70h)**来检查是否有编程错误发生。

注意事项:

页编程操作只能将数据从1设置为0(即从0xFF修改为特定值)。如果目标位已经是0,则无法再次修改为1。要将0修改为1,必须先进行擦除操作。

不允许跨页编程,即一个页编程操作不能写入超过一个256字节的页。如果数据跨页,需要分成多个页编程操作。

在编程过程中,芯片可能不允许其他操作(如读取),直到编程完成或被挂起。

9.2 擦除操作

擦除操作会将指定区域的所有位设置为逻辑1(即0xFF)。

准备阶段: 确保芯片上电并处于稳定状态。

写使能: 每次擦除操作(子扇区、扇区、全芯片)前,必须先发送**写使能(WREN, 0x06h)**指令。

发送擦除指令:

子扇区擦除(Subsector Erase, 0x20h): 擦除一个4KB子扇区。

扇区擦除(Sector Erase, 0xD8h): 擦除一个64KB扇区。

全芯片擦除(Bulk Erase, 0xC7h 或 0x60h): 擦除整个芯片。

发送地址(对于子扇区/扇区擦除): 对于子扇区或扇区擦除,发送该子扇区/扇区内的任何一个地址。对于全芯片擦除,无需发送地址。

片选去激活: CS#信号拉高。芯片会进入忙碌状态,执行内部擦除操作。

状态查询: 持续轮询**状态寄存器(RDSR, 0x05h)**的BUSY位,直到其变为0。

错误检查: 读取**标志状态寄存器(RDFSR, 0x70h)**检查是否有擦除错误。

注意事项:

擦除操作是不可逆的,一旦擦除,数据将丢失。

擦除时间远长于编程时间,尤其是全芯片擦除,可能需要几十秒。在擦除过程中,系统应避免访问被擦除的区域。

在擦除过程中,芯片可能不允许其他操作(如读取),直到擦除完成或被挂起。

9.3 程序/擦除挂起与恢复

N25Q128A13ESE40F支持在编程或擦除操作进行中暂停,以允许系统执行其他任务,如响应中断、读取其他非被操作区域的数据。

发出挂起指令: 当芯片处于忙碌状态(编程或擦除中)时,发送**程序/擦除挂起(Program/Erase Suspend, 0x75h)**指令。

等待挂起完成: 轮询**标志状态寄存器(RDFSR, 0x70h)**中的Suspend位(如果存在,或者通过BUSY位和特定状态位组合判断),直到操作挂起。

执行其他任务: 一旦操作挂起,系统可以读取闪存中未被挂起操作影响的区域的数据,或执行其他SPI操作。

恢复操作: 当需要恢复之前挂起的操作时,发送**程序/擦除恢复(Program/Erase Resume, 0x7Ah)**指令。

等待恢复完成: 轮询**状态寄存器(RDSR, 0x05h)**的BUSY位,直到它再次变为0(表示整个编程/擦除操作完成)。

注意事项:

挂起操作并不能完全停止对内部阵列的访问,它只是暂停了主编程/擦除循环。在挂起期间,只能访问未受影响的区域。

挂起和恢复操作会引入额外的开销,应根据系统实时性需求权衡使用。

9.4 芯片测试与验证

在生产和系统集成过程中,需要对N25Q128A13ESE40F进行功能和性能测试。

功能测试: 验证芯片的各个指令是否按照预期工作,包括读、写、擦除、写保护、寄存器读写等。

性能测试: 测量芯片在不同时钟频率、电压和温度下的读取、编程、擦除时间是否符合数据手册规定。特别是XiP模式下的读取吞吐量是关键性能指标。

数据完整性测试: 通过写入特定数据模式(如全0、全1、交替01等)并回读验证,确保数据的准确性和完整性。

擦写寿命测试: 在研发和认证阶段,需要对芯片进行大量的擦写循环测试,以验证其擦写寿命是否达到100,000次。

数据保持测试: 长期暴露在高温下或进行高压烘烤等加速老化测试,以验证数据保持能力是否超过20年。

电源完整性测试: 监控VCC引脚的电压稳定性,确保在突发电流需求(如编程/擦除)时电源不会大幅跌落。

信号完整性测试: 使用示波器分析SPI信号的波形,检查是否存在过冲、下冲、反射或串扰等问题,确保信号质量良好,避免数据错误。

ESD/Latch-up测试: 验证芯片的静电放电和闩锁效应防护能力。

9.5 系统内编程 (In-System Programming, ISP)

N25Q128A13ESE40F支持ISP,这意味着芯片可以在焊接在PCB上后,通过系统的主控制器或一个外部编程接口进行编程。

优势: 简化了生产流程,无需预先编程芯片;方便固件更新和现场维护;降低了生产成本。

实现方式: 通常通过主控制器上的GPIO引脚模拟SPI接口,或者使用JTAG/SWD调试接口上的SPI功能来对闪存进行编程。需要开发相应的ISP驱动程序。

挑战: ISP可能会受到板级噪声、电源稳定性、信号完整性以及主控制器I/O性能的限制。在设计阶段应充分考虑这些因素。

有效的编程、擦除和测试策略对于确保产品质量和长期可靠性至关重要。

第十章 可靠性与质量

N25Q128A13ESE40F作为一款工业级闪存芯片,其可靠性和质量是确保其在各种应用中稳定运行的关键。美光作为一家领先的存储解决方案供应商,对其产品的可靠性进行了严格的验证和测试。

10.1 存储器单元可靠性

NOR闪存的可靠性主要体现在以下几个方面:

擦写循环寿命 (Endurance): 芯片的每个扇区(或子扇区)都保证至少可以承受100,000次擦写循环。这意味着在该次数范围内,闪存单元能够可靠地进行编程和擦除,而不会出现数据损坏或单元失效。对于需要频繁更新数据的应用,如日志记录或配置参数,这个指标至关重要。在实际应用中,为了最大化芯片寿命,通常会采用**磨损均衡(Wear Leveling)**算法,确保所有扇区均匀地分担擦写任务,避免某些扇区过度磨损。

数据保持时间 (Data Retention): N25Q128A13ESE40F保证数据在无电源供电的情况下能保持至少20年。这个参数通过高温烘烤等加速寿命测试进行验证。长数据保持时间对于存储关键固件、配置或校准数据至关重要,即使设备长时间断电,数据也不会丢失。

位错误率 (Bit Error Rate, BER): 虽然数据手册通常不直接给出BER,但NOR闪存的设计目标是在其整个寿命周期内保持极低的位错误率。任何在编程、擦除或读取过程中检测到的错误都会被视为不合格,并可能触发内部纠错机制(如果芯片支持)或错误标志。

10.2 封装可靠性

封装的可靠性直接影响芯片的物理耐久性和长期稳定性。

热循环 (Temperature Cycling): 芯片会经历从低温到高温的反复循环测试,以模拟产品在不同环境温度下的工作情况。这有助于评估封装材料、引线键合和内部连接在热膨胀和收缩下的应力承受能力。

高温存储寿命 (High Temperature Storage Life): 芯片在不通电的情况下长时间暴露在高温环境中,以评估其在极端存储条件下的数据保持能力和材料稳定性。

高温工作寿命 (High Temperature Operating Life): 芯片在通电工作状态下长时间暴露在高温环境中,以评估其在严苛操作条件下的整体可靠性。

湿度敏感性 (Moisture Sensitivity Level, MSL): 根据JEDEC J-STD-020标准对芯片进行MSL等级认证,指示芯片在回流焊前对环境湿度的敏感程度。较低的MSL等级表示对潮湿不敏感,而较高的等级可能需要在焊接前进行烘烤。

机械冲击和振动: 评估封装在物理冲击和振动下的机械完整性,这对于汽车电子、工业控制等振动环境的应用尤为重要。

10.3 制造质量与标准

美光的闪存产品在制造过程中遵循严格的质量控制标准和流程。

ISO/TS 16949认证: 对于汽车级产品,美光通常会通过ISO/TS 16949质量管理体系认证,确保生产过程符合汽车行业的最高标准。

JEDEC标准: 芯片的设计和测试遵循JEDEC(联合电子器件工程委员会)的行业标准,确保兼容性和互操作性。

RoHS合规性: 所有产品都符合RoHS指令,确保不含有害物质,满足环保要求。

PPAP (Production Part Approval Process): 对于汽车和一些工业应用,美光会提供PPAP文档,证明产品在生产前已经过全面验证,并符合客户的工程设计记录和规范要求。

良率管理: 严格的制造过程控制和测试流程确保了高良率,从而降低了缺陷率。

批次追溯: 完善的批次管理系统,可以追溯每个芯片的生产历史、原材料和测试数据,这对于质量控制和问题分析非常重要。

10.4 可靠性测试方法

在产品开发和量产过程中,会采用多种测试方法来验证芯片的可靠性:

加速寿命测试 (Accelerated Life Testing): 通过在高温、高压等极端条件下运行芯片,加速其老化过程,从而在较短时间内预测其在正常工作条件下的寿命。

失效分析 (Failure Analysis): 当芯片出现故障时,会进行详细的失效分析,包括电气测试、物理检查(如SEM、TEM)、材料分析等,以确定失效原因并采取纠正措施。

统计过程控制 (Statistical Process Control, SPC): 在制造过程中使用SPC技术监控关键参数,确保生产过程的稳定性和一致性。

N25Q128A13ESE40F的可靠性是其在各种关键应用中被广泛采用的基础。通过全面的设计、严格的测试和严格的质量控制,美光确保了其闪存产品能够满足甚至超越行业和客户的预期。对于最终用户而言,这意味着更稳定的系统运行、更少的数据损坏风险和更长的产品生命周期。

第十一章 常见问题与开发指南

在使用N25Q128A13ESE40F进行系统设计和开发时,开发者可能会遇到一些常见问题,并需要遵循特定的指南以确保最佳性能和可靠性。

11.1 常见问题与故障排除

11.1.1 无法识别芯片或通信失败

检查电源: 确保VCC电压在2.7V至3.6V之间且稳定。

检查SPI连接: 仔细检查SCK, CS#, SI, SO(或IO0-IO3)引脚的连接是否正确,是否存在短路或断路。

检查SPI模式: 确保主控制器和芯片的SPI时钟极性(CPOL)和时钟相位(CPHA)设置匹配(例如,都是模式0或模式3)。

片选时序: 确认CS#信号的时序是否符合数据手册要求,尤其是在SCK启动前和结束后的建立/保持时间。

时钟频率: 尝试降低SPI时钟频率,看是否可以正常通信。过高的频率可能导致信号完整性问题。

上电初始化: 确保在芯片上电后给予足够的稳定时间(tPUW)再发送第一个命令。

软件复位: 尝试发送软件复位指令(如果芯片支持)来重置芯片状态。

引脚复用: 如果使用多I/O模式,确保WP#和HOLD#引脚已正确配置为I/O线,并且没有同时作为其硬件功能引脚被错误驱动。

11.1.2 编程或擦除失败

未发送WREN指令: 编程或擦除前,务必先发送WREN(写使能)指令。这是最常见的错误之一。

BUSY位未检查: 在每次编程或擦除操作后,必须轮询状态寄存器的BUSY位,等待操作完成。在操作完成前发送下一个指令可能导致失败。

写保护: 检查是否有硬件写保护(BPx, TB位)或软件写保护(挥发性锁定位)被启用,导致目标区域无法写入。

地址错误: 确保编程或擦除的地址是有效的,并且对于页编程是页起始地址,对于扇区/子扇区擦除是扇区/子扇区内的任意地址。

电源稳定性: 在编程或擦除时,芯片会消耗较大的瞬时电流,如果电源线路阻抗高或电容不足,可能导致VCC跌落,从而造成操作失败。确保VCC有足够的去耦电容。

擦写寿命达到极限: 长期使用的芯片可能出现某些扇区擦写寿命耗尽。这通常会通过标志状态寄存器中的错误位指示。

11.1.3 数据读取不正确

时钟频率过高: 降低时钟频率,排除时序问题。

Dummy Cycles不足: 对于快速读取、双/四I/O读取指令,确保配置了足够的虚拟周期(Dummy Cycles)。如果虚拟周期太少,芯片可能没有足够的时间准备数据,导致读取错误。

信号完整性问题: 检查SPI总线上的信号质量,是否存在噪声、串扰或阻抗不匹配等问题,特别是在高速模式下。使用终端电阻或优化走线可以改善。

SPI模式不匹配: 确保主控制器读取时使用的SPI模式(0或3)与芯片期望的模式匹配。

数据保持失效: 极少数情况下,如果芯片已达到其数据保持寿命极限,数据可能会损坏。

11.1.4 功耗异常

未进入低功耗模式: 确保在空闲时正确发送指令进入待机模式或深度掉电模式。

CS#信号未拉高: 如果CS#信号一直保持低电平,芯片将保持活跃状态,功耗会较高。

SPI总线活动: 即使没有发送有效命令,SPI总线上持续的时钟或数据活动也可能导致功耗增加。

11.2 开发指南与最佳实践

11.2.1 硬件设计建议

电源去耦: 在N25Q128A13ESE40F的VCC引脚附近放置至少一个100nF的陶瓷去耦电容,并根据需要增加一个10uF或更大的电解电容,以提供稳定的电源并吸收瞬时电流。

SPI信号走线: 保持SPI信号线(SCK, CS#, SI, SO/IOx)尽可能短且平行,减少串扰。在高速应用中,考虑使用差分走线或阻抗匹配。

WP#/HOLD#引脚处理: 如果不使用其硬件功能,确保这些引脚有适当的上拉或下拉,避免悬空。在四I/O模式下,确保在软件中正确启用其I/O功能。

接地: 确保良好的接地平面,降低噪声。

11.2.2 软件驱动开发

状态机管理: 闪存操作涉及复杂的内部状态机(如忙碌、挂起、空闲)。驱动程序应严格遵循数据手册中描述的命令序列和状态转换。

错误处理: 驱动程序应包含错误检测机制,例如轮询标志状态寄存器,并在发生编程/擦除错误时采取适当的恢复措施(如重试、日志记录或通知系统)。

磨损均衡: 对于需要频繁擦写数据的应用,实施磨损均衡算法至关重要,以延长闪存的整体寿命。这通常涉及维护一个扇区擦写计数表,并优先使用擦写次数最少的扇区。

固件更新策略: 设计健壮的固件更新机制,包括:

安全校验: 使用CRC、MD5或数字签名来验证新固件的完整性和真实性。

回滚机制: 保留一份已知良好(Good Known)的固件版本作为备份,以便在更新失败时可以恢复。

双启动区: 在闪存中划分两个独立的启动区,交替存储主固件,以实现安全更新和回滚。

XiP优化:

正确配置Dummy Cycles: 根据系统时钟频率和性能要求,通过读取或写入挥发性配置寄存器来优化Dummy Cycles的数量。

Cache管理: 如果主处理器带有缓存,确保缓存策略与XiP访问模式兼容,避免缓存一致性问题。

代码位置: 将对性能要求最高的代码段放置在可以直接XiP的区域。

OTP区域管理: 谨慎对待OTP区域的编程。一旦编程和锁定,其内容将无法更改。在编程前应进行多次验证。

11.2.3 调试技巧

逻辑分析仪: 使用逻辑分析仪捕获SPI总线上的信号,可以帮助调试时序问题、命令序列错误或数据传输异常。

调试器: 利用微控制器调试器在代码中设置断点,逐步执行闪存操作指令,检查寄存器状态和返回值。

自定义测试程序: 编写小的测试程序,隔离地验证闪存的各个功能,例如只读ID、只进行页编程、只进行扇区擦除等。

遵循这些指南和最佳实践,可以帮助开发者更高效地使用N25Q128A13ESE40F,并构建出稳定、可靠且高性能的嵌入式系统。

总结与展望

美光N25Q128A13ESE40F是一款功能强大、性能优越的128Mbit串行NOR闪存芯片。通过深入探讨其产品概述、存储器组织、SPI接口、指令集、写保护机制、电气特性、典型应用、封装信息以及编程测试和开发指南,我们可以全面了解这款芯片的卓越之处。

N25Q128A13ESE40F的核心优势在于其高速SPI接口带来的高吞吐量、Execute-in-Place (XiP) 功能带来的快速启动能力、以及多层次的写保护机制和OTP区域带来的数据安全性。这些特性使其成为各种对性能、启动时间、可靠性和安全性有严格要求的嵌入式应用的理想选择,涵盖了从消费电子、工业控制到汽车电子和医疗设备等广泛领域。

随着物联网(IoT)设备数量的爆炸式增长以及边缘计算(Edge Computing)和人工智能(AI)在嵌入式系统中的普及,对高性能、低功耗、高可靠性和安全存储的需求将持续增长。串行NOR闪存,特别是像N25Q128A13ESE40F这样具备XiP能力的器件,将继续在这些新兴应用中扮演关键角色。它们能够提供快速的固件加载、实时代码执行以及安全的数据存储,从而支撑更智能、更响应迅速、更安全的设备。

未来,我们可以预见,NOR闪存技术将继续朝着更高密度、更快速度、更低功耗和更强的安全特性方向发展。同时,与处理器更紧密的集成、更简化的开发工具以及更智能的存储管理算法也将是行业发展的重点。N25Q128A13ESE40F作为美光在该领域的一个代表性产品,无疑将继续在数字世界的各个角落发挥其重要作用。

希望这份详尽的N25Q128A13ESE40F芯片资料能够为您在产品开发和技术研究中提供有价值的参考。在实际应用中,请务必结合最新的官方数据手册以获取最准确和最新的信息。

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)