tlk2711芯片手册

14

14

拍明芯城

拍明芯城

TLK2711高速串行收发器芯片中文技术手册

一、芯片概述

TLK2711是一款由德州仪器(Texas Instruments,TI)推出的高性能串行收发器芯片,广泛应用于高速数据通信领域,特别适用于光纤通信、背板互连和串行传输链路等高带宽需求的场景。该芯片支持最高2.7Gbps的数据速率,并兼容多种工业通信协议,如Gigabit Ethernet、光纤通道(Fibre Channel)以及各种ASIC或FPGA通信接口,具有极高的通用性与稳定性。

TLK2711基于串行化技术,将并行数据转换为高速串行数据输出,并具备接收端的串行至并行转换功能,其内部集成了高性能的时钟数据恢复(CDR)模块、8B/10B编码器/解码器、电压控制振荡器(VCO)、PLL环路以及强大的错误检测与恢复机制,为用户提供了完整的高速链路解决方案。

其主要应用包括电信设备、数据中心服务器、光模块、广播传输设备、工业控制系统等,特别适用于需要大带宽、低延迟和高可靠性的通信链路。

二、主要技术参数

以下列出TLK2711芯片的关键技术指标,这些参数是系统设计中重要的参考依据。

技术参数列表:

数据传输速率范围:0.6 Gbps 至 2.7 Gbps

串行接口:支持LVPECL、CML等差分信号标准

并行接口:16位并行数据总线(TXDATA、RXDATA)

编码机制:集成8B/10B编码器与解码器

电源电压:3.3V ±5%

接口逻辑电压:3.3V TTL兼容

接收输入灵敏度:±100mV

功耗:约650mW(典型)

工作温度范围:0°C ~ 70°C(商业级)

封装形式:64引脚TQFP封装

这些参数体现出TLK2711在高速、低功耗、接口兼容性方面的综合优势,在复杂通信系统中可大幅简化电路设计。

三、芯片内部结构与功能模块

TLK2711内部由多个高性能模块构成,各模块协同工作实现高速收发数据的全过程。

核心功能模块介绍:

并行至串行转换器(Serializer)

该模块负责将输入的16位并行数据编码并打包成串行数据,输出至高速差分链路。它与时钟管理模块密切协同,确保每一位数据精确时序传输。

串行至并行转换器(Deserializer)

接收到的高速串行数据经过CDR模块恢复时钟后,由该模块解包成并行数据输出,确保数据的完整性与正确解码。

时钟数据恢复模块(CDR)

用于从接收端串行数据中提取嵌入时钟信号,恢复出稳定的接收时钟。此模块是保持接收数据稳定可靠的关键技术之一。

8B/10B编码器与解码器

编码器将输入的8位数据转换成10位编码格式,从而确保DC平衡、消除长时间连续“0”或“1”的问题,增强链路抗干扰能力。接收端的解码器则完成逆转换。

锁相环(PLL)与振荡器

提供内部时钟生成与倍频功能,支持不同速率的自动锁定,确保发送与接收模块之间时钟同步。

环回与测试模式支持

支持本地回环(loopback)调试模式,便于故障定位与链路测试。

这些模块的集成使TLK2711能够在各种复杂通信环境中稳定运行,同时减轻了外部逻辑负担。

四、工作原理详解

TLK2711的基本工作过程可以从发送端与接收端两个方向进行分析。发送端将并行数据输入后进行编码、串行化,再通过差分信号发送;接收端则从差分信号中恢复时钟并完成解码与并行化处理。

发送过程说明:

发送部分通过16位TXDATA输入总线接收并行数据,同时由TXCLK提供同步时钟。数据首先进入8B/10B编码器,经过编码后转交至串行转换器(Serializer),完成串行化后,通过TX+、TX-差分对发送至链路另一端。

接收过程说明:

接收部分通过RX+、RX-差分输入对接收高速串行信号,数据经过CDR模块恢复出嵌入时钟,然后由Deserializer进行解串转化为16位并行格式,再送至RXDATA输出总线。若启用8B/10B解码功能,数据还会进行解码处理并附加错误检测。

整个收发链路的数据路径和时钟路径高度集成,保证了数据准确性和系统时钟的稳定性,尤其适合长距离、高频宽通信场景。

五、芯片主要特性优势

TLK2711作为高速串行收发器,其综合性能极为出色,适用于高速通信应用中对信号完整性和系统稳定性要求极高的场景。

芯片的主要优势特性包括:

高速率支持: 可支持高达2.7Gbps的数据速率,满足现代数据通信对带宽的严苛要求。

集成度高: 内部集成多项功能模块,无需额外外部逻辑器件即可构建完整通信通道。

兼容性强: 支持多种逻辑电平标准和接口协议,适用于多种平台如FPGA、ASIC等。

低功耗设计: 典型功耗约650mW,适用于功耗敏感型设备。

增强抗干扰能力: 通过8B/10B编码提高信号完整性,适合恶劣电磁环境下的通信。

测试功能完善: 内建环回模式便于链路调试和系统集成测试。

成熟封装与接口设计: TQFP封装方便PCB设计,具备良好的散热性与电气性能。

这些特性使其在众多高速通信芯片中脱颖而出,被广泛应用于对信号完整性有较高要求的系统中。

六、典型应用领域

TLK2711的强大功能使其在多个行业获得广泛应用。以下为其常见应用领域。

主要应用场景列表:

光纤收发模块

数据中心互连系统

高速背板通信

工业自动化通信系统

服务器和存储设备

广播视频设备高速接口

电子测量与测试仪器

在这些场景中,TLK2711承担核心通信接口的角色,通过其高速、稳定的数据通路构建可靠的系统通信架构。

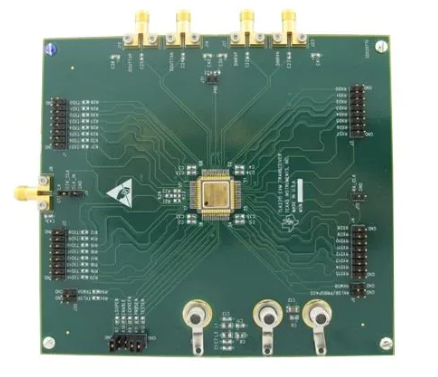

七、典型应用电路设计

设计TLK2711的应用电路时需关注电源隔离、差分阻抗匹配、时钟源选择等多个方面。以下为一组典型的发送和接收电路示意:

发送端设计要点:

16位TXDATA通过FPGA或微控制器控制

输入时钟TXCLK应为同步源,可用晶振或来自FPGA的输出

TX+、TX-差分对经由AC耦合电容连接至链路或光模块输入

需保持差分阻抗为100Ω匹配

接收端设计要点:

RX+、RX-差分对经由AC耦合接入

CDR模块恢复出的RXCLK提供给下游系统作为同步时钟

RXDATA并行数据通过逻辑控制器处理

良好的PCB布局和差分走线是确保数据传输完整性的关键,建议使用连续参考层与匹配的差分走线规则。

八、使用注意事项与调试建议

TLK2711虽功能强大,但在设计和调试过程中仍需注意多个细节,以确保系统运行稳定。

使用注意事项列表:

供电稳定性: 电源应使用低纹波LDO或DC-DC稳压器,避免供电噪声引起时钟漂移。

时钟源品质: 若使用外部参考时钟,抖动应控制在极低水平,以保证CDR模块可靠工作。

差分阻抗控制: PCB布线时应确保差分对走线长度差小于5mil,总阻抗为100Ω。

散热设计: 高速工作会产生热量,应预留散热通孔和铜皮,必要时加散热器。

编码同步: 若使用8B/10B编码,应确保发送与接收端一致配置,避免同步错误。

测试模式验证: 使用环回模式可进行芯片自检与链路测试,提高调试效率。

九、与其他芯片对比分析

TLK2711常被用于替代或与其他高速串行芯片比较,如TI的TLK2501、ADI的ADN2814或Intel的GX系列串行PHY。

对比分析列表:

与TLK2501相比,TLK2711具有更低功耗和更高集成度

与ADN2814相比,TLK2711适配性更强,电源更简单

相较Intel GX PHY,TLK2711在非FPGA系统中更具灵活性和开发便捷性

因此,TLK2711通常是中高端通信设备在非大规模FPGA场景下的首选。

十、结语与未来展望

TLK2711作为一款成熟的高速串行收发芯片,其优异的性能和广泛的应用使其长期占据工业通信芯片的重要地位。虽然随着通信速率的进一步提升,新一代如25G、56G SerDes正在兴起,但在诸如2.5G~3G的中高速通信场合,TLK2711仍具备极强的生命力。

未来,随着物联网、工业互联、5G边缘通信等新兴应用的拓展,对中高速、低延迟收发器的需求将持续增长。TLK2711的可靠性、成熟生态和TI强大的支持体系,将继续在这些领域中发挥重要作用。

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)