74lvc245引脚及功能

16

16

拍明芯城

拍明芯城

74LVC245引脚及功能详解

一、概述:CMOS总线收发器的重要地位

在当今数字电子系统中,尤其是在多模块互联、数据总线复杂的嵌入式系统、通信设备、工业控制板以及消费电子产品中,数据传输的方向性与稳定性成为了设计的核心问题之一。在这种背景下,具备高性能双向数据传输能力的总线收发器芯片便显得尤为关键。而74LVC245,作为一款来自74系列的低电压 CMOS 八位双向总线收发器,不仅功能强大,而且结构灵活,广泛应用于各种逻辑控制系统中,尤其在多位并行通信、电平匹配、总线扩展等场景下显示出其独特优势。

该芯片内建方向控制与三态使能机制,能够根据外部逻辑控制信号选择数据流的方向,并根据需要将输出设为高阻状态,避免不同模块之间的数据冲突。其低功耗、高速度、高电平兼容性等特点,使其在3.3V和5V系统中同样表现出色,并可轻松胜任多种电平交互应用。

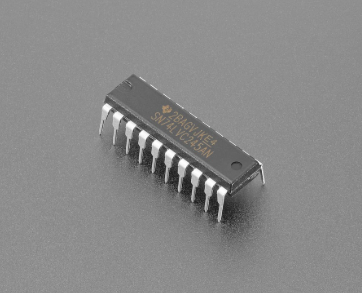

二、封装结构与物理外形

74LVC245通常采用多种封装形式以满足不同电路板的安装需求,包括标准的DIP(Dual Inline Package)双列直插封装、SOIC(Small Outline Integrated Circuit)小外形封装、TSSOP(Thin Shrink Small Outline Package)薄型封装以及更小尺寸的VQFN(Very Thin Quad Flat No-lead)封装。

这些封装形式不仅满足不同布线密度和机械强度的需求,而且由于管脚布局统一,大部分应用电路可在封装互换时保持原样不变。例如在小型化产品如移动终端、便携式仪器等场景下,TSSOP-20或VQFN-20封装极具优势,占用PCB面积小,同时具备良好的热性能。

以最常见的TSSOP-20为例,该封装器件共有20个引脚,针脚间距约为0.65mm,适合SMT贴片加工,所有管脚沿两侧对称分布,利于布线与多芯片模块化设计。

三、引脚分布图及说明

在TSSOP-20或SOIC-20封装中,74LVC245的引脚分布如下:

+---------------------+

A1 | 1 20 | Vcc

A2 | 2 19 | B1

A3 | 3 18 | B2

A4 | 4 17 | B3

A5 | 5 16 | B4

A6 | 6 15 | B5

A7 | 7 14 | B6

A8 | 8 13 | B7

GND | 9 12 | B8

OE̅ | 10 11 | DIR

+---------------------+

四、每个引脚的详细功能解释

1. A1–A8(引脚1~8)

这些引脚代表A端口的数据输入/输出端。它们与B端口配合使用,承担数据的输入与输出功能。方向取决于DIR信号电平的设置:当DIR为高电平时,数据从A端传输到B端;反之,则数据由B传输到A。这种设计使得芯片具备完整的双向通信能力,可在不同子系统间进行高效数据交互。A1至A8分别对应B1至B8的通道,每一对引脚形成一条独立的数据通路,可并行传输8位数据,非常适合用于8位数据总线场景。

2. GND(引脚9)

该引脚为地线(Ground),是整个芯片内部电路的零电位参考点。所有输入输出逻辑电平均以GND为参考电位,因此在系统设计中必须确保GND连接良好,并与其他模块的地线保持一致,以避免电平漂移、逻辑错误或电磁干扰。同时,GND引脚还承担着电流回路闭合的作用,若GND断开或阻抗过大,会导致芯片无法正常工作。

3. OE̅(引脚10)

该引脚为输出使能(Output Enable)控制信号,为低有效信号。即当OE̅为低电平时,芯片处于激活状态,允许数据在A、B之间传输;当OE̅为高电平时,芯片进入高阻态(Hi-Z),所有输出端口被断开,与总线“脱钩”,不参与数据传输。这种设计极大提升了总线的多路复用能力,允许多个设备共用一条数据总线而不会发生驱动冲突。OE̅功能在多芯片并联应用中尤为关键,通常由中央控制器或逻辑单元动态控制。

4. DIR(引脚11)

该引脚为数据方向控制信号(Direction Control),用于决定数据传输的方向。当DIR为高电平时,数据从A端传输到B端;当DIR为低电平时,数据从B端传输到A端。该引脚与OE̅结合使用,可实现高灵活性的双向通信控制。在设计中,DIR通常由处理器或状态逻辑控制,配合总线仲裁机制,确保数据在正确时序与方向上传输。

5. B1–B8(引脚12~19)

这些引脚为B端口的数据输入/输出端,与A端口形成对应关系,即B1与A1相连,B2与A2相连,依此类推。当数据方向设置为A到B时,这些引脚将充当输出端;反之亦然。这种灵活的配置方式让芯片不仅可用于信号方向选择场景,还可用于双向电平转换、双总线接口等复杂应用。

6. Vcc(引脚20)

该引脚为正电源输入端,是芯片内部CMOS电路供电的主电源接口。74LVC245的工作电压范围较宽,一般为1.65V至3.6V,典型值为3.3V。Vcc必须连接至稳定的低噪声电源,并配合适当的去耦电容(如0.1μF+1μF并联)近距离放置,以确保供电稳定,避免电源波动影响逻辑电平判断与输出驱动能力。

五、工作原理分析

74LVC245的核心工作机制依赖于其内部的八组双向缓冲器,这些缓冲器既可作为数据驱动器,也可作为信号接收器。每组缓冲器的工作状态由两个控制引脚OE̅与DIR联合决定。

数据传输方向由DIR决定:

DIR=1:A → B(数据从A端传输到B端)

DIR=0:B → A(数据从B端传输到A端)

输出状态由OE̅决定:

OE̅=0:输出激活,允许数据传输;

OE̅=1:高阻态,禁止输出,端口断开。

该控制逻辑保证了在任意时刻只有一个方向的数据流动,并可通过高阻机制防止总线冲突。

例如,在一个典型的主从微控制器系统中,主控MCU可以通过控制DIR和OE̅信号来选择性地读取从设备的数据或向其发送控制指令,从而在共享总线上实现可靠通信。

六、逻辑真值表与工作状态组合说明

为帮助设计人员更清晰地掌握74LVC245芯片在各种控制信号组合下的工作状态,我们必须结合OE̅和DIR两个控制引脚的逻辑组合,分析其对应的数据传输行为。以下是真值表(Truth Table):

| OE̅(输出使能) | DIR(方向控制) | A端口状态 | B端口状态 | 描述 |

|---|---|---|---|---|

| L(低) | L(低) | 输入 | 输出 | B ← A(A到B) |

| L(低) | H(高) | 输出 | 输入 | A ← B(B到A) |

| H(高) | X(任意) | 高阻态 | 高阻态 | 所有输出禁用(高阻状态) |

这种机制非常有利于在系统中设计总线控制和冲突避免逻辑。例如多个设备连接至同一总线时,可通过中央控制逻辑协调各个芯片的OE̅信号,仅允许一个芯片处于激活状态,其余芯片均为高阻状态,从而避免短路或逻辑错误。

七、电气参数与时序特性全面解读

对于一款逻辑芯片而言,其电气参数直接决定了芯片的适用电压、驱动能力、响应速度以及整体系统的稳定性和性能。74LVC245的电气参数具有典型的低压CMOS特性,支持较宽的工作电压和较强的兼容性。

1. 主要电气参数

| 参数项 | 最小值 | 典型值 | 最大值 | 单位 | 说明 |

|---|---|---|---|---|---|

| 工作电压范围 | 1.65 | 3.3 | 3.6 | V | 支持1.8V、2.5V、3.3V系统 |

| 输入高电平 VIH | 2.0 | — | — | V | 最小输入高电平,低于此值视为低电平 |

| 输入低电平 VIL | — | — | 0.8 | V | 最大输入低电平,高于此值视为高电平 |

| 输出高电平 VOH | 2.9 | 3.2 | — | V | 驱动高电平输出 |

| 输出低电平 VOL | — | — | 0.4 | V | 驱动低电平输出 |

| 三态漏电流 IOZ | — | — | ±5 | µA | 高阻状态时的最大漏电流 |

| 每路驱动电流 | ±24 | mA | 最大持续输出电流,适合强驱动应用 | ||

| 输入电流 | — | — | ±1 | µA | CMOS输入高阻,输入电流极小 |

2. 时序参数

| 参数项 | 条件(Vcc=3.3V) | 典型值 | 单位 |

|---|---|---|---|

| 传播延迟 tPLH / tPHL | CL=50pF | 3.8 ns | ns |

| 输出使能延迟 tPZL / tPZH | CL=50pF | 4.0 ns | ns |

| 输出禁用延迟 tPLZ / tPHZ | CL=50pF | 4.2 ns | ns |

八、关键特点与性能优势分析

74LVC245之所以广泛应用于各种总线系统,不仅在于其基本的双向收发功能,还因为它具备许多电气性能与封装上的优势:

1. 支持低压电源系统

该芯片设计基于LVC(Low Voltage CMOS)工艺,支持最低1.65V的供电电压,适配现代低功耗逻辑系统的趋势。

2. 高速数据传输能力

其传播延迟小于5ns,支持几十兆赫兹的并行数据交互,是高速系统中稳定的数据缓冲与传输器件。

3. 高阻三态输出

内建的三态输出功能,使芯片在未被选通时对总线影响为零,方便多设备共享总线,防止数据冲突。

4. 强驱动能力

支持最大±24mA的输出电流,即便驱动多个负载,也能保持逻辑电平的完整性。这对长距离布线、大电容负载系统尤为重要。

5. ESD与Latch-up防护设计

大多数LVC芯片都具备超过±2000V的ESD防护能力,能有效应对人体接触带来的静电风险。此外,其CMOS结构优化设计也增强了Latch-up抵抗能力,提升整体稳定性。

6. 高电平输入容忍

即使供电电压为1.8V,也允许接受3.3V的输入信号,这在电平转换应用中极具价值。

九、典型应用电路图详解

为了更具体展示74LVC245的使用方法,我们以两个典型应用场景为例:

1. 微控制器双向总线扩展

MCU(GPIO1-8) ---- A1~A8

DIR ← 控制信号(MCU)

OE̅ ← 控制信号(MCU)

|

B1~B8 → 连接到外设或外部总线

在此电路中,MCU通过控制DIR和OE̅信号控制芯片工作模式。当需要向外设发送数据时,将DIR设为高电平(A到B),OE̅拉低;当需要从外设读取数据时,将DIR设为低电平(B到A),OE̅拉低。通过这种方式,MCU可实现与外部8位数据总线的双向通信,而无需额外硬件切换。

2. 不同电压系统的数据桥接

系统A(1.8V) → A端

DIR ← 恒定电平或MCU控制

OE̅ ← 恒定电平或MCU控制

系统B(3.3V) ← B端

此场景适用于两个不同电压平台之间的数据交互。由于74LVC245支持3.3V容忍输入,即便其Vcc为1.8V,仍可接收来自3.3V系统的逻辑信号,发挥电平转换桥接的作用。这种应用常见于SoC与外部存储芯片、外围接口模块之间的数据交互中。

十、电平转换应用优势

74LVC245在现代电子设计中广泛充当电压电平转换桥梁,这是由于其出色的输入容忍和输出驱动能力所致。当前电子系统中普遍存在不同供电电压等级的设备,例如1.8V的低功耗MCU需要与3.3V外设通信,或者3.3V主控芯片要与5V老旧设备协同工作。在这种场景下,电平转换器成为系统稳定运行的关键。

74LVC245具有以下几项在电平转换中的独特优势:

1. 宽输入电压容忍特性

即使芯片工作在较低的供电电压下,如1.8V或2.5V,它的输入引脚仍然可以承受最高至5.5V的输入信号。这种特性在跨平台设计中非常有用,特别是在处理高电平系统与低电平控制器之间的信号匹配时。

2. 对称的双向结构

由于芯片支持控制方向,且具备完整的三态输出,因此其A端与B端都可以看作是输入或输出端,使其可以灵活实现任意方向的电平桥接。例如,当主控芯片为1.8V而外部模块为3.3V时,将芯片供电接在1.8V,同时使用DIR控制数据流向,即可轻松完成双向桥接。

3. 简洁的控制逻辑

仅需两个控制引脚(OE̅和DIR)即可实现三种状态:从A到B传输、从B到A传输以及高阻断态,简化了系统控制逻辑,无需使用多余的三态门或分立电平转换电路。

这种便捷且强大的特性,使74LVC245成为许多嵌入式系统、电源隔离模块、FPGA通信接口中首选的电平转换解决方案之一。

十一、与其他收发器芯片对比(如74HC245、74LV245)

为了更全面理解74LVC245的优势,我们将它与同类芯片做横向对比,包括74HC245和74LV245两种常见型号。这几种芯片虽然功能类似,但由于制造工艺、电压支持范围和驱动能力不同,它们适用的场景也存在差异。

1. 与74HC245的对比

| 参数/特性 | 74LVC245 | 74HC245 |

|---|---|---|

| 工艺类型 | CMOS低电压工艺 | 标准CMOS工艺 |

| 工作电压范围 | 1.65V - 3.6V | 2.0V - 6.0V |

| 输入电平容忍 | 最高支持5.5V | 不超过Vcc + 0.5V |

| 最大传播延迟 | ~5ns | ~15ns |

| 三态输出 | 支持 | 支持 |

| 典型应用 | 现代低压系统 | 老旧中速系统 |

2. 与74LV245的对比

| 参数/特性 | 74LVC245 | 74LV245 |

|---|---|---|

| 工作电压范围 | 1.65V - 3.6V | 2.0V - 5.5V |

| 最大输出电流 | ±24mA | ±12mA |

| 电平容忍能力 | 最大输入5.5V | 最大输入Vcc |

| 推挽输出强度 | 强驱动 | 中等驱动 |

十二、设计注意事项与抗干扰建议

在使用74LVC245设计实际电路时,应当注意若干关键设计细节,以保障系统的稳定性、抗干扰能力和可靠性。以下是一些实际工程经验总结的设计建议:

1. 电源去耦

建议在芯片Vcc与GND之间接入0.1µF与1µF两个电容,分别滤除高频和低频噪声,提升供电稳定性。去耦电容尽量靠近芯片布置,避免电源纹波干扰逻辑电平。

2. 控制信号稳定性

OE̅与DIR两个引脚建议由时序可靠的控制器(如MCU或FPGA)直接控制,避免使用悬空或模拟电平输入。OE̅若接至外部控制逻辑,其电平变化应避免与数据线状态发生冲突,建议通过上电延时控制避免在系统初始化阶段发生竞争。

3. 防止数据总线冲突

在总线系统中使用多个74LVC245时,确保同一时间仅有一个器件输出数据至总线,其他均处于高阻状态。系统设计时应加入总线仲裁机制或使用菊花链式OE̅控制。

4. 端接匹配与布线注意

对于高速传输场景,建议在输出端加串联阻值为22~33Ω的小电阻用于匹配,减少信号反射。PCB布线时应尽量避免走线交叉、回路路径不清晰等布线错误,以防止EMI问题。

十三、常见问题诊断与解决方案

在使用74LVC245芯片过程中,工程师常遇到一些实际问题,以下列出常见问题及其解决策略:

问题1:输出异常或数据失真

原因分析: 控制引脚未正确配置(OE̅或DIR悬空);供电不稳定;总线存在多个驱动器同时输出。

解决方法: 检查控制信号逻辑,确保OE̅正确拉低以使能输出;添加去耦电容稳定供电;合理规划总线驱动器。

问题2:芯片温度过高

原因分析: 输出端驱动过大负载或短路;多输出口并联造成电流冲突。

解决方法: 检查负载电流是否超出芯片规格;避免多个芯片同时驱动同一总线;必要时加限流电阻。

问题3:通信速率不足或误码频繁

原因分析: 传输线过长引起信号衰减或反射;芯片驱动能力不足以支持长距离传输。

解决方法: 加入串联终端电阻;缩短布线长度;使用差分信号传输方案或添加缓冲级。

十四、测试、验证与仿真方法

在任何数字逻辑设计过程中,验证芯片行为和电路正确性是至关重要的一步。对于74LVC245这样的三态双向总线收发器,测试方法既包括静态功能验证,也包括动态时序仿真和系统级集成验证。

1. 静态功能测试

这类测试主要用于验证芯片的基本逻辑行为:

设置不同的OE̅和DIR组合,观察是否正确控制输出/高阻状态;

向A端或B端输入固定电平(如0或1),验证另一端是否正确反映;

断电后检查是否有“漏电现象”,以验证高阻态是否有效;

验证输入容忍性,在VCC = 1.8V或3.3V时,输入5V逻辑信号检查是否无损。

常见工具:逻辑分析仪、多通道示波器、微控制器开发板(如STM32或Arduino)配合GPIO输出测试向量。

2. 动态时序仿真

为了确保设计满足信号完整性和速度需求,应在仿真软件中模拟其动态行为,尤其是在高频数据传输应用中:

使用SPICE模型或IBIS模型进行时域仿真;

仿真输入跳变沿对输出延迟的影响,评估传播延迟tpd;

验证输出电平上升沿、下降沿(tr/tf)是否符合标准总线系统需求;

检查在不同电压、不同负载下的电流消耗变化。

推荐软件:LTspice、Cadence PSpice、Mentor HyperLynx Signal Integrity。

3. 系统级验证

在目标应用平台上进行系统级联调是必不可少的步骤:

在与MCU/FPGA对接时测试通信稳定性;

验证多芯片协作下的总线管理逻辑是否一致;

用大量数据测试传输稳定性(如UART、SPI、I²C数据桥接);

在电压波动、电磁干扰下测试稳健性(如加电噪声、负载热启动)。

十五、封装选型与布局优化策略

74LVC245芯片广泛提供多种封装形式以适应不同PCB布局需求,包括SOIC-20、TSSOP-20、SSOP-20、VQFN-20等。每种封装对应的特点与使用建议如下:

1. 常见封装类型

| 封装 | 引脚间距 | 适用场景 | 优点 | 缺点 |

|---|---|---|---|---|

| SOIC-20 | 1.27mm | 通用板卡、测试开发板 | 易于手焊 | 占板面积较大 |

| TSSOP-20 | 0.65mm | 高密度电路板 | 芯片紧凑 | 焊接要求高 |

| SSOP-20 | 0.635mm | 便携设备、高速信号 | 节省空间 | 易短路 |

| VQFN-20 | 无引脚 | 超小型设备 | 散热良好、空间小 | 需底部焊盘、工艺复杂 |

芯片中线对称放置:由于A与B端对称,建议以中轴线方式放置,有利于左右两侧总线直接进入;

靠近MCU/FPGA布放:减少数据线长度,降低信号延迟;

三态控制线优先布线:OE̅和DIR应避免与高速数据线平行布线,防止干扰;

地线短而粗:尤其VQFN封装需布置GND焊盘,以确保地稳定性与良好散热;

电源层铺铜:VCC与GND连接建议使用多层板供电层或铺铜方式。

十六、结语:工程实战中的不可或缺角色

74LVC245不仅是一个数字信号收发器,更是现代信号完整性管理、电平桥接、总线共享优化的解决方案核心器件。它所扮演的角色远不止逻辑门那么简单,而是:

在不同电压平台之间搭建稳定通信桥梁;

通过三态高阻状态参与复杂总线共享机制;

以高速传输与强驱动能力,成为嵌入式设计中的可靠传输保障者;

在低功耗场景中以出色的电平容忍度简化设计逻辑,降低系统成本。

其低延迟、强兼容、稳定输出特性,使其在物联网节点、工业控制器、便携设备接口、高速数码产品等领域成为设计工程师信赖的选择。

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)