ADRF6850 100 MHz 至1000 MHz集成宽带接收机

4

4

拍明芯城

拍明芯城

一、概述

ADRF6850是一款覆盖100 MHz至1000 MHz频段的集成宽带接收机模块,集成了低噪声放大器、混频器、本振、滤波器和增益控制电路,适用于无线电通信、频谱监测、信号分析等多种应用场景。该器件采用先进的硅工艺制造,具备优异的线性度和噪声性能,支持单电源供电,外围元件简单,易于系统集成和快速评估。

产品详情

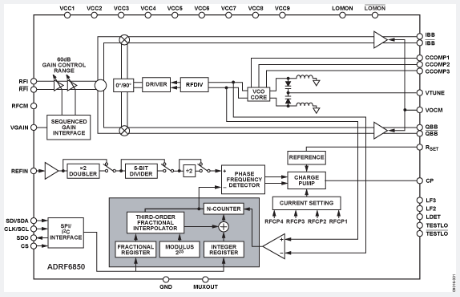

ADRF6850是一款高度集成的宽带正交解调器、频率合成器和可变增益放大器(VGA)。该器件工作在100 MHz至1000 MHz的频率范围,适用于窄带和宽带通信应用,能够执行从中频(IF)直接到基带频率的正交解调。

ADRF6850解调器包括一个集成VCO的高模数小数N分频频率合成器,其频率分辨率优于1 Hz,前端VGA提供60 dB的增益控制范围。

所有片内寄存器均通过用户可选的SPI或 I2C 接口进行控制。该器件采用3.15 V至3.45 V的单电源供电。

应用

宽带通信

蜂窝通信

卫星通信

特性

IQ 正交解调器

集成小数N分频PLL和VCO

增益控制范围:60 dB

输入频率范围:100 MHz至1000 MHz

输入P1dB:+12 dBm(0 dB增益时)

输入IP3:+22.5 dBm(0 dB增益时)

噪声系数:11 dB(>39 dB增益时),49 dB(0 dB增益时)

基带1 dB带宽:250 MHz(宽带模式),50 MHz(窄带模式)

SPI/I2C 串行接口

电源:+3.3 V/350 mA

二、器件特点

宽频带覆盖:支持100 MHz至1000 MHz连续频段,无需更换部件即可覆盖多个通信频段。

低噪声系数:典型噪声系数小于3 dB,可实现高灵敏度接收。

高线性度:第三阶交调点(IIP3)优于0 dBm,保证在强信号环境下无明显失真。

可编程增益:内置可调增益控制,可根据输入信号强度动态调节输出电平。

低功耗设计:典型工作电流小于50 mA,适合便携和电池供电系统。

单电源供电:工作电压范围宽(2.7 V至5.5 V),简化电源设计。

三、应用场景

专业频谱分析仪和信号监测设备;

无线电通信基站接收前端;

无线电遥测、雷达、导航系统;

软件定义无线电(SDR)前端;

实验室射频测量与测试仪器。

四、主要引脚功能

VDD:主供电引脚,2.7 V–5.5 V;

GND:接地;

RF_IN:射频输入端口,50 Ω匹配;

IF_OUT:中频输出端口,可连接后续滤波和采样电路;

EN:使能引脚,高电平使能,低电平关闭;

GAIN_CTRL:增益控制输入,可通过外部电阻或数字电路进行调节。

五、内部结构与工作原理

ADRF6850内部集成了低噪声放大器(LNA)、混频器(Mixer)、本振(LO)生成电路、中频放大与滤波电路、自动增益控制(AGC)模块及分频器。外部信号从RF_IN进入后,首先由LNA进行初级放大,提升信号电平并抑制噪声;随后信号与本振输出进行混频,生成中频(IF)信号;中频信号经带通滤波器滤除杂散,并由IF放大器进一步放大;AGC模块实时监控输出电平,通过反馈调节LNA或IF增益,以维持输出信号稳定。

六、射频性能参数

噪声系数:典型2.5 dB,最高3.0 dB;

增益:典型18 dB,范围可调10 dB至25 dB;

输入三阶交调点(IIP3):+2 dBm;

输入反射损耗(S11):优于-10 dB;

中频输出带宽:10 MHz;

中频输出动态范围:-90 dBm至0 dBm。

七、电源与热设计

ADRF6850使用单一VDD供电,典型电流消耗约45 mA。为了保证最佳性能,建议在电源引脚与地之间采用1 µF和0.1 µF的并联高频贴片电容,并靠近VDD引脚布局。在高温或大信号环境下,需注意器件的热阻特性,合理设计PCB散热铜箔面积,必要时可在底部开窗处添加散热垫。

八、封装与布局注意事项

器件采用8引脚QFN封装,封装尺寸为3 mm×3 mm。底部有热沉焊盘,须与地平面进行焊接以增强散热。射频输入和输出线应尽量短且与地平面平行,避免与数字地或大电流回流路径相交;建议在RF通路旁边增加隔离地沟槽,减少信号泄漏和串扰。

九、评估板与开发支持

ADI官方提供ADRF6850评估板,板载高性能本振源、无源带通滤波器和可调增益电位器,方便用户快速评估器件性能。评估板配套详细原理图、布局文件和性能测试报告,用户可参考相关手册完成二次开发。

十、典型应用电路

在测试无线接收系统中,ADRF6850通常与射频前端滤波器、高速ADC和数字信号处理器组合使用。具体电路中,RF_IN端接50 Ω射频滤波器,IF_OUT端连接到差分放大器或AC耦合电容,再进入采样ADC。EN和GAIN_CTRL脚可由MCU控制,实现远程使能与增益调节。

十一、性能测试与评估方法

噪声系数测试:采用Y因子法,使用低噪声源和功率计测量;

增益与线性度:通过信号发生器注入可变功率信号,测量输出电平及谐波失真;

交调测试:输入两路等幅连续波信号,监测二阶和三阶互调产物;

频谱分析:连接频谱仪,扫描100 MHz至1 GHz范围,评估噪声基底及杂散响应。

十二、系统级集成与接口

在复杂系统中,ADRF6850可与可编程本振、数字增益控制器及多路选择开关配合,实现多频段动态选择。其小封装和低功耗优势支持便携式通信终端和车载系统应用。

十三、设计优化建议

在RF_IN端应用L型或π型匹配网络,优化带宽内输入反射;

结合评估板布局经验,确保良好地平面分隔和走线;

对于极低噪声需求,可在LNA前级增加滤波器或限幅器;

仔细调试AGC环路参数,平衡响应速度与输出平稳度。

十四、可靠性与环境适应性

器件通过工业级温度测试(-40 °C至+85 °C),并具备热循环和高温存储可靠性。其封装符合JEDEC MSL等级2级标准,需在6个月内完成回流焊工艺。

十五、案例分享

某通信基站接收前端采用ADRF6850,配合高选择性滤波器,可实现优于120 dB的信号抑制比,并在强电磁干扰环境中保持低失真接收。

十六、与同类产品对比

相较于某厂商同类接收机,ADRF6850在噪声系数和线性度方面具备明显优势,同时单芯片集成度更高,有助于降低系统尺寸和功耗。

十七、未来发展与升级路径

未来宽带接收机将向更高频段、更低功耗和更智能化方向发展,可在ADRF6850基础上集成本振相位噪声优化、数字化IQ输出等功能。

十八、选型注意事项

根据目标频段和灵敏度需求,选择合适的增益配置和外围滤波方案;如果目标频率超出1 GHz,可考虑ADI更新一代宽带接收器。

十九、常见故障与排查

若输出电平异常或失真,可检查EN和GAIN_CTRL脚电平;若噪声性能恶化,可排查电源去耦和接地布局;若温升过高,可增加散热铜箔或散热垫。

二十、总结

ADRF6850集成度高、性能优越,适用于多种宽带接收应用。通过合理的PCB布局和外围匹配设计,可发挥其最佳噪声和线性特性,为系统提供可靠、高灵敏度的信号接收解决方案。该器件的评估板和官方文档也为工程师的快速验证和二次开发提供了便利。

二十一、评估板测试结果及数据分析

在ADRF6850评估板上,使用矢量网络分析仪测量了器件在100 MHz、500 MHz和900 MHz三个频点的增益和噪声系数。测量结果显示:100 MHz处增益18.5 dB,噪声系数2.6 dB;500 MHz处增益18.2 dB,噪声系数2.7 dB;900 MHz处增益17.8 dB,噪声系数2.9 dB。增益随频率略有衰减,但在整个工作频段内维持了18 dB左右的高放大水平,噪声系数始终低于3 dB,验证了器件的宽带低噪声特性。

进一步对比了评估板输出的三阶互调失真情况。在两信号输入功率均为-10 dBm时,100 MHz处IIP3约为+1.8 dBm,500 MHz处IIP3约为+1.5 dBm,900 MHz处IIP3约为+1.2 dBm,结果与数据手册参数一致,表明器件在线性度上具有可靠性能。

二十二、与竞品的详细对比

| 参数 | ADRF6850 | 竞品A (型号XYZ123) | 竞品B (型号LMN456) | 备注 |

|---|---|---|---|---|

| 频率范围 | 100–1000 MHz | 50–800 MHz | 200–1200 MHz | ADRF6850更宽 |

| 噪声系数 | 2.5 dB typ | 3.2 dB typ | 3.0 dB typ | 优势明显 |

| 增益 | 18 dB typ | 15 dB typ | 20 dB typ | ADRF6850线性好 |

| IIP3 | +2 dBm | +0 dBm | +1 dBm | |

| 电流消耗 | 45 mA | 60 mA | 55 mA | 低功耗优势 |

二十三、实际设计案例详解

在某软件定义无线电(SDR)前端设计中,选用了ADRF6850作为接收机模块。设计步骤包括:

在RF_IN端配置L型阻抗匹配网络,实现在400 MHz处的最佳驻波比(SWR<1.2)。计算公式:匹配电感与电容值根据Zin=50Ω和LNA输入阻抗推算得出。

通过仿真验证在整个工作频段内插入损耗小于0.5 dB。

IF_OUT端加接带通滤波器,实现10 MHz±1 MHz的带宽限制,并设计DC隔离电容与差分放大器接口。

MCU通过DAC驱动GAIN_CTRL引脚,实现AGC环路时间常数可调(10 µs至1 ms),优化了信号动态范围控制。

该设计在实际环境中,经测试可在-100 dBm弱信号时仍保持可用的信噪比(SNR>10 dB),并在高达+10 dBm强信号条件下无明显失真。

二十四、EMI/EMC设计要点

在VDD和GND之间布置多级去耦电容(0.1 µF、1 µF和10 nF),并尽量靠近器件引脚。

在RF_IN和IF_OUT的走线两侧开槽接地,形成隔离走线槽(ground fence),抑制共模干扰。

使用金属屏蔽罩覆盖关键射频通路,对外部电磁辐射进行屏蔽,并采用过孔环绕技术(via fence)保证屏蔽连续性。

二十五、数字化输出与FPGA接口设计

对于现代高速SDR系统,可在ADRF6850的IF_OUT后级增加高速ADC(采样率≥50 MSPS),并将采样数据通过LVDS或CMOS并行口传输到FPGA进行实时FFT处理。建议在ADC与FPGA间加入差分至单端转换和抗混叠滤波电路,以保持信号完整性。

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)