第一章:绪论

随着无线通信和射频系统性能需求的不断提高,数字预失真(DPD)技术已成为提升功率放大器线性度和效率的关键手段。ADRF6821 作为一款面向通信数字预失真接收系统的高集成度射频集成电路,创新性地将分数分频锁相环和多路压控振荡器融入同一芯片,并提供宽带输入覆盖 450 MHz 到 2800 MHz 频段。本文将从器件背景、功能特性、内部架构、性能指标、典型应用以及设计指南等多维度,对 ADRF6821 进行系统而深入的介绍,以期为射频系统设计工程师提供实用参考。

产品详情

ADRF6821 是一种高度集成的双射频 (RF) 输入、零中频 (IF)/低 IF RFIC 接收器,具有正交解调器、数字步进衰减器 (DSA)、IF 线性放大器、集成式小数分频锁相环 (PLL) 和低相位噪声多核压控振荡器 (VCO)。RFIC 非常适合数字预失真 (DPD) 系统通信。

ADRF6821 配有高度隔离的 2:1 RF 开关和片内宽带 RF balun,支持两个单端 50 Ω 终止 RF 输入。可编程衰减器确保高线性度解调器内核具有优质的差分 RF 输入电平。集成衰减器提供 15 dB 的衰减范围,步进大小为 1 dB。高线性度 IF 放大器跟在解调器之后,为链中的下一元件 — 通常是模数转换器 (ADC) — 提供接口。

ADRF6821 提供两种生成差分本地振荡器 (LO) 输入信号的方法:通过具有低相位噪声 VCO 的片内小数分频频率合成器在内部生成,或通过相位噪声 LO 信号在外部生成。集成合成器的连续 LO 覆盖范围为 450 MHz 到 2800 MHz。PLL 基准输入支持频率范围宽广,并且在相位频率检测器 (PFD) 之前有一个集成的基准分频器。

选择之后,内部小数分频频率合成器的输出由正交相位分路器分成 2 部分。从外部 LO 路径生成时,2× LO 信号可由正交相位分路器分成 2 部分,以生成混频器的正交 LO 输入。

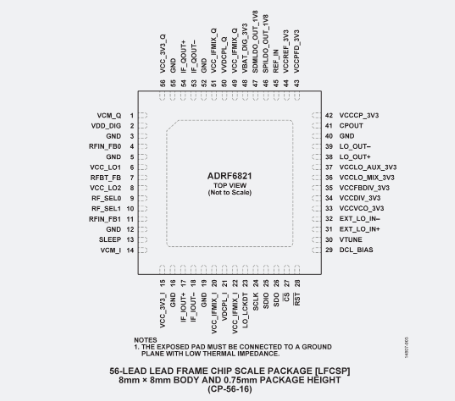

ADRF6821 通过高级硅锗 (SiGe)、双极互补金属氧化物半导体 (BiCMOS) 工艺制成,采用符合 RoHS 的 56 引脚、8 mm × 8 mm LFCSP 封装以及裸焊盘。性能是在 −40°C 至 +105°C 温度范围内标称。

应用

蜂窝 W-CDMA/GSM/LTE

DPD 接收器

微波点对点无线电

特性

具有集成式小数分频 PLL 的 DPD 接收器

RF 输入频率范围:450 MHz 到 2800 MHz

内部 LO 输入频率范围:450 MHz 到 2800 MHz

双 RF 输入具有 SPDT 吸收式 RF 开关

集成式 RF balun 适用于单端 50 Ω 输入

集成式 VCO 可覆盖整个 RF 输入范围

数字可编程 LO 相位偏移和 dc 调零

可通过 4 线 SPI 编程

56 引脚 8 mm × 8 mm LFCSP

第二章:产品概述

ADRF6821 是一款高性能、宽带射频零中频/低中频接收 RFIC,集成了双路射频输入、四相检波解调、数字步进衰减、IF 线性放大、分数分频锁相环和多核压控振荡器。该器件采用先进的硅锗 BiCMOS 工艺,支持 –40°C 至 +105°C 的宽温度范围,封装形式为 56 引脚、8 mm × 8 mm 的 LFCSP,便于在有限面积内实现高密度射频前端设计。

第三章:器件基本架构

ADRF6821 的整体架构可分为五大模块:

射频输入与开关模块:采用集成式 2:1 吸收型 RF 开关,支持两路单端 50 Ω 终端射频输入;

射频变压器与移频解调模块:内部宽带 RF 平衡至差分变压器,后接四相检波混频器,可实现零中频或低中频输出;

数字步进衰减模块:提供最多 15 dB 的衰减范围,步长 1 dB,确保进入解调器的差分信号电平在最佳线性范围;

中频放大与滤波模块:高线性 IF 放大器结合可编程低通滤波,为后续 ADC 或数字解调提供平衡驱动;

本振信号源与锁相环模块:内置分数分频锁相环及多核压控振荡器,覆盖 450 MHz 至 2800 MHz 的 LO 生成,或接受外部 LO 驱动。

第四章:集成式分数分频锁相环

ADRF6821 内部的分数分频锁相环(PLL)由相位频率检测器(PFD)、电荷泵、环路滤波器网络以及分频模/分频器构成。其核心优势在于:

大范围的参考频率支持,使设计者能够灵活选择晶振或外部参考;

精细的分数分频控制,实现 LO 频率微调,满足现代蜂窝通信中对频率精度和相位噪声的严格需求;

内置可编程参考分频器和反馈分频器,降低外部元件数量与系统布局复杂度。

第五章:多核压控振荡器(VCO)

VCO 模块采用多核设计,以覆盖从 450 MHz 到 2800 MHz 的射频输入范围,并提供 2 倍倍频输出能力至 900 MHz 至 5600 MHz。本振输出的性能指标包括:

低相位噪声:在成品设计中可满足 < –110 dBc/Hz @ 1 MHz 偏移的要求;

宽频带调谐:通过调谐电压 VTUNE 可实现连续频率覆盖;

稳定性与温度补偿:工艺和电路设计保证在宽温度范围内保持频率稳定,减小温漂。

第六章:数字预失真(DPD)功能

ADRF6821 专为与数字预失真处理器配合使用而设计,其高线性解调和宽带 IF 驱动能力,为 DPD 算法在基带数字信号处理器中提供精确采样和误差反馈。主要特点包括:

零中频或低中频输出灵活选择,兼容多种 DPD 架构;

较高的输入 1 dB 压缩点(IP1dB > +10 dBm),确保接收链在高功率下仍具备优秀线性;

可编程 DC 偏置和相位偏移校正,通过 SPI 接口快速配置,以配合不同放大器的特性。

第七章:射频输入与开关设计

器件内置的集成射频开关具备高隔离度和低插入损耗,实现双通道射频切换而无需外部开关。设计要点如下:

射频输入必须 AC 耦合,确保 DC 偏置分离;

外部 50 Ω 匹配网络设计可根据实际板级布局进行微调;

推荐在输入采样处添加微带滤波,抑制带外干扰并改善信号纯净度。

第八章:中频放大与输出接口

中频输出部分包括平衡差分放大器和可编程低通滤波器,可配置带宽高达 500 MHz。

差分输出驱动 ADC:为下一级 ADC 或数字解调芯片直接提供低阻抗差分信号;

带宽与增益可通过寄存器设置:设计者可依据系统带宽需求和信号功率级别灵活配置。

第九章:寄存器编程与数字接口

ADRF6821 通过四线串行外设接口(SPI)进行寄存器编程,主要包括:

时钟信号 SCLK、数据输入 SDIO、数据输出 SDO 与片选 CS;

10 位或 14 位可编程寄存器,用于配置 PLL 分频比、衰减值、相位偏移、DC 校正等;

软件提供 ACE(Analysis Control Evaluation)工具,支持图形化配置与快速评估。

第十章:性能指标

在典型工作条件下,ADRF6821 主要性能参数如下:

射频输入范围:450 MHz 至 2800 MHz;

本振输出范围:900 MHz 至 5600 MHz;

相位噪声:–110 dBc/Hz @ 1 MHz 偏移(典型);

1 dB 压缩点:+10 dBm(RF 输入);

互调失真(IMD3):< –70 dBc;

工作电压:3.3 V 核心电源,5.6 V 推荐电源;

功耗:典型 600 mW。

第十一章:典型应用场景

ADRF6821 广泛应用于:

蜂窝基站和室内分布系统(DAS)中的数字预失真接收模块;

微波点对点无线电链路;

多模多频无线宽带接入设备(WiMAX、LTE、5G NR 异构网络);

测试与测量仪器中的宽带信号分析前端。

第十二章:PCB 布局与电路设计注意事项

为了充分发挥 ADRF6821 的性能,版图设计需关注:

电源去耦:在各电源管脚附近放置低 ESR 陶瓷电容和阻抗匹配良好的地平面;

射频路径:使用 50 Ω 微带线或带状线,避免信号转角和不必要的 vias;

接地:射频地与数字地分区,并在适当位置进行匝间连接,减少环路面积;

温度管理:在高功率环境下,需考虑 PCB 散热、热过孔分布与散热铜皮设计。

第十三章:FPGA 与 ADC 接口设计

结合 FPGA 或专用 DPD 处理器,设计者需:

确保 IF 信号带宽匹配 ADC 采样率;

在 ADC 前加入抗混叠滤波;

在 FPGA 中实现高精度定时与相位校正,利用 ADRF6821 提供的相位偏移和 DC 校正功能,简化数字校准算法。

第十四章:评估板(EVAL-Z)介绍

ADRF6821-EVALZ 评估板提供即插即用功能:

集成 SDP‑S 控制接口,可通过 ACE 软件实现一键配置;

5.6 V 单电源供电,板载 LDO 提供 3.3 V,兼容实验室环境;

SMA 射频连接器与分立元件布局,使工程师快速验证器件性能并优化系统。

第十五章:未来发展与趋势

随着 5G NR、毫米波通信和大规模天线阵列技术演进,射频前端将向更高带宽、更低功耗和更智能化方向发展。ADRF6821 代表了集成分立元件向高集成度 RFIC 的趋势。在未来,还可通过:

增加 PLL 数字化控制精度;

引入更先进的 GaN 或 SiGe 工艺以提升线性;

将更多射频前端功能集成于同一芯片,实现更小尺寸和更高密度的基站设备。

第十六章:总结

ADRF6821 以其宽频覆盖、低相位噪声、高线性和高集成度,为通信 DPD 接收系统提供了理想的解决方案。通过深入了解其架构、功能和设计要点,系统工程师可在射频前端设计中最大化性能,提升无线通信系统效率与稳定性。无论是在蜂窝基站、宽带接入还是专业测试设备中,ADRF6821 均展现出广阔的应用前景。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)