基于AT89S52单片机和ENC624J600网络控制芯片的嵌入式Web控制系统设计方案

249

249

拍明

拍明

原标题:以52单片机为核心处理器的嵌入式Web控制系统设计方案

当前工业控制系统中流行的控制方式:底层设备采用RS232总线结构,而上层的管理层一般采用以太网结构。该控制方式使信号可以在企业的Intranet上及时发布和共享,还可以在Internet/Intranet的任何位置对现场智能设备进行在线控制、功能组态以及远程诊断等,实现了控制网络真正意义上的开放性和互操作性。而RS485总线是一种基于平衡发送和差分接收的串行总线,具有很强的抗共模干扰能力,在适当的波特率下传输距离很远。同时由于其硬件设计简单、控制方便、易于进行网络扩展,被广泛的应用在很多工业现场。

本文所研究的嵌入式以太网适配器,就是要解决嵌入式设备网络通信的问题,方便嵌入式系统与计算机网络的通信,实现远程监控、访问及数据的传输。

一、主要芯片选择及简介

1、单片机AT89S52

本设计中AT89S52作为核心处理器。AT89S52是Atmel公司生产的低功耗、高性能CMOS8位单片机,片内含有8k字节的EPROM和256字节的RAM。具有ISP(在系统编程)功能。它具有灵活性高、使用方便、价格低廉等优点。因此,该芯片在嵌入式控制系统中得到了广泛应用。单片机AT89S52经过以太网传到PC机实现远程控制。利用AT89S52的ISP(在系统编程)功能,很方便地把编好的程序写到单片机中,并且调试、修改和升级很容易。由于AT89S52单片机本身提供了一组全双工串行传输口,由TXD引脚来传送串行数据,而由RXD引脚来接收数据,可是其工作逻辑电平皆为TTL电平(0V,5V)。AT89S52最小系统如图1所示。

图1 AT89S52最小系统

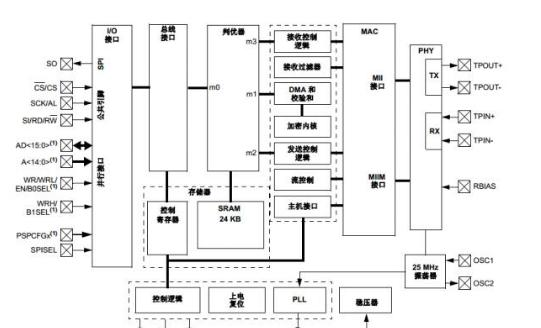

2、网络控制芯片ENC624J600

ENC624J600网络控制器是一款带有行业标准串行接口和并行接口的,专为嵌入式应用系统设计的独立以太网控制芯片。ENC624J600通过SPI或并行接口与单片机通信,数据传输速率为14Mbit/s(对于SPI)至160Mbit/s(对于16位的并行接口),ENC624J600主要功能特性有,自适应的选择传输速率,支持10Mbit/s或100Mbit/s;充分支持半双工或全双工交换式以太网;可编程填充和CRC生成;提供24KBA片内RAM缓冲区,用于执行发送和接手操作,主单片机还可以用它来进行常规的存储操作;支持总线8位或16位CPU访问,可编程自动拒绝错误数据包;可编程为发生冲突时自动重发。

ENC624J600器件符合IEEE 802.3中适用于10 Base-T 和100 Base-TX 以太网的全部规范,包括许多可选条款,例如自动协商。ENC624J600器件采用了一系列数据包过滤机制以对传入数据包进行限制。它还提供了一个16位宽的内部DMA以实现快速数据吞吐和硬件IP校验和计算支持。对于需要SSL、TLS 以及其他与加密相关的协议的安全和身份验证功能的应用,提供了一个安全引擎模块。 该引擎可执行RSA、Diffie- Hellman、AES、MD5 和SHA-1 算法计算,以缩短代码大小、加快连接的建立和吞吐,并减少固件开发的工作量。通过SPI或并行接口与单片机通信,数据传输速率为14 Mbit/s(对于SPI)至160 Mbit/s (对于16 位解复用并行接口)。提供了专用于LED 连接、活动指示以及发送/接收/DMA 中断的引脚。提供了一个通用24 KB片内RAM缓冲区,用于执行发送和接收操作。主单片机还可以用它来进行常规存储操作。通信协议(例如TCP)可使用此存储器保存可能需要重新发送的数据。在最终产品易于生产性方面,ENC624J600 系列的每个器件都预编程了唯一的非易失性MAC地址。在大多数情况下,这使最终器件省去了串行编程步骤,图2给出了器件的一般框图。

图2 ENC624J600的框图

3、外部数据存储器FM1808

FM1808是基于铁电存储器原理制造的并行接口256Kbit铁电存储器,FM1808的主要特性如下:采用先进的铁电技术制造;存储容量为256Kbit;读写寿命为100亿次;掉电数据可保存10年;写数据无延时;存取时间为70ns;低功耗,工作电流为25mA,待机电流仅为20uA;采用单5V工作电压;工作温度范围为-40℃~+85℃;具有特别优良的防潮湿、防电击及抗震性能;与SRAM或并行EEPROM管脚兼容。

二、硬件电路设计

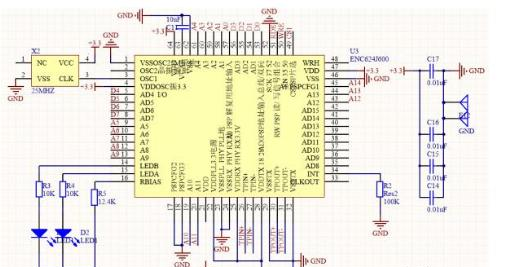

1、AT89S52与以太网控制器连接电路的设计

本系统里,P0口被作为低8位地址/数据复用,当作数据线使用时用来连接NC624J600的8位数据接口。当作为地址线使用时,为了给ENC624J600提供15位地址的低8位,要采用复用技术,对地址和数据进行分离。因此P0口连接到74ls373的D0~D7,把低8位地址暂存,随后有地址锁存器的O0~O7给ENC624J600提供15位地址的低8位,而高7位由P2口通过74ls245提供,如图3所示。

要使与单片机的接口具有高度的灵活性,ENC624J600器件提供了两种选择:基于串行外设接口(SPI)标准的串行接口和灵活的8/16位并行从端口接口。在任何给定时间只能使用一个接口。本课题中,AT89S52单片机和ENC624J600的连接选择PSP接口,如图3所示。要选择PSP接口,则在上电时通过INT/ SPISEL引脚上的SPISEL功能由硬件选择I/O接口。要完成此操作,需在向器件供电且器件退出上电复位状态后将施加到该引脚的电平约锁存1至10μs。如果SPISEL被锁存在逻辑高电平状态,将使能串行接口。如果SPISEL被锁存在逻辑低电平状态,则使能PSP接口。

图3 AT89S52与以太网控制器连接电路的设计

2、AT89S52和与外部扩展存储器FM1808的电路设计

AT89S52与FM1808的连接与AT89S52与NC624J600的连接类似,P0口被作为低8位地址/数据复用,当作数据线使用时用来连接FM1808的8位数据。当作为地址线使用时,采用复用技术,对地址和数据进行分离,给FM1808提供15位地址的低8位,而高7位由P2口通过74ls245提供,如图4所示。

图4 AT89S52和与外部扩展存储器FM1808的电路设计

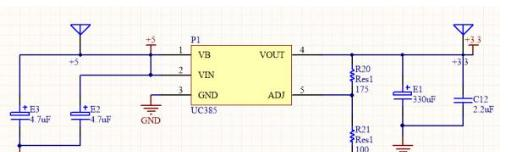

3、电源电路设计

电源模块是一块电路板最为基本的组成部分,只有稳定可靠的电源为板上芯片供电才能够保证各功能模块的正常工作,因此在电源模块的设计时首先应该初步计算电路板所有元件的功耗,然后在保证功耗的前提下选择相应的芯片进行直流电源模块设计,尽量做到体积小,重量轻;性价比合理;能长期稳定、可靠地工作。

本适配器所需要的电源有3.3V。系统需要3.3V电源供电的芯片以太网控制器等。考虑到系统可能工作于高速通信模式,消耗电流会非常大,所以选用1片UC385芯片,每片UC385输出电流可达800mA,可以完全满足系统的需求。具体电路如图5所示 。

图5 电源模块设计

三、软件部分设计

1、主函数

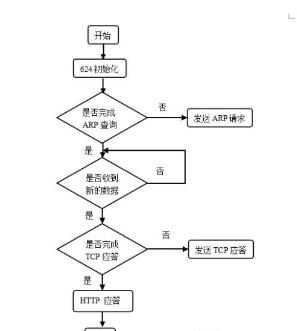

上电先查询ARP,若未获取MAC,则发送ARP请求。若有新的数据,若TCP应答没有完成,则应答TCP,完成TCP三次握手。然后根据请求类型响应HTTP。

2、TCP应答部分

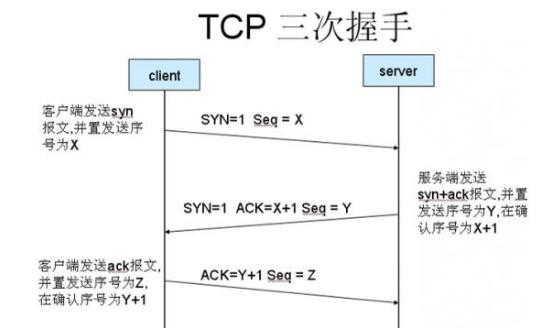

1) 三次握手阶段

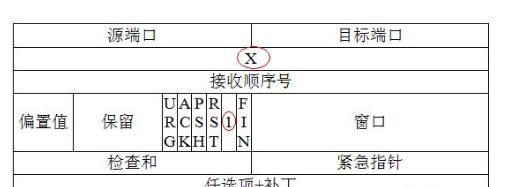

所谓三次握手(Three-way Handshake),是指建立一个TCP连接时,需要客户端和服务器总共发送3个包。三次握手的目的是连接服务器指定端口,建立TCP连接,并同步连接双方的序列号和确认号并交换 TCP 窗口大小信息。

图6 三次握手(Three-way Handshake)

第一次握手:客户端发送一个TCP的SYN标志位置1的包指明客户打算连接的服务器的端口,以及初始序号X,保存在包头的序列号(Sequence Number)字段里。

图7 第一次握手

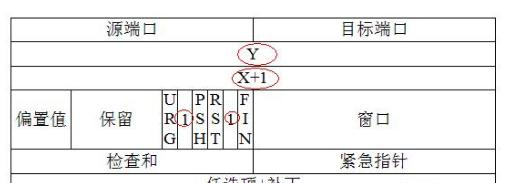

第二次握手:服务器发回确认包(ACK)应答。即SYN标志位和ACK标志位均为1同时,将确认序号(Acknowledgement Number)设置为客户的ISN加1以。即X+1。

第三次握手,客户端再次发送确认包(ACK) SYN标志位为0,ACK标志位为1.并且把服务器发来ACK的序号字段+1,放在确定字段中发送给对方。并且在数据段放写ISN的+1

图9 第三次握手

其实在握手和结束时确认号应该是对方序列号加1,传输数据时则是对方序列号加上对方携带应用层数据的长度。

在传输TCP分包的过程中也是需要发送一分包,确认一分包的,而TCP确认包只有54字节,就是只有头部信息。因此在传输TCP分包序列号一直不变,确认号按发送数据的长度递增即可。

3、 HTTP

1)请求

连接成功建立后,开始向web服务器发送请求,这个请求一般是GET或POST命令(POST用于FORM参数的传递)。GET命令的格式为:GET 路径/文件名 HTTP/1.0文件名指出所访问的文件,HTTP/1.0指出Web浏览器使用的HTTP版本。现在可以发送GET命令:GET /mytest/index.html HTTP/1.0,

2)应答

web服务器收到这个请求,进行处理。从它的文档空间中搜索子目录mytest的文件index.html。如果找到该文件,Web服务器把该文件内容传送给相应的Web浏览器。为了告知浏览器,Web服务器首先传送一些HTTP头信息,然后传送具体内容(即HTTP体信息),HTTP头信息和HTTP体信息之间用一个空行分开。常用的HTTP头信息有:

① HTTP 1.0 200 OK 这是Web服务器应答的第一行,列出服务器正在运行的HTTP版本号和应答代码。代码“200 OK”表示请求完成。

② MIME_Version:1.0 它指示MIME类型的版本。

③ content_type:类型 这个头信息非常重要,它指示HTTP体信息的MIME类型。如:content_type:text/html指示传送的数据是HTML文档。

④ content_length:长度值 它指示HTTP体信息的长度(字节)。

3)关闭连接

当应答结束后,Web浏览器与Web服务器必须断开,以保证其它Web浏览器能够与Web服务器建立连接。

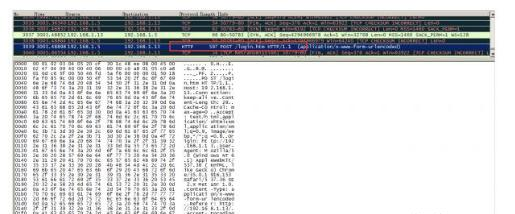

4、提交表单GET/POST

GET请求的数据会附在URL之后(就是把数据放置在HTTP协议头中),以?分割URL和传输数据,参数之间以&相连,如:login.acTIon?name=hyddd&password=idontknow&verify=%E4%BD%A0%E5%A5%BD。如果数据是英文字母/数字,原样发送,如果是空格,转换为+,如果是中文/其他字符,则直接把字符串用BASE64加密,得出如:%E4%BD%A0%E5%A5%BD,其中%XX中的XX为该符号以16进制表示的ASCII。

POST把提交的数据则放置在是HTTP包的包体中。在FORM(表单)中,Method默认为“GET”。

本文中登录时提交表单数据采用的是POST方式,而提交控制信息表单时用的是GET。以下是用抓包的方式明显看出他们的不同之处。

图10 POST方式

图11 GET方式

图12 GET方式是提交的数据直接放在URL中了

5、总体软件设计

AT89S52单片机首先对ENC624J600进行初始化,首先应查询ESTAT寄存器的CLKRDY位,确保在配置MAC和PHY寄存器前有足够的延时;PHY寄存器用来设置通信模式;编程ERXST和ERXND指针对接收缓冲器进行初始化,当编程ERXST指针时,相同的值会自动更新ERXWRPT寄存器,接收硬件将从ERXWRPT中的地址开始写入已收到的数据,为跟踪接收的数据,ERXRDPT寄存器也需要用相同的值编程;为了能最大限度地降低主控制器的处理工作量,ENC624J600配备了不同的过滤器,可自动拒绝不需要的数据包,所有的过滤器都由ERXFCON寄存器进行配置,可以使用ANDOR位对几个过滤器的测试结果作逻辑/与0或逻辑/或0运算;由于未被用作接收缓冲器的存储空间都作为发送缓冲器,所以不需要对发送缓冲器进行特定的初始化,通常将存储空间分配为大的接收缓冲器空间和较小的接收存储空间。

在初始化完成后,即进入主循环程序,单片机将反复检测ENC624J600是否接收到以太网帧(或者数据缓冲区B中有数据需要发送),当有数据接收(或者发送)时则根据标志位进行相应的子函数处理,将数据存入数据缓冲区(或者发送至以太网上)。主程序流程如图13所示。

【AT89S52】

AT89S52是一种低功耗、高性能CMOS 8位微控制器,具有8K 系统可编程Flash 存储器。使用Atmel 公司高密度非易失性存储器技术制造,与工业80C51 产品指令和引脚完全兼容。片上Flash允许程序存储器在系统内编程,亦适于常规编程器。在单芯片上,拥有灵巧的8 位CPU 和在系统可编程Flash,使得AT89S52在众多嵌入式控制应用系统中得到广泛应用。

主要性能

1、与MCS-51单片机产品兼容;

2、8K字节在系统可编程Flash存储器;

3、1000次擦写周期;

4、全静态操作:0Hz-33MHz;

5、三级加密程序存储器;

6、32个可编程I/O口线;

7、三个16位定时器/计数器;

8、6个中断源;

9、全双工UART串行通道;

10、低功耗空闲和掉电模式;

11、掉电后中断可唤醒;

12、看门狗定时器;

13、双数据指针;

14、掉电标识符。

引脚说明

AT89S52 是一种低功耗、高性能CMOS8位微控制器,具有8K 在系统可编程Flash存储器。使用Atmel 公司高密度非易失性存储器技术制造,与工业80C51 产品指令和引脚完全兼容。片上Flash允许程序存储器在系统可编程,亦适于常规编程器。在单芯片上,拥有灵巧的8 位CPU 和在系统可编程Flash,使得AT89S52为众多嵌入式控制应用系统提供高灵活、超有效的解决方案。 AT89S52具有以下标准功能: 8k字节Flash,256字节RAM, 32 位I/O 口线,看门狗定时器,2 个数据指针,三个16 位 定时器/计数器,一个6向量2级中断结构,全双工串行口。另外,AT89S52 可降至0Hz 静态逻 辑操作,支持2种软件可选择节电模式。空闲模式下,CPU 停止工作,允许RAM、定时器/计数器、串口、中断继续工 作。掉电保护方式下,RAM内容被保存,振荡器被冻结,单片机一切工作停止,直到下一个中断或硬件复位为止。

P0 口

P0口是一个8位漏极开路的双向I/O口。作为输出口,每位能驱动8个TTL逻 辑电平。对P0端口写“1”时,引脚用作高阻抗输入。 当访问外部程序和数据存储器时,P0口也被作为低8位地址/数据复用。在这种模式下, P0不具有内部上拉电阻。 在flash编程时,P0口也用来接收指令字节;在程序校验时,输出指令字节。程序校验 时,需要外部上拉电阻。

P1 口

P1 口是一个具有内部上拉电阻的8 位双向I/O 口,p1 输出缓冲器能驱动4 个 TTL 逻辑电平。

此外,P1.0和P1.1分别作定时器/计数器2的外部计数输入(P1.0/T2)和定时器/计数器2 的触发输入(P1.1/T2EX)。 在flash编程和校验时,P1口接收低8位地址字节。

引脚号第二功能:

P1.0 T2(定时器/计数器T2的外部计数输入),时钟输出

P1.1 T2EX(定时器/计数器T2的捕捉/重载触发信号和方向控制)

P1.5 MOSI(在系统编程用)

P1.6 MISO(在系统编程用)

P1.7 SCK(在系统编程用)

P2 口

P2 口是一个具有内部上拉电阻的8 位双向I/O 口,P2 输出缓冲器能驱动4 个 TTL 逻辑电平。对P2 端口写“1”时,内部上拉电阻把端口拉高,此时可以作为输入 口使用。作为输入使用时,被外部拉低的引脚由于内部电阻的原因,将输出电流(IIL)。 在访问外部程序存储器或用16位地址读取外部数据存储器(例如执行MOVX @DPTR) 时,P2 口送出高八位地址。在这种应用中,P2 口使用很强的内部上拉发送1。在使用 8位地址(如MOVX @RI)访问外部数据存储器时,P2口输出P2锁存器的内容。 在flash编程和校验时,P2口也接收高8位地址字节和一些控制信号。

P3 口

P3 口是一个具有内部上拉电阻的8 位双向I/O 口,p3 输出缓冲器能驱动4 个 TTL 逻辑电平。 P3口亦作为AT89S52特殊功能(第二功能)使用,如下表所示。 在flash编程和校验时,P3口也接收一些控制信号。

端口引脚第二功能:

P3.0 RXD(串行输入口)

P3.1 TXD(串行输出口)

P3.2 INTO(外中断0)

P3.3 INT1(外中断1)

P3.4 TO(定时/计数器0)

P3.5 T1(定时/计数器1)

P3.6 WR(外部数据存储器写选通)

P3.7 RD(外部数据存储器读选通)

此外,P3口还接收一些用于FLASH闪存编程和程序校验的控制信号。

RST

复位输入。当振荡器工作时,RST引脚出现两个机器周期以上高电平将使单片机复位。

ALE/PROG

当访问外部程序存储器或数据存储器时,ALE(地址锁存允许)输出脉冲用于锁存地址的低8位字节。一般情况下,ALE仍以时钟振荡频率的1/6输出固定的脉冲信号,因此它可对外输出时钟或用于定时目的。要注意的是:每当访问外部数据存储器时将跳过一个ALE脉冲。对FLASH存储器编程期间,该引脚还用于输入编程脉冲(PROG)。如有必要,可通过对特殊功能寄存器(SFR)区中的8EH单元的D0位置位,可禁止ALE操作。该位置位后,只有一条MOVX和MOVC指令才能将ALE激活。此外,该引脚会被微弱拉高,单片机执行外部程序时,应设置ALE禁止位无效。

PSEN

程序储存允许(PSEN)输出是外部程序存储器的读选通信号,当AT89S52由外部程序存储器取指令(或数据)时,每个机器周期两次PSEN有效,即输出两个脉冲,在此期间,当访问外部数据存储器,将跳过两次PSEN信号。

EA/VPP

外部访问允许,欲使CPU仅访问外部程序存储器(地址为0000H-FFFFH),EA端必须保持低电平(接地)。需注意的是:如果加密位LB1被编程,复位时内部会锁存EA端状态。如EA端为高电平(接Vcc端),CPU则执行内部程序存储器的指令。FLASH存储器编程时,该引脚加上+12V的编程允许电源Vpp,当然这必须是该器件是使用12V编程电压Vpp。

寄存器

并不是所有的地址都被定义了。片上没有定义的地址是不能用的。读这些地址,一般将得到一

AT89S52 特殊寄存器映象及复位值

AT89S52 特殊寄存器映象及复位值

个随机数据;写入的数据将会无效。

用户不应该给这些未定义的地址写入数据“1”。由于这些寄存器在将来可能被赋予新的功能,复位后,这些位都为“0”。

定时器2寄存器:寄存器T2CON 和T2MOD 包含定时器2 的控制位和状态位(如表2和表3所示),寄存器对RCAP2H和RCAP2L是定时器2的捕捉/自动重载寄存器。

中断寄存器:各中断允许位在IE寄存器中,六个中断源的两个优先级也可在IE中设置。

表2 T2CON:定时器/计数器2控制寄存器

T2CON 地址为0C8H 复位值:0000 0000B位可寻址

TF2 | EXF2 | RLCLK | TCLK | EXEN2 | TR2 | C/T2 | CP/RL2 |

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

符号 | 功能 |

TF2 | 定时器2 溢出标志位。必须软件清“0”。RCLK=1 或TCLK=1 时,TF2不 用置位。 |

EXF2 | 定时器2 外部标志位。EXEN2=1 时,T2EX 上的负跳变而出现捕捉或重载 时,EXF2 会被硬件置位。定时器2 打开,EXF2=1 时,将引导CPU执行定 时器2 中断程序。EXF2 必须软件清“0”。在向下/向上计数模式(DCEN=1) 下EXF2不能引起中断。 |

RLCLK | 串行口接收数据时钟标志位。若RCLK=1,串行口将使用定时器2 溢出脉冲 作为串行口工作模式1 和3 的串口接收时钟;RCLK=0,将使用定时器1计数 溢出作为串口接收时钟。 |

TCLK | 串行口发送数据时钟标志位。若TCLK=1,串行口将使用定时器2 溢出脉冲作 为串行口工作模式1 和3 的串口发送时钟;TCLK=0,将使用定时器1计数溢出 作为串口发送时钟。 |

EXEN2 | 定时器2外部允许标志位。当EXEN2=1时,如果定时器2没有用作串行时钟, T2EX(P1.1)的负跳变将引起定时器2 捕捉和重载。若EXEN2=0,定时器2 将视T2EX端的信号无效 |

TR2 | 开始/停止控制定时器2。TR2=1,定时器2开始工作 |

C/T2 | 定时器 2 定时/计数选择标志位。C/T2 =0,定时; C/T2 =1,外部事件计 数(下降沿触发) |

CP/RL2 | 捕捉/重载选择标志位。当EXEN2=1时, CP/RL2=1,T2EX出现负脉冲,会引 起捕捉操作;当定时器2溢出或EXEN2=1时T2EX出现负跳变,都会出现自动重载 操作。CP/RL2=0 将引起T2EX 的负脉冲。当RCKL=1或TCKL=1时,此标志位 无效,定时器2溢出时,强制做自动重载操作。 |

双数据指针寄存器:为了更有利于访问内部和外部数据存储器,系统提供了两路16位数据指针寄存器:位于SFR中82H~83H的DP0和位于84H~85。特殊寄存器AUXR1中DPS=0 选择DP0;DPS=1 选择DP1。用户应该在访问数据指针寄存器前先初始化DPS至合理的值。

表 3a AUXR:辅助寄存器

AUXR 地址:8EH 复位值:XXX00XX0B不可位寻址

WDIDLE | DISRTO | DISALE | |||||

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

预留扩展用

DISALE ALE使能标志位

DISALE 操作方式

0 ALE 以1/6晶振频率输出信号

1 ALE 只有在执行MOVX 或MOVC指令时激活

DISRTO 复位输出标志位

DISRTO

0看门狗(WDT)定时结束,Reset 输出高电平

1 Reset 只有输入

WDIDLE 空闲模式下WDT 使能标志位

WDIDLE

0 空闲模式下,WDT继续计数

1 空闲模式下,WDT停止计数

掉电标志位:掉电标志位(POF)位于特殊寄存器PCON的第四位(PCON.4)。上电期间POF置“1”。POF可以软件控制使用与否,但不受复位影响。

表 3b AUXR1:辅助寄存器1

AUXR1 地址:A2H 复位值:XXXXXXX0B

不可位寻址

DPS | |||||||

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

预留扩展用

DPS 数据指针选择位

DPS

0 选择DPTR寄存器DP0L和DP0H

1 选择DPTR寄存器DP1L和DP1H

存储器编辑

MCS-51器件有单独的程序存储器和数据存储器。外部程序存储器和数据存储器都可以64K寻址。

程序存储器:如果EA引脚接地,程序读取只从外部存储器开始。

对于 89S52,如果EA 接VCC,程序读写先从内部存储器(地址为0000H~1FFFH)开始,接着从外部寻址,寻址地址为:2000H~FFFFH。

数据存储器:AT89S52 有256 字节片内数据存储器。高128 字节与特殊功能寄存器重叠。也就是说高128字节与特殊功能寄存器有相同的地址,而物理上是分开的。

当一条指令访问高于7FH 的地址时,寻址方式决定CPU 访问高128 字节RAM 还是特殊功能寄存器空间。直接寻址方式访问特殊功能寄存器(SFR)。

例如,下面的直接寻址指令访问0A0H(P2口)存储单元MOV 0A0H , #data使用间接寻址方式访问高128 字节RAM。例如,下面的间接寻址方式中,R0 内容为0A0H,访问的是地址0A0H的寄存器,而不是P2口(它的地址也是0A0H)。

MOV @R0 , #data堆栈操作也是间接寻址方式。因此,高128字节数据RAM也可用于堆栈空间。

片上资源

看门狗定时器

WDT是一种需要软件控制的复位方式。WDT 由13位计数器和特殊功能寄存器中的看门狗定时器复位存储器(WDTRST)构成。WDT 在默认情况下无法工作;为了激活WDT,用户必须往WDTRST寄存器(地址:0A6H)中依次写入01EH 和0E1H。当WDT激活后,晶振工作,WDT在每个机器周期都会增加。WDT计时周期依赖于外部时钟频率。除了复位(硬件复位或WDT溢出复位),没有办法停止WDT工作。当WDT溢出,它将驱动RSR引脚一个高电平输出。

WDT的使用为了激活WDT,用户必须向WDTRST寄存器(地址为0A6H的SFR)依次写入01EH和0E1H。当WDT激活后,用户必须向WDTRST写入01EH和0E1H喂狗来避免WDT溢出。当计数达到8191(1FFFH)时,13 位计数器将会溢出,这将会复位器件。晶振正常工作、WDT激活后,每一个机器周期WDT 都会增加。为了复位WDT,用户必须向WDTRST 写入01EH 和0E1H(WDTRST 是只读寄存器)。WDT计数器不能读或写。

当WDT计数器溢出时,将给RST引脚产生一个复位脉冲输出,这个复位脉冲持续96个晶振周期(TOSC),其中TOSC=1/FOSC。为了很好地使用WDT,应该在一定时间内周期性写入那部分代码,以避免WDT复位。

掉电和空闲方式下的 WDT在掉电模式下,晶振停止工作,这意味这WDT也停止了工作。在这种方式下,用户不必喂狗。有两种方式可以离开掉电模式:硬件复位或通过一个激活的外部中断。通过硬件复位退出掉电模式后,用户就应该给WDT喂狗,就如同通常AT89S52 复位一样。

通过中断退出掉电模式的情形有很大的不同。中断应持续拉低很长一段时间,使得晶振稳定。当中断拉高后,执行中断服务程序。为了防止WDT在中断保持低电平的时候复位器件,WDT 直到中断拉低后才开始工作。这就意味着WDT 应该在中断服务程序中复位。

为了确保在离开掉电模式最初的几个状态WDT不被溢出,最好在进入掉电模式前就复位WDT。

在进入待机模式前,特殊寄存器AUXR的WDIDLE位用来决定WDT是否继续计数。

默认状态下,在待机模式下,WDIDLE=0,WDT继续计数。为了防止WDT在待机模式下复位AT89S52,用户应该建立一个定时器,定时离开待机模式,喂狗,再重新进入待机模式。

UART

在AT89S52 中,UART 的操作与AT89C51和AT89C52一样。为了获得更深入的关于UART 的信息,选择“Products”,然后选择“8051-Architech Flash Microcontroller”,再选择“ProductOverview”即可。

定时器 0 和定时器1

在AT89S52 中,定时器0 和定时器1 的操作与AT89C51 和AT89C52 一样。为了获得更深入的关于UART 的信息,选择“Products”,然后选择“8051-Architech Flash Microcontroller”,再选择“ProductOverview”即可。

定时器 2

定时器2是一个16位定时/计数器,它既可以做定时器,又可以做事件计数器。其工作方式由特殊寄存器T2CON中的C/T2位选择(如表2所示)。定时器2有三种工作模式:

捕捉方式、自动重载(向下或向上计数)和波特率发生器。如表3 所示,工作模式由T2CON中的相关位选择。定时器2 有2 个8位寄存器:TH2和TL2。在定时工作方式中,每个机器周期,TL2寄存器都会加1。由于一个机器周期由12 个晶振周期构成,因此,计数频率就是晶振频率的1/12。表 3定时器2工作模式

RCLK+TCLK | CP/RL2 | TR2 | MODE |

0 | 0 | 1 | 16位自动重载 |

0 | 1 | 1 | 16位捕捉 |

1 | x | 1 | 波特率发生器 |

x | x | 0 | (不用) |

捕捉方式在捕捉模式下,通过T2CON中的EXEN2来选择两种方式。

如果EXEN2=0,定时器2时一个16位定时/计数器,溢出时,对T2CON 的TF2标志置位,TF2引起中断。如果EXEN2=1,定时器2做相同的操作。除上述功能外,外部输入T2EX引脚(P1.1)1至0的下跳变也会使得TH2和TL2中的值分别捕捉到RCAP2H和RCAP2L中。除此之外,T2EX 的跳变会引起T2CON 中的EXF2 置位。像TF2 一样,T2EX 也会引起中断。捕捉模式如图5所示。在计数工作方式下,寄存器在相关外部输入角T2 发生1 至0 的下降沿时增加1。在这种方式下,每个机器周期的S5P2期间采样外部输入。一个机器周期采样到高电平,而下一个周期采样到低电平,计数器将加1。在检测到跳变的这个周期的S3P1 期间,新的计数值出现在寄存器中。因为识别1-0的跳变需要2个机器周期(24个晶振周期),所以,最大的计数频率不高于晶振频率的1/24。为了确保给定的电平在改变前采样到一次,电平应该至少在一个完整的机器周期内保持不变。

自动重载当定时器2 工作于16 位自动重载模式,可对其编程实现向上计数或向下计数。这一功能可以通过特殊寄存器T2MOD(见表4)中的DCEN(向下计数允许位)来实现。通过复位,DCEN 被置为0,因此,定时器2 默认为向上计数。DCEN 设置后,定时器2就可以取决于T2EX向上、向下计数。

如图6 所示,DCEN=0 时,定时器2 自动计数。通过T2CON 中的EXEN2 位可以选择两种方式。如果EXEN2=0,定时器2计数,计到0FFFFH后置位TF2溢出标志。计数溢出也使得定时器寄存器重新从RCAP2H 和RCAP2L 中加载16 位值。定时器工作于捕捉模式,RCAP2H和RCAP2L的值可以由软件预设。如果EXEN2=1,计数溢出或在外部T2EX(P1.1)引脚上的1到0的下跳变都会触发16位重载。这个跳变也置位EXF2中断标志位。T2EX 上的一个逻辑0 使得定时器2 向下计数。当TH2 和TL2 分别等于RCAP2H 和RCAP2L中的值的时候,计数器下溢。计数器下溢,置位TF2,并将0FFFFH加载到定时器存储器中。如图6所示,置位DCEN,允许定时器2向上或向下计数。在这种模式下,T2EX引脚控制着计数的方向。T2EX上的一个逻辑1使得定时器2向上计数。定时器计到0FFFFH溢出,并置位TF2。定时器的溢出也使得RCAP2H和RCAP2L中的16位值分别加载到定时器存储器TH2和TL2中。

定时器2上溢或下溢,外部中断标志位EXF2 被锁死。在这种工作模式下,EXF2不能触发中断。

表 4 T2MOD-定时器2控制寄存器

T2MOD 地址:0C9H 复位值:XXXXXX00B

不可位寻址

T2OE | DCEN | ||||||

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

符号 | 功能 |

无定义,预留扩展 | |

定时器2输出允许位 | |

置1后,定时器2可配置成向上/向下计数 |

【ENC624J600】

10/100 Base-T/TX Ethernet Controller with SPI Interface

Device Overview

Summary

Microchip's ENC624J600 offers low-cost stand-alone 10/100 Base-T Ethernet interface controller with integrated MAC & PHY, hardware cryptographic security engines and factory preprogrammed unique MAC address. A 24-Kbyte on-chip RAM buffer is available for TX and RX operations. The ENC624J600 have an industry standard Serial Peripheral Interface (SPI) or a flexible parallel interface. They are designed to serve as an Ethernet network interface for any microcontroller equipped with SPI or a standard parallel port. Microchip’s ENC624J600 enables designers to create secured network- and Internet-connected embedded applications with minimized board space, cost and complexity.

Ethernet Application Design Center

Microchip's complimentary and confidential LANCheck® online design review services are available for customers who have selected our products for their application design-in*.

*The LANCheck online design review service is subject to Microchip's Program Terms and Conditions and requires a myMicrochip account.

Additional Features

IEEE 802.3™ Compliant Fast Ethernet Controller

Integrated MAC and 10/100Base-T

Hardware Security Acceleration Engines-

Factory Preprogrammed Unique MAC Address

Supports one 10/100Base-T Port with Automatic Polarity Detection and Correction

Support for Pause Control Frames, including Automatic Transmit and Receive Flow Control

Programmable Automatic Retransmit on Collision

14 Mbit/s SPI interface with enhanced set of opcodes- 8-bit multiplexed parallel interface- 8-bit or 16-bit multiplexed or demultiplexed parallel interface

High-performance, modular exponentiation engine with up to 1024-bit operands- Supports RSA® and Diffie-Hellman key exchange algorithms

Fast MD5 hash computations

Fast SHA-1 hash computations

Package:64-Pin (TQFP)

Parametrics

Name

Value

Description

10Based-T/100Based-TX Ethernet Controller with Security

Ethernet Bandwidth:10/100Mbps

MAC:Yes

PHY:Yes

TX/RX RAM Buffer(Bytes):24K

Interrupt Pin:1

LEDs:2

# Ethernet Ports:Ethernet x1

Temp. Range Min. (°C):-40

Temp. Range Max. (°C):85

Max Speed (MHz):25Mhz

Interface:SPI, Parallel

Vdd I/O (V):3.3

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)