什么是stm32f407vet6,stm32f407vet6的基础知识?

30

30

拍明芯城

拍明芯城

STM32F407VET6简介

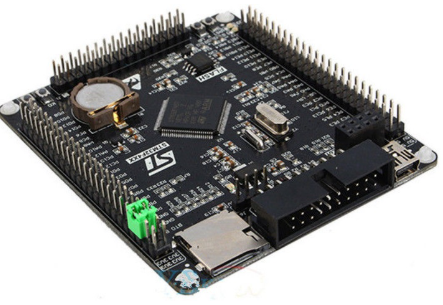

STM32F407VET6是意法半导体(STMicroelectronics)推出的一款基于ARM Cortex-M4内核的高性能微控制器,广泛应用于工业控制、消费电子、通讯设备、医疗仪器、智能家居等领域。该系列芯片具有主频高、外设丰富、功耗低等优势,可满足各种复杂嵌入式系统设计需求。本文将从概述、核心架构、主要特性、封装与引脚定义、电气特性与时钟系统、存储体系、外设模块、开发环境与工具链、工程设计要点、典型应用案例等方面进行详细介绍,力图为读者全面呈现STM32F407VET6的基础知识以及实际应用中的关键技术要点。

一、概述

STM32F407VET6属于STM32F4系列微控制器中的高端型号,采用ARM公司授权的Cortex-M4内核,最高主频可达168MHz,并集成了浮点运算单元(FPU),能够高效地进行浮点运算,适用于信号处理、控制算法等对计算能力要求较高的场景。该芯片内部整合了丰富的片上资源,包括多路通用和高级定时器、DMA控制器、多路USART/UART、SPI、I2C、CAN、SDIO、USB OTG、以太网MAC、图形加速器(Chrom-ART Accelerator)、双12位ADC、双12位DAC、硬件真随机数发生器以及加密加速单元等。由于功能强大且生态完善,STM32F407VET6成为众多设计者进行嵌入式系统开发的首选之一。

二、核心架构与计算性能

STM32F407VET6内部采用ARM Cortex-M4内核,主频最高可达168MHz,并包含32KB的一级指令缓存和四路指令预取队列,显著提升指令执行效率。同时,Cortex-M4核内置单精度浮点运算单元(FPU),支持IEEE754标准浮点运算,可大幅提高DSP算法以及复杂控制算法的执行速度。其内核支持哈佛结构体系,代码和数据分别通过不同的总线进行访问,减少总线争用,提高系统吞吐量。Cortex-M4内核还支持口令安全、硬件乘法器和除法器、嵌套向量中断控制器(NVIC)等,能够实现快速中断响应和精确实时控制,适合工业自动化、运动控制、机器人等严苛实时性领域的需求。

三、封装形式与引脚定义

STM32F407VET6主要采用LQFP100封装形式,也可见到部分BGA封装,但在开发板及样板设计中最常见的为LQFP100(14mm×14mm)封装。该封装提供了100个引脚,分别分布在四个侧面,每侧25个引脚。引脚定义包括电源引脚、时钟系统引脚、复位引脚、多路GPIO、外设功能引脚、晶振输入输出引脚以及调试接口(SWD、JTAG)。

电源与地引脚

VDD(电源输入):芯片核心和外设的供电电压范围为1.8V至3.6V,其中主供电通常为3.3V。

VSS(地):芯片地参考,需要在设计PCB时注意连接地平面,以降低噪声。

VDD_SRAM:专用SRAM供电引脚,需要外部连接至主供电3.3V,保证内部SRAM的稳定工作。

VBAT:备份电源输入,用于实时时钟(RTC)和备份寄存器当主电源掉电时仍能保持工作。

时钟与复位引脚

OSC_IN/OSC_OUT:外部高速晶振(HSE)输入和输出引脚,常见晶振频率为8MHz、12MHz或25MHz,可配置通过倍频器产生168MHz系统时钟。

PLL输入/输出:内部使用PLL倍频器,将外部或内部时钟信号倍频到需要的系统时钟值。

NRST:外部复位输入引脚,低电平有效,可通过按键或外部电路触发复位,使芯片进入初始化状态。

PC14、PC15:外部低速晶振(LSE)输入(PC14)、输出(PC15)引脚,用于外部32.768kHz晶振,为RTC提供低功耗时钟源。

调试与编程接口

SWDIO、SWCLK:串行线调试(Serial Wire Debug)接口的IO和时钟引脚,用于在线单线调试和编程。

JTAG(JTMS/SWDIO、JTCK/SWCLK、JTDI、JTDO、NJTRST):完整的JTAG六线调试接口,可进行核心寄存器查看、断点设置、单步调试等操作。

GPIO与复用功能引脚

LQFP100封装提供了82个通用输入输出引脚(GPIO),可配置为标准I/O、外部中断、外设功能复用等模式,不同引脚所在的引脚组(PORTA、PORTB、PORTC、PORTD、PORTE、PORTF、PORTG、PORTH、PORTI)具备不同的复用能力。例如:PA0至PA15:可配置为ADC、USART、SPI、TIM、CAN、I2S、FSMC等多种复用功能,用途灵活。

PB0至PB15:同样具备多路外设复用功能,可用于PWM输出、定时器输入捕获、I2C、SPI等。

PC0至PC15、PD0至PD15,依次类推,丰富的IO资源令应用配置更具灵活性。

四、时钟系统与电气特性

STM32F407VET6的时钟系统由内部高速振荡器(HSI,16MHz)、内部低速振荡器(LSI,32kHz)、外部高速晶振(HSE,可选4~26MHz以内)、外部低速晶振(LSE,32.768kHz)以及多级PLL倍频器组成。其时钟树结构可细分为:

内部高速振荡器(HSI)

HSI默认16MHz,可通过HSI校准寄存器进行微调。HSI可作为系统时钟源,也可为PLL提供输入时钟。优点在于启动时间短、无需外部元件、功耗较低;缺点是温度及工艺差异导致频率漂移较大,不适合对时钟精度要求高的应用。外部高速晶振(HSE)

HSE外部晶振通常选用8MHz、12MHz、16MHz或25MHz晶振,可通过PLL倍频至168MHz系统时钟。当系统对时钟精度要求高时,建议使用HSE作为主系统时钟源。PLL倍频方式支持多种倍频因子配置,以获得不同的系统时钟频率(如168MHz、144MHz、120MHz等)。使用HSE时需注意晶振电路的布局:晶振脚与地脚需尽量靠近,晶体两端布置负载电容,避免过长走线导致振荡不稳定。内部低速振荡器(LSI)与外部低速晶振(LSE)

LSI(32kHz)主要用于看门狗定时器(IWDG)与实时时钟(RTC)的工作时钟,但其频率精度较低,仅适合对时间精度要求不高的看门狗场景。LSE(32.768kHz)外部石英晶振可提供高精度32kHz时钟,专用于RTC,保证在低功耗模式下也能维持准确的时钟计时。LSE启动时间较长,一般需要数十毫秒,在应用设计中需预留启动等待时间。PLL倍频器配置

STM32F407VET6内部包含两个PLL模块:PLLM(主PLL)和PLLI2S(用于音频时钟)。主要使用主PLL将输入时钟倍频到168MHz系统时钟,其计算公式为:SYSCLK = (PLL输入频率 / PLLM) × PLLN / PLLP

其中,PLL输入频率可选HSI(16MHz)或HSE(如8MHz);PLLM可配置范围为2~63;PLLN可配置范围为50~432;PLLP可配置为2、4、6、8,对应PLL输出分频系数。通过合理配置上述参数,可将8MHz HSE倍频为168MHz系统时钟,也可将HSE倍频为不同外设所需的时钟频率,如SDIO、USB需48MHz时钟、I2S需特定音频频率时钟等;使用PLLI2S即可产生I2S音频所需的高精度时钟。电气特性与功耗

STM32F407VET6典型工作电压为3.3V,允许范围为1.8V~3.6V,片上集成多个电压调节器和电源监控模块,可对电源掉电、复位时序进行监测。其不同工作模式下的电流消耗差异较大:运行模式(Run Mode):在168MHz主频、全外设开启情况下,典型电流约为95mA左右,实际与外设工作状态相关。

睡眠模式(Sleep Mode):CPU停机,仅保留外设时钟,可降低功耗至数十毫安。

停止模式(Stop Mode):多数外设关闭,仅保留RTC和看门狗;功耗可降至数十微安。

待机模式(Standby Mode):仅保留少量SRAM,几乎所有外设关闭,功耗降至微安级,用于超低功耗遥测、采集等场景。

在PCB设计中需保持稳压电源的稳定,推荐在VDD与VSS之间放置足够的去耦电容(0.1μF陶瓷电容与10μF钽电容组合),同时对高速信号线进行串噪电阻和差分对匹配布局,以减少EMI干扰。

五、存储体系

STM32F407VET6内部集成了多种存储资源,包括闪存(Flash)、SRAM、数据缓存、指令缓存以及外部存储接口:

片上闪存(Flash)

STM32F407VET6片上闪存容量为512KB或1MB(具体型号有所差异,VET6一般为512KB),用于存储程序代码和常量数据。闪存可分为若干扇区(Sector),最小扇区大小为16KB或64KB,支持按扇区擦写和编程,方便在运行时进行固件升级。闪存编程操作需在特定时钟下进行,且在编程或擦除期间需禁止读取闪存,否则可能发生总线冲突。开发者在设计时需注意代码区与数据区的分布,以及启动加载程序(Bootloader)与应用固件的分区管理。片上SRAM

STM32F407VET6内置192KB的SRAM,分为多个区块:112KB位于主SRAM区域,用于程序运行时堆栈、全局或静态变量存储。

64KB位于DTCM(Data Tightly Coupled Memory)区域,为高速访问区,无等待周期,可为DMA与CPU提供更高效的数据访问。适合放置实时算法使用的数据缓冲区。

16KB位于SRAM2区域,用于备份寄存器及运行时数据,可与RTC备份域共享,断电时需VBAT供电保留内容。

缓存与总线架构

Cortex-M4核外设有指令缓存(I-Cache)和数据缓存(D-Cache),其中指令缓存4路、8路组相联,减少闪存取指等待周期;数据缓存4路、2路组相联,提高数据访问效率。内部总线分为AXI总线、AHB和APB多层结构,DMA、以太网、SDIO等外设可通过AXI总线直接访问SDRAM或SRAM,降低总线争用。外部存储接口

STM32F407VET6支持外部存储扩展,可通过FSMC(灵活静态内存控制器)接口连接SRAM、PSRAM、NOR Flash、NAND Flash等,也可通过SDIO接口连接SD卡、MMC卡、WiFi模块等存储或通信设备。为满足大容量数据存储及数据流实时传输需求,外部SDRAM接口可配合FSMC实现最高32MB外部SDRAM映射,适合图形处理、视频采集等应用场合。

六、丰富的外设模块

STM32F407VET6外设资源异常丰富,涵盖定时器、通信接口、AD/DA转换、模拟功能、安全加速、智能外设等多种功能模块。以下从主要外设分类进行详细说明:

定时器与PWM模块

高级定时器(TIM1、TIM8):具备组合PWM输出、死区时间插入、刹车功能以及多通道互锁等高级特性,适用于电机驱动、逆变器、DC-DC变换器等复杂控制场景。每路高级定时器支持4路比较通道输出,最多提供6个互补输出,可配置死区、刹车输入、外部触发等功能。

通用定时器(TIM2、TIM3、TIM4、TIM5):32位(TIM2、TIM5)或16位(TIM3、TIM4)定时器,支持输入捕获、输出比较、PWM、单脉冲模式(One-pulse)、编码器接口(Encoder Mode),可用于测量信号周期、脉宽、频率,或生成精确PWM。32位定时器可实现更大范围计数,适合长时间事件计时。

基本定时器(TIM6、TIM7):16位定时器,仅支持基础定时功能,可充当DAC或ADC触发定时,或作为定时中断源,应用于定时唤醒、心跳计时、操作系统节拍等场景。

通信接口

USART/UART:6路通用异步收发器(USART1、USART2、USART3、UART4、UART5、USART6),支持同步、单线半双工、LIN、IrDA、RS485等模式。其中USART1、USART2位于APB2总线上,传输速率最高可达4.5Mbps;其他位于APB1总线上,最高传输速率为(42MHz时钟)/16。支持硬件流控制(CTS/RTS)、FIFO缓冲,可实现稳定高速数据通信。

SPI/I2S:3路SPI(SPI1、SPI2、SPI3)支持主从模式、全双工、半双工、三线模式。通过复用复数引脚可配置为I2S音频协议接口,用于数字音频传输,支持主从时钟、标准、左对齐、PCM等模式,配合PLLI2S可产生准确音频时钟,满足音频流处理需求。

I2C:3路I2C接口(I2C1、I2C2、I2C3),支持标准模式(100kHz)、快速模式(400kHz)、快速模式+(1MHz),带有10位/7位地址,可实现多主、多从通信。硬件支持PEC校验与DMA传输,可用于连接传感器、EEPROM、RTC等外设。

CAN:2路CAN接口(CAN1、CAN2),符合CAN 2.0B协议,支持双缓冲接收、FIFO、硬件滤波,可实现车载网络、工业总线、自动化控制领域的实时数据传输。CAN2的CAN_RX引脚与CAN1的RX引脚共用,但各自有独立的滤波器,提高灵活性。

USB OTG FS/HS:集成USB On-The-Go控制器,可工作于主机(Host)或设备(Device)模式。USB FS(全速,12Mbps)模块内置PHY;USB HS(高速,480Mbps)需外接ULPI PHY。USB OTG支持电缆检测、VBUS监测、ID检测,实现OTG设备的自动角色切换。

以太网MAC:集成10/100M以太网MAC,支持RMII接口,可通过外部PHY芯片(如DP83848)实现高速网络连接。MAC模块支持IEEE 1588硬件时间戳、流量控制、断言功能,可满足工业以太网、物联网边缘设备对网络通信的高实时性和高带宽需求。

SDIO:SDIO接口支持SD、SDIO、MMC协议,最高传输速率可达48MHz,支持4位总线模式,适合SD卡文件系统扩展、无线模块通信、SPI总线替代方案等。

模数转换与数模转换

ADC:2路12位ADC(ADC1、ADC2),每个ADC拥有3个同步并行采样组,支持高达2.4MSPS采样速率,通道数达16个外部通道,内置温度传感器、VREFINT和VBAT测量通道。ADC支持DMA双缓冲、模拟看门狗、注入模式等功能,可用于高速传感器数据采集与处理。

DAC:2路12位数模转换器,每个DAC拥有独立输出缓冲,可通过DMA自动更新转换值。DAC支持双三角波、双噪声波发生器,可在音频合成、波形产生、控制信号等场景下使用。

安全与加密模块

硬件加密单元(CRYP):支持AES、DES、Triple DES、MD5、SHA-1、SHA-2等加密算法,具有硬件加速功能,能显著提高数据加密解密速度,减少CPU占用。该模块常用于安全通信协议、固件加密、数字签名等场景。

真随机数发生器(RNG):基于模糊组件的硬件随机数生成器,可提供高质量的随机数,满足密码学算法与安全协议的要求。RNG输出符合FIPS 140-2标准,适合密钥生成、掩码生成等应用。

其他外设模块

硬件定点运算单元(FPU):Cortex-M4核内置的单精度浮点运算单元可加速浮点运算,减少软件模拟浮点运算的时间,提高算法执行效率,特别适合数字信号处理(DSP)以及复杂控制算法。

Chrom-ART Accelerator(2D图形加速器):用于图形坐标转换和像素填充加速,提高GUI渲染和显示性能,尤其在采用TFT LCD屏幕时可显著减少CPU负担。

数模混合接口(FSMC):灵活静态存储器控制器可通过并行总线连接外部SRAM、PSRAM、NOR/NAND Flash、LCD控制器等,实现低成本大容量存储扩展和外设访问。

备份域(Backup Domain):包含备份寄存器、RTC、LSE时钟,可在掉电时通过VBAT口供电保持数据,适合断电存储关键数据和实时时钟计时。

看门狗定时器(WWDG/IWDG):独立看门狗和窗口看门狗模块可用于系统故障检测与安全复位。IWDG基于内部LSI振荡器,确保在系统崩溃或时钟异常时可强制系统复位;WWDG基于APB1时钟,可在特定窗口期内刷新,否则触发系统复位。

七、开发环境与工具链

进行STM32F407VET6应用开发,需要搭建完善的软硬件环境,包括开发板、调试器、IDE、库文件和例程。以下几部分是常见的开发环境组成:

硬件开发板与调试器

STM32F407VET6最小系统板:包含基本电源、时钟电路、串口转USB、ST-LINK/V2调试接口、外部存储扩展座(SD卡)等,方便快速上手。

ST-LINK/V2或ST-LINK/V3调试器:ST官方调试器,通过SWD或JTAG接口与目标板连接,支持在线下载、单步调试、寄存器查看、内存读写等功能。

J-Link系列调试器:Segger J-Link提供更高调试速度和更丰富的调试功能,可选配RTT调试打印、闪存编程加速等。

集成开发环境(IDE)与编译工具链

STM32CubeIDE:基于Eclipse和GCC的免费IDE,集成STM32CubeMX图形化配置工具,可通过鼠标配置外设时钟、引脚复用、生成HAL库初始化代码,极大降低外设配置难度。CubeIDE自带GCC编译器、GDB调试器、STM32CubeProgrammer下载工具。

Keil μVision:ARM公司的商业IDE,集成Keil MDK-ARM工具链,提供强大的仿真与调试功能、RTX实时操作系统示例,可结合CMSIS包快速开发。需要商业授权或使用有限功能版本。

IAR Embedded Workbench:IAR公司的商业IDE,具有优秀的代码优化和调试功能,可生成高效代码,适用于对代码尺寸和性能要求极高的项目。

GCC + Makefile:对于习惯命令行编译或持续集成需求的开发者,可使用GNU Arm Embedded Toolchain和Makefile进行编译,配合OpenOCD或ST-LINK工具进行下载与调试,实现开源免费开发环境。

固件库与中间件

STM32CubeF4 HAL库:ST官方提供的硬件抽象层(HAL)库,封装了对底层寄存器的操作,开发者可通过高级API来快速驱动外设。配合CubeMX可自动生成初始化代码,缩短开发周期。

LL(Low-Layer)库:相对于HAL库,LL库接口更底层、更接近寄存器,具有更高的执行效率,适合对性能要求较高的场景。CubeMX也可自动生成LL驱动代码。

CMSIS(Cortex Microcontroller Software Interface Standard):由ARM定义的底层库和RTOS接口标准,包括CMSIS-CORE、CMSIS-DSP、CMSIS-RTOS等,为编写可移植的ARM Cortex-M代码提供基础。

FreeRTOS:开源实时操作系统,可在STM32F407平台上运行,支持多线程、信号量、消息队列、事件组等功能,适用于复杂实时多任务应用。

LwIP、FatFS、USB Host/Device中间件:LwIP实现轻量级TCP/IP协议栈,支持以太网通信;FatFS提供FAT文件系统接口,可用于SD卡或USB存储;USB中间件支持USB设备类(MSC、CDC、HID等)和Host栈(Host MSC、Host HID等),丰富了应用场景。

八、工程设计要点与实践经验

在STM32F407VET6项目开发过程中,需要关注时钟配置、外设初始化、功耗管理、中断优先级、内存分配、优化与调试等关键环节。以下结合实践经验进行一些要点说明:

时钟配置与功耗优化

使用CubeMX进行时钟树配置:CubeMX可直观显示PLL参数、各个外设时钟分频器设置、总线上限频率,帮助避免配置错误。

选择合适的系统时钟:如果应用对性能要求不高,可适当降低系统频率(如120MHz、84MHz)以减少功耗;如果需要USB、SDIO等外设,需保证对应时钟频率(USB需48MHz,SDIO需48MHz)。

启用睡眠、停止、待机模式:根据实际应用场景,在空闲阶段合理使用睡眠模式或停止模式,通过设置SLEEPDEEP位、关闭无关外设时钟以降低功耗。

优化IO电平与上拉下拉:未使用的IO应配置为模拟输入模式,关闭数字输入缓冲及上拉/下拉电阻,以减少漏电流;必要时可在PCB上加入拉高/拉低电阻。

外设初始化与中断设计

优先级配置与嵌套中断:STM32F407使用NVIC进行中断优先级管理,共有4位抢占优先级和0位子优先级。优先级越小表示优先级越高,需合理分配外设中断优先级,避免出现优先级反转或死锁。对实时要求较高的外设(如紧急安全中断、CAN收发中断)应设置更高(数值更小)优先级。

DMA与中断结合:对于数据量较大的外设(如ADC、I2S、USART DMA),可开启DMA传输,减少CPU干扰并加快数据传输速率;在DMA传输完成后,由DMA中断通知上层应用处理数据。需要注意DMAMUX通道配置与缓存一致性管理。

外设复用冲突解决:由于多引脚存在复用同一功能的情况,在CubeMX选错时容易导致引脚冲突。解决办法是在配置时查看引脚详细复用表,确保同一引脚组只被一个外设占用,或通过改用其他引脚组来解决冲突。

内存分配与堆栈管理

Heap与Stack大小配置:默认在链接脚本中为堆和栈分配了固定大小,例如8KB堆、4KB栈。项目中若使用大量动态分配或深度递归,需要根据实际情况调整Heap与Stack大小,避免出现堆栈溢出。可在链接脚本(.ld文件)或CubeIDE的Project Settings中手动修改。

DTCM与SDRAM使用:将对性能要求较高或频繁访问的数组、缓冲区放置在DTCM区域以提高访问速度;若程序需要处理大容量图像数据或外部存储数据,可通过FSMC将SDRAM映射到地址空间,将大块数据存储在外部SDRAM中。

缓存一致性管理:开启数据缓存后,DMA对外设读写时需先清除(invalidate)Cache或刷新(clean)Cache,否则可能出现数据不同步。建议根据DMA使用场景,手动调用SCB_InvalidateDCache()或SCB_CleanDCache()函数保证缓存与内存一致性。

代码优化与调试技巧

启用编译优化:在Release模式下启用-O2或-O3优化,配合函数内联(inline)和代码裁剪(Garbage Collection of unused sections)可显著减少代码体积并提高性能。

利用ST-Link Real-Time Transfer(RTT)调试:RTT技术可在不打断CPU的情况下实时输出调试信息,适合程序调试与性能分析。需在项目中加入SEGGER_RTT.c/h相关文件,配置SWO口和调试工具。

使用逻辑分析仪和示波器:对时序敏感的外设(如I2C、SPI时序、PWM波形),可通过示波器或逻辑分析仪进行波形捕获与分析,确认通信协议和信号完整性。

堆栈溢出检测:在启动代码里可将初始SP下方添加特定填充模式(如0xDEADBEEF),运行后检查边界区域是否被覆盖,及时发现堆栈溢出问题。

九、典型应用案例

为了更好地理解STM32F407VET6在实际工程中的应用,以下结合几个典型案例进行分析,展示其在工业控制、图像处理、通信网关、音视频处理等领域的应用价值和实现要点。

工业自动化运动控制系统

应用背景与需求:在工业自动化场合(如数控机床、机器人臂、AGV小车),对电机驱动控制的实时性、精度和可靠性有较高要求。需要对电机位置、速度进行闭环控制,并实时处理编码器信号与PWM输出。

硬件方案:采用STM32F407VET6作为主控芯片,搭配三相伺服驱动器、增量式光电编码器、三相电源模块、霍尔传感器或直流电机传感器。STM32的TIM1和TIM8高级定时器用于产生三相电机驱动的互补PWM波,支持死区控制和紧急刹车。编码器信号通过定时器的插入模式或编码器接口模式进行高速捕获,获得实时转速和位置信息。

软件实现要点:

定时器配置:TIM1/TIM8配置为中心对齐模式(Center-aligned Mode)、死区时间设定(根据MOSFET驱动需求,一般20~200ns),刹车引脚配置用于外部过流或过压保护。

编码器接口:TIM2或TIM3配置为编码器接口模式(Encoder Mode),将A、B相脉冲接入计数器,实现实时位置角度测量。对编码器计数器溢出或计数方向进行判断,以获得精确转速。

PI/PID控制算法:在DMA模式下使用ADC采集电机驱动电流与电压,通过硬件滤波器或数字滤波后传送至DTCM,采用浮点运算单元(FPU)进行PID算法计算,输出控制量给TIMx的比较寄存器,实现无刷直流电机或伺服电机控制。

看门狗与安全保护:使用IWDG配置合适的喂狗周期(例如50ms),避免系统死锁时失控;在过流、过压事件发生时通过定时器刹车或外部中断触发紧急关断保护电路。

工业以太网通信网关

应用背景与需求:在工业现场中,各类设备往往采用Modbus、CANOpen、PROFINET等不同协议,需要一个网关将现场总线数据转换为以太网格式,实现集中监控与远程管理。对实时性和吞吐量都有较高要求,同时要求通讯加密与鉴权。

硬件方案:STM32F407VET6利用其内置以太网MAC连接外部RMIIPHY芯片(如LAN8742),实现10/100Mbps以太网连接;CAN接口用于连接CANOpen设备;串口或RS485接口用于Modbus RTU/ASCII通信;SDIO接口或SPI接口用于扩展存储或WiFi模块。

软件实现要点:

以太网MAC与PHY驱动:采用HAL库或LWIP集成的以太网驱动初始化函数,配置MAC地址、PHY地址、RCC时钟以及GPIO引脚复用,使用缓存描述符(DMA Descriptor)模式实现数据包收发。

LWIP协议栈移植与配置:在FreeRTOS下创建以太网收发任务,初始化LWIP堆栈,启用DHCP或使用静态IP地址,配置TCP、UDP连接,完成Modbus TCP、Socket通信等应用。

多协议处理与消息转发:建立CAN接收中断,在中断中接收CAN报文并存入队列;Modbus RTU通过USART-DMA模式接收解析报文;在以太网通信任务中解析TCP/UDP报文,根据协议转换规则将数据转发至CAN总线或Modbus总线上。必须注意多任务并发访问共享资源时的互斥与同步机制,可使用信号量或互斥锁进行保护。

安全加密与认证:在以太网层面可使用TLS/SSL,调用硬件CRYP加速模块进行AES加解密,减少CPU占用;对于固件的安全性,采用Bootloader与加密签名机制,在启动时验证固件完整性,防止恶意篡改。

TFT显示与触摸界面

应用背景与需求:在医疗仪器、工控设备、智能家居等领域,需要直观的图形用户界面(GUI)进行人机交互,需要实时刷新屏幕并处理触摸输入。STM32F407VET6的Chrom-ART加速器和FSMC接口可与TFT LCD屏和触摸屏控制器结合,实现流畅的图形显示。

硬件方案:使用2.8寸或4.3寸TFT LCD(分辨率如320×240或480×272),通过FSMC并行总线连接LCD控制器(如ILI9341、RM68120等),触摸板(如电阻式或电容式)通过SPI或I2C接口连接控制器;外部SDRAM用于存储图像缓冲区。

软件实现要点:

FSMC与LCD接口:配置FSMC为16位/8位异步模式,设置读写时序寄存器以满足LCD控制器的时序要求;将LCD数据/命令引脚映射到FSMC地址线,通过FSMC_A0区分数据和命令,驱动函数中通过FSMC写寄存器与写数据实现TFT刷新。

图形库与加速器使用:可采用ST官方的TouchGFX或第三方图形库(如uGFX、emWin)进行上层GUI设计;在底层驱动函数中使用Chrom-ART Accelerator进行图形转换(如竖屏数据流转换、RGB565与RGB888格式转换),提高擦屏、图标绘制速度。

触摸屏驱动与中断:电阻式触摸板通过ADC采样X和Y坐标,或通过触摸控制芯片(如XPT2046)以SPI方式获取触摸点;电容式触摸板通过I2C总线读取坐标并通过中断触发按下事件;触摸中断优先级要高于普通应用任务,保证灵敏度。

双缓冲与帧率控制:在SDRAM中分配双缓冲区域,一个缓冲用于当前显示,一个缓冲用于后台绘制。绘制完成后通过DMA2D(Chrom-ART)将后台缓冲区拷贝到LCD显示缓冲区,减少撕裂现象并提升刷新效率。

音频处理与数字信号处理(DSP)

应用背景与需求:在嵌入式音频设备(如数字混音台、智能音箱、噪声消除耳机)中,需要对PCM音频数据进行采样、滤波、FFT分析、数字调制等处理,要求浮点运算单元提供高效计算。

硬件方案:STM32F407VET6通过I2S总线连接音频CODEC(如WM8731、TLV320AIC23B等),支持I2S全双工通信;内部使用PLLI2S模块产生44.1kHz、48kHz或96kHz音频时钟;外部SDRAM可作为缓冲区用于缓存音频数据。

软件实现要点:

I2S与DMA配置:I2S配置为主模式,使用DMA双缓冲模式接收和发送音频PCM数据,通过回调函数实现连续数据流传输。I2S时钟来源于PLLI2S配置(例如,PLLI2S输入8MHz HSE,配置参数后可得到I2S时钟44.1kHz或48kHz),确保音频采样精度。

CMSIS-DSP库调用:在音频回调中调用CMSIS-DSP库函数进行FFT变换、FIR滤波或IIR滤波,实现噪声滤除、回声消除、音效调整等功能。CMSIS-DSP利用FPU加速浮点运算,大幅度提高算法执行效率。

音频数据格式与缓存管理:采用16位或24位PCM格式,根据DAC或DAC缓冲区所需格式调整;使用环形缓存(Circular Buffer)管理I2S数据收发,避免缓存溢出或数据卡顿。需要在初始化时配置DMA缓存大小和优先级,确保音频流畅性。

用户界面与音频输出:若设备具备LCD显示,可将音频频谱通过图形界面显示;音量调节、均衡器参数可通过触摸屏或旋钮进行实时调整,通过I2C或GPIO读取输入并更新DSP参数。音频输出通过DAC或I2S输出到外部放大器及扬声器,需关注模拟地与数字地分离以降低噪声。

十、常用外设选型与PCB设计要点

在硬件设计过程中,合理选择外设芯片与布局布线对于STM32F407VET6系统的稳定性和性能至关重要。以下从电源、晶振、外部存储、EMI与信号完整性等方面做简要指导:

电源与电平转换

稳压器选型:STM32F407VET6典型工作电压为3.3V,可选用TI、Analog Devices或国产稳压芯片(如AMS1117-3.3、MCP1700-3.3)提供稳定电源。为减少噪声干扰,可在稳压器后面串联电感与RC滤波网络。

电源滤波与去耦:在VDD与VSS之间沿每组电源引脚放置0.1μF陶瓷旁路电容,靠近芯片引脚;同时在主电源入口处放置10μF至22μF的钽电容,以抑制突发大电流;对于USB或以太网供电,还需额外的共模电感和EMI滤波电路。

电平转换与隔离:当需要与5V或12V设备通信时,可选用电平转换芯片(如TXS0108E、74HC4050)或光耦隔离(如光电耦合器HCPL-A310)进行电平或信号隔离,保护STM32 IO不受高电压冲击。

晶振与时钟电路

HSE晶振电路设计:若使用7~25MHz的石英晶体,需要匹配适当的负载电容(一般为5~15pF),并保证晶振脚之间走线尽量短,远离数字信号线与开关节点,以减少干扰。若对时钟精度要求不高,也可采用MEMS振荡器(如SiT5351)替代石英晶体,减少板级调试时间。

LSE晶振电路设计:32.768kHz晶体需要大约6~12pF的负载电容,该电容值由晶体手册中推荐值决定。晶体与芯片引脚之间宜布置地平面隔离带,禁止其他信号线穿过,以免降低时钟精度。

外部存储与扩展

SDRAM布局:若系统需要大容量外部SDRAM(如32MB或64MB),选用SDRAM芯片(如IS42S16800J)并通过FSMC接口连接。SDRAM地址线与数据线需要与FSMC地址、数据引脚1:1对应,且走线长度差控制在200 mils以内,终端匹配电阻需靠近芯片端进行阻抗匹配,确保信号完整性。

NAND/NOR Flash扩展:若需要外挂更多代码或数据存储,可通过FSMC连接NAND或NOR Flash。NAND Flash的布局需注意数据线和控制信号(CLE、ALE、WE、RE)匹配时序,可采用隔离电阻和IO缓冲器以减少负载。

SD卡与USB存储:通过SDIO接口与SD卡通信时,必须保证SDIO信号线(CMD、CLK、DAT0-3)的走线长度一致,并添加上拉/下拉电阻;USB接口需要4.7Ω、22Ω的差分信号串阻,且Vbus线需在外部放置稳压二极管进行过压保护。

EMI与信号完整性

信号线走线规则:高速信号(如USB、以太网、SDIO、FSMC信号等)必须采用差分阻抗控制,并保证走线长度匹配,否则可能产生串扰和信号反射。使用四层PCB时,将电源层和地层置于核心层,中间信号层叠加参考层,可减少EMI。

地平面与电源平面:宜使用完整的地平面减小环路面积,避免地弹回效应(Ground Bounce);关键模拟信号与数字信号地分开布线,并在芯片下方预留一个固定的地平面,不要分割。

EMI滤波与屏蔽:对于以太网PHY、USB接口和外部时钟源周围,可放置共模电感和EMI滤波器;若应用对干扰要求严格,需要在PCB关键区域采用屏蔽罩(金属罩壳)或导电胶带进行局部屏蔽。

十一、生态与软件资源

STM32F407VET6凭借其强大的功能和广泛的外设支持,拥有成熟的生态系统和丰富的软件资源,以下为常见开发资源及社区支持:

STM32CubeMX与CubeIDE:STM32CubeMX可基于GUI方式进行外设、时钟、引脚配置,并生成初始化C代码;STM32CubeIDE则将CubeMX、Eclipse IDE与GCC工具链集成,为开发者提供一站式集成开发环境。

HAL库示例与应用笔记:ST官方提供大量针对STM32F4系列的示例工程,包括GPIO、ADC、USART、CAN、USB、以太网、SDRAM、DMA2D等模块的使用示例;同时发布了PMC(Power Management Controller)、Timing、Graphics、Audio等应用笔记,为开发者提供参考。

第三方中间件与社区支持:如FreeRTOS、uC/OS、LWIP、FatFS、TouchGFX、EmFile、emWin等,可满足实时操作系统、网络、文件系统、图形UI等多种需求;Github、CSDN、STM32官方论坛等社区也活跃着大量STM32爱好者分享心得、经验与项目。

调试与分析工具:ST-LINK Utility用于在线烧写和调试;Keil、IAR提供性能分析与代码覆盖率工具;Segger提供SystemView进行实时系统调用跟踪与诊断;此外还有Trace32、Ozone等第三方专业分析工具。

十二、总结与展望

STM32F407VET6凭借ARM Cortex-M4内核的高性能和浮点运算能力、丰富的片上外设资源以及成熟的生态支持,成为嵌入式领域中功能强大且应用广泛的微控制器。通过合理配置时钟系统与外设资源,结合DMA、FPU、Chrom-ART加速器等硬件加速模块,可以实现高效实时控制、复杂图形显示、高带宽通信、音视频处理、信号采集与处理等多种功能。其多种功耗模式也为便携式、无线传感器节点等应用提供了低功耗方案。

在未来,随着物联网、工业互联网、智能制造等领域的快速发展,STM32F407VET6仍能依托其强大的性能和外设,对于二次开发和扩展平台保持高度适应性。例如,在边缘计算网关中负责数据预处理和协议转换,亦可在智能机器人中作为主控核心,执行高级控制算法和视觉处理。结合云端通信与大数据分析,STM32F407VET6平台可进一步拓展在智能家居、智能医疗、智慧城市等领域的应用边界。

综上所述,深入掌握STM32F407VET6的架构、外设、开发要点与优化技巧,对于嵌入式工程师设计高性能、稳定可靠的系统具有重要意义。希望本文提供的全面知识与实践经验,能够帮助开发者迅速上手并开展项目设计,实现创新应用。

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)