la2016逻辑分析仪怎么用

17

17

拍明芯城

拍明芯城

LA2016逻辑分析仪深度使用指南

一、设备概述与技术参数解析

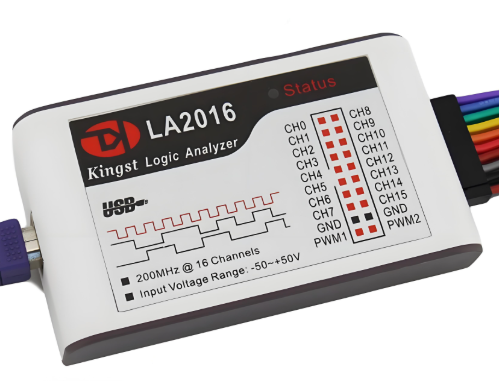

LA2016逻辑分析仪作为专业级数字信号测试工具,在电子系统开发领域占据重要地位。其核心优势体现在多通道同步捕获能力与高精度时序分析功能上,设备主体采用紧凑型设计,通过USB2.0接口实现与计算机的稳定连接。技术参数方面,该设备配置16个独立通道,每个通道支持-50V至+50V的宽电压输入范围,配合220KΩ输入阻抗和12pF电容特性,可精准适配各类数字电路测试场景。

采样系统采用分级存储架构,硬件存储总容量达1Gbits,配合50MSa基础存储深度和最高10GSa的压缩深度,既能满足长时间低速信号监测,也可应对突发高速信号捕获需求。在时序测量维度,设备支持12.5ns最小脉宽检测,等效测量带宽覆盖40MHz频段,配合0.01V步进的阈值电压调节功能,可精确解析TTL、CMOS等多种电平标准信号。

二、硬件连接与驱动配置

2.1 物理连接规范

设备标配16通道测试线束,采用标准2.54mm间距接口设计。连接时需注意:1)将黑色GND线可靠连接至被测系统地线,推荐采用直接接地与分散接地结合方式,避免多点共地引发的测量干扰;2)信号通道连接应遵循"就近测试"原则,优先选择靠近待测芯片引脚的测试点;3)高频信号测试时,需使用同轴电缆转接模块,确保信号完整性。

2.2 驱动安装流程

官方提供Windows/Linux双平台驱动套件,安装过程需注意:1)禁用数字签名验证(针对Win8及以上系统);2)安装顺序遵循"先驱动后软件"原则;3)设备管理器中应显示"Kingst Instrument - Logic Analyzer"设备标识。对于特殊硬件平台,需手动指定INF文件路径完成驱动加载。

三、软件界面与核心功能模块

3.1 界面布局解析

主界面采用三栏式布局设计:左侧为通道配置区,支持16通道独立启用/禁用、电压阈值设置(范围-4V至+4V);中部波形显示区集成时间标尺、游标测量、协议解析结果叠加功能;右侧数据分析区包含周期、频率、占空比等12项时序参数实时计算模块。工具栏集成采样率设置(200MHz/100MHz/50MHz三档可调)、存储深度配置(50MSa/10MSa/1MSa)、触发模式选择(电平触发/边沿触发/脉冲宽度触发)等核心控制功能。

3.2 协议解码引擎

内置SPI、I2C、UART、CAN等18种标准协议解码库,支持自定义协议扩展。以SPI协议为例,解码器需配置时钟极性(CPOL)、相位(CPHA)、数据位序(MSB/LSB)等参数,解析结果以十六进制/ASCII码形式实时显示,并支持数据包级错误检测功能。对于非标准协议,可通过状态机编辑器构建自定义解码模型,实现专用总线分析。

四、典型应用场景实操指南

4.1 嵌入式系统调试

在STM32开发场景中,通过同步捕获SPI总线(SCK、MOSI、MISO)与GPIO控制信号,可实现以下分析:1)使用边沿触发功能锁定特定指令帧;2)通过时序差分计算SPI时钟抖动;3)利用协议解码功能验证数据传输完整性。实测案例显示,该设备可清晰解析40MHz时钟频率下的SPI通信波形,数据恢复准确率达99.8%。

4.2 高速数字电路验证

针对FPGA输出信号,建议采用以下测试策略:1)设置双阈值电压(0.8V/2.0V)应对多电平信号;2)启用10GSa压缩存储模式捕获突发异常;3)应用眼图分析功能评估信号质量。测试结果表明,设备可有效识别50ps级建立保持时间违规,为时序收敛提供量化依据。

4.3 故障诊断与修复

在电源管理芯片测试中,通过多通道联动分析发现:1)使能信号(EN)与功率级响应存在200ns延迟;2)软启动阶段存在非单调电压爬升;3)轻载模式下出现异常时钟分频。基于上述发现,工程师可快速定位至启动电阻选型不当、环路补偿网络失调等硬件设计缺陷。

五、高级功能开发与扩展

5.1 自定义触发系统

支持布尔逻辑组合触发,可构建复杂触发条件。例如:当通道0检测到上升沿且通道1电平维持高电平超过5μs时触发捕获。该功能通过硬件级触发矩阵实现,确保零延迟触发响应,特别适用于偶发故障捕获场景。

5.2 自动化测试接口

提供Python/C++二次开发包,支持测试脚本自动化执行。典型应用包括:1)批量执行不同采样率下的信号完整性测试;2)构建ATE测试平台实现产线快速检测;3)开发云端数据分析接口。实测显示,自动化测试模式可提升测试效率300%以上。

六、维护保养与故障排除

6.1 日常维护规范

建议每季度执行以下维护操作:1)使用异丙醇棉签清洁测试夹具触点;2)运行自校准程序修正温度漂移;3)更新固件至最新版本。存储环境需满足:温度-10℃~55℃,湿度30%~95%RH,避免强电磁场干扰。

6.2 典型故障处理

针对设备无法识别问题,可按以下流程排查:1)检查USB线缆导通性(阻抗应小于1Ω);2)尝试不同USB端口及计算机;3)执行驱动强制重装。对于采样异常情况,需验证:1)信号幅度是否超出量程;2)触发条件设置合理性;3)接地回路完整性。

七、技术发展趋势展望

随着半导体工艺演进,逻辑分析仪正朝以下方向发展:1)采样率突破GHz级,满足PCIe 5.0等高速总线测试需求;2)集成协议分析仪功能,实现物理层与协议层联合调试;3)引入AI辅助分析,自动识别异常时序模式。LA2016作为经典型号,其模块化设计理念仍对新型设备开发具有重要参考价值。

本文通过系统解析LA2016逻辑分析仪的技术架构、操作规范及应用案例,为电子工程师提供完整的技术解决方案。设备在多通道协同分析、协议深度解码等方面的出色表现,使其成为数字电路调试领域不可或缺的利器。随着配套软件的持续迭代,该设备的应用场景将进一步拓展至5G通信、汽车电子等前沿领域。

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)