74ls283引脚图

80

80

拍明芯城

拍明芯城

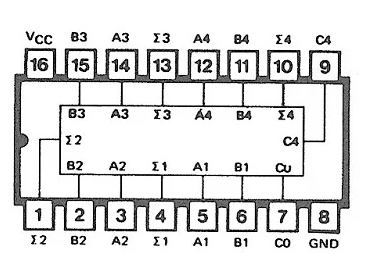

74LS283是一款4位二进制超前进位全加器芯片,其引脚图通常包含以下引脚:

Vcc:芯片的电源正极输入,典型值为5V。

GND:芯片的低电平输入,即电源的负极。

A1~A4:A端运算的输入端,用于接收第一个4位二进制数的各位。

B1~B4:B端运算的输入端,用于接收第二个4位二进制数的各位。

Σ1~Σ4(或S1~S4,根据具体文档可能有所不同):运算和的输出端,分别对应A端和B端输入相加后的4位结果。

C0:进位输入端,用于接收来自前一位的进位信号(在多位数相加时)。

C4:进位输出端,用于输出当前4位相加后产生的进位信号到下一位。

以下是74LS283引脚图的简要描述(由于我无法直接绘制图形,以下用文字描述):

引脚图通常呈矩形,左侧和上方为输入引脚,右侧和下方为输出引脚(但具体布局可能因封装形式而异)。

Vcc引脚通常位于左上角或右上角,GND引脚则位于左下角或右下角。

A1A4和B1B4引脚分别排列在Vcc和GND引脚的两侧,形成两个4位的输入端口。

Σ1Σ4(或S1S4)引脚则排列在A1A4和B1B4引脚的对面,形成4位的输出端口。

C0引脚通常位于A1或B1引脚的旁边,用于接收进位输入。

C4引脚则位于Σ4(或S4)引脚的旁边或下方,用于输出进位信号。

具体的引脚布局和编号可能因不同的封装形式(如双列直插封装DIP或小外形模压封装SOP)而有所差异。因此,在实际应用中,建议参考具体的74LS283芯片数据手册或引脚图来确定引脚的具体位置和编号。

74LS283芯片具有高速、低功耗和稳定性好的特点,被广泛应用于计算机系统、逻辑电路设计以及算术运算等领域。其超前进位加法器设计使得每一位的进位直接由加数和被加数相加产生,无需等待低位的进位信号,从而提高了运算速度。

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)