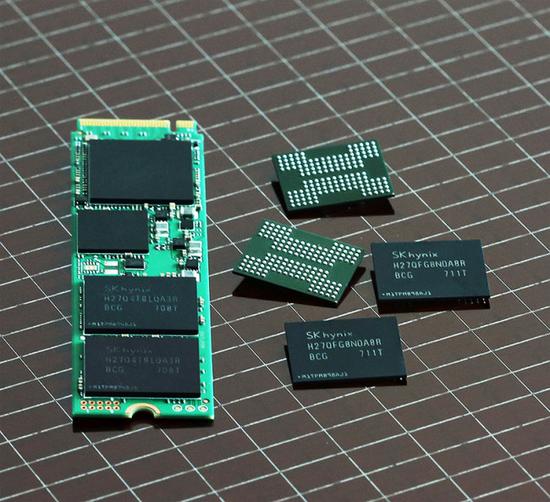

苹果供应商海力士发布72层256G 3D闪存芯片可以提供32GB闪存

296

296

拍明

拍明

苹果供应商海力士(SK Hynix)今天发布了72层,256Gb 3D NAND 闪存芯片。这种芯片比 48层技术多1.5倍,单个 256Gb NAND 闪存芯片可以提供 32GB 闪存,这种芯片比 48 层 3D NAND 芯片的内部运行速度快两倍,读写性能快 20%。

海力士自从2016年11月开始生产 48 层 256Gb 3D NAND 芯片。之前的 36 层 128Gb 3D NAND 芯片在2016年4月开始生产。因为层数更多,利用现有的生产线,产能可以提升 30%。海力士将在今年下半年开始量产。

iPhone 7 和 iPhone 7 Plus 配备的 NAND 闪存供应商来自东芝和海力士。一些 iPhone 7 采用东芝 48 层 3D BiCS NAND 芯片,这种芯片之前从未出现在其他商业产品中。其他 iPhone 7 型号采用海力士闪存芯片。

32GB iPhone 7 比 128 GB 型号更慢,前者的数据读取速度为 656 Mbps,后者为 856Mbps。东芝和海力士的内存芯片采用 15纳米工艺打造

海力士

Hynix 海力士芯片生产商,源于韩国品牌英文缩写"HY"。海力士即原现代内存,2001年更名为海力士。海力士半导体是世界第三大DRAM制造商,也在整个半导体公司中占第九位。

海力士市场概况

市场地位

在韩国有4条8英寸晶圆生产线和一条12英寸生产线,在美国俄勒冈州有一条8英寸生产线。2004年及2005年全球DRAM市场占有率处于第二位,中国市场占有率处于第一位。在世界各地有销售法人和办事处,共有员工15000人.海力士(Hynix)半导体作为无形的基础设施,通过半导体,竭尽全力为客户创造舒适的生活环境。海力士半导体致力生产以DRAM和NAND Flash为主的半导体产品。

市场前景

海力士半导体以超卓的技术和持续不断的研究投资为基础,每年都在开辟已步入纳米级超微细技术领域的半导体技术的崭新领域。另外,海力士半导体不仅标榜行业最高水平的投资效率,2006年更创下半导体行业世界第七位,步入纯利润2万亿韩元的集团等,正在展现意义非凡的增长势力。海力士半导体不仅作为给国家经济注入新鲜血液的发展动力,完成其使命,同时不断追求与社会共同发展的相生经营。海力士半导体为发展成为令顾客和股东满意的先导企业,将尽心尽责,全力以赴。

闪存芯片分类

闪存也有不同类型,其中主要分为NOR型和NAND型两大类。

NOR型与NAND型闪存的区别很大,打个比方说,NOR型闪存更像内存,有独立的地址线和数据线,但价格比较贵,容量比较小;而NAND型更像硬盘,地址线和数据线是共用的I/O线,类似硬盘的所有信息都通过一条硬盘线传送一般,而且NAND型与NOR型闪存相比,成本要低一些,而容量大得多。因此,NOR型闪存比较适合频繁随机读写的场合,通常用于存储程序代码并直接在闪存内运行,手机就是使用NOR型闪存的大户,所以手机的“内存”容量通常不大;NAND型闪存主要用来存储资料,我们常用的闪存产品,如闪存盘、数码存储卡都是用NAND型闪存。

速度

这里我们还需要端正一个概念,那就是闪存的速度其实很有限,它本身操作速度、频率就比内存低得多,而且NAND型闪存类似硬盘的操作方式效率也比内存的直接访问方式慢得多。因此,不要以为闪存盘的性能瓶颈是在接口,甚至想当然地认为闪存盘采用USB2.0接口之后会获得巨大的性能提升。

前面提到NAND型闪存的操作方式效率低,这和它的架构设计和接口设计有关,它操作起来确实挺像硬盘(其实NAND型闪存在设计之初确实考虑了与硬盘的兼容性),它的性能特点也很像硬盘:小数据块操作速度很慢,而大数据块速度就很快,这种差异远比其他存储介质大的多。这种性能特点非常值得我们留意。

NAND型

内存和NOR型闪存的基本存储单元是bit,用户可以随机访问任何一个bit的信息。而NAND型闪存的基本存储单元是页(Page)(可以看到,NAND型闪存的页就类似硬盘的扇区,硬盘的一个扇区也为512字节)。每一页的有效容量是512字节的倍数。所谓的有效容量是指用于数据存储的部分,实际上还要加上16字节的校验信息,因此我们可以在闪存厂商的技术资料当中看到“(512+16)Byte”的表示方式。2Gb以下容量的NAND型闪存绝大多数是(512+16)字节的页面容量,2Gb以上容量的NAND型闪存则将页容量扩大到(2048+64)字节。

擦除操作

NAND型闪存以块为单位进行擦除操作。闪存的写入操作必须在空白区域进行,如果目标区域已经有数据,必须先擦除后写入,因此擦除操作是闪存的基本操作。一般每个块包含32个512字节的页,容量16KB;而大容量闪存采用2KB页时,则每个块包含64个页,容量128KB。

每颗NAND型闪存的I/O接口一般是8条,每条数据线每次传输(512+16)bit信息,8条就是(512+16)×8bit,也就是前面说的512字节。但较大容量的NAND型闪存也越来越多地采用16条I/O线的设计,如三星编号K9K1G16U0A的芯片就是64M×16bit的NAND型闪存,容量1Gb,基本数据单位是(256+8)×16bit,还是512字节。

寻址

寻址时,NAND型闪存通过8条I/O接口数据线传输地址信息包,每包传送8位地址信息。由于闪存芯片容量比较大,一组8位地址只够寻址256个页,显然是不够的,因此通常一次地址传送需要分若干组,占用若干个时钟周期。NAND的地址信息包括列地址(页面中的起始操作地址)、块地址和相应的页面地址,传送时分别分组,至少需要三次,占用三个周期。随着容量的增大,地址信息会更多,需要占用更多的时钟周期传输,因此NAND型闪存的一个重要特点就是容量越大,寻址时间越长。而且,由于传送地址周期比其他存储介质长,因此NAND型闪存比其他存储介质更不适合大量的小容量读写请求。

【相关信息】3D闪存芯片

3D内存芯片(Hybrid Memory Cube(HMC)),又名混合立方内存芯片,由美光公司提出,这种混合立体内存与CPU的数据传输速度将是现阶段内存技术的10倍以上,以便适应高速发展的处理器和宽带网络。

研发

在2011年6月,三星和美光牵头,联合了Altera、OpenSilicon、Xilinx等,成立了HybridMemoryCubeConsofrtin(混合立方内存芯片联盟)。旨在通过多方的合作,将新的内存技术混合立方内存芯片推向市场。

随后,IBM、Microsoft、惠普、ARM、海力士相继加入 75名预期将成为联盟应用者的成员。HMCC现已对超过90家表示兴趣的潜在应用者成员进行了答复。

HMCC开发团队计划向越来越多加入该联盟的“应用者”提交一份接口规范草案。随后,融合了开发者和应用者的团队将推敲该草案并在2012年底发布该接口规范的定稿。

效能

由于在存储芯片堆叠时使用了IBM的TSV(through-siliconvia;过孔硅) 技术,相同面积的芯片将获得10倍于传统芯片的存储容量。与此同时,由于采用了某些内建机制,传输数据消耗的能量将减少70%,传输速度也将提升到标准DDR3芯片的15倍左右。现有产品原型的带宽就已高达128GB/s,为高端DDR3闪存传输速度的10倍,最终成品还会更高。

市场

HMC的特性将为各种广泛的应用提供高性能的存储解决方案,应用范围从工业产品到高性能计算和大规模网络。根据官方解释,HMC内存最初将定位于工业企业服务器市场,但随着技术的发展和成本的降低终将进入消费级市场 。

责任编辑:Davia

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)