浅谈外部中断的使用:TMS320C6455实现外部中断

291

291

拍明

拍明

原标题:TMS320C6455外部中断实现 浅谈外部中断的使用

TMS320C6455

TMS320C6455是TI公司推出的的一款新型高性能单核定点DSP.它是TI公司基于第三代先进VeloviTI VLIW(超长指令字)结构开发出来的新产品,在通信,医疗图像,无线传输方面都可以大有作为.TMS320C6455主频达到了1GHz,1ns的指令周期.每周期执行8条32位指令,最大峰值速度达到8000MIPS.这意味着.在1G时钟频率下,8000个16位“16位的MACs能在1秒钟发生.TMS320C6455还带有Seria/RapidlOfr)总线,互连速率每秒高达25Gbits,实现了极高的多处理性能,降低了系统消耗,比此前的外部存储器接口快12倍,这使得多DSP级连变得十分方便.TMS320CC6455片内是基于C64xx内核的L1/L2存储结构.片上集成有大量的存储空间.L1P为32K字节,L1D为32K字节 L2为2M字节、比此前C64x器的存储器容量件翻一番,其中L1P和L2都可直接映射到存储空间。

TMS320C6455的外围总线包括:一个内部集成电路总线(I2C).两个多路缓冲串口总线fMcBSPs),两个64位通用定时器(可以配置成4个32位定时器),一个可配置的16位或32位主机接口(HPI6/HPI32).一个PCI总线,一个16管脚的通用输入/输出端口(GPIO),一个10/100/1000M 以太网媒体访问控制器(EMAC)。一个无缝外部存储器接口(64一bit EMIFA),一个32位DDR2 SDRAM接口。

C6455由于自带千兆EMAC,外接PHY物理层芯片即可实现一个千兆以太网口。千兆以太网的实现使得C6455嵌入式处理器与台式机等设备的数据传输变得异常方便。TI为C6455等处理器提供了NDK(Network Develop Kit),通过NDK的使用可以简化C6455中TCP/IP或者UDP等数据传输协议的实现。

外部中断

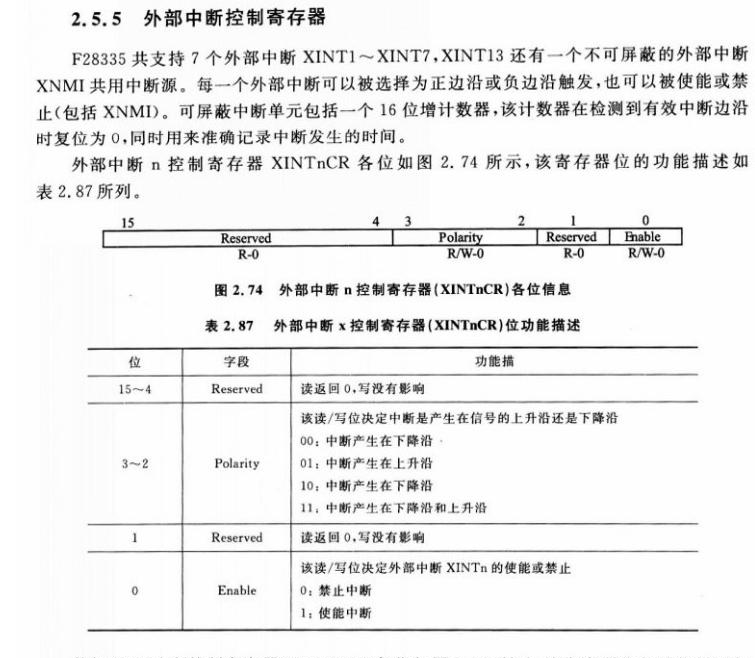

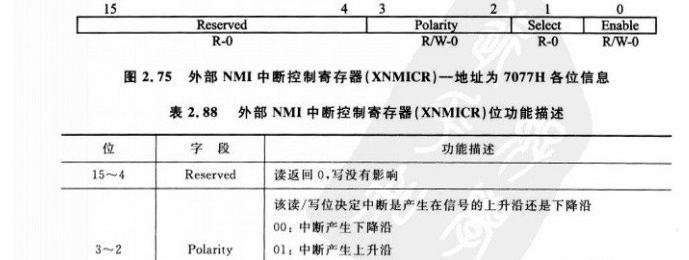

外部中断和其他模块中断中断原理一样,也是先设置中断级,然后PIE级,最后CPU级,外部中断的中断寄存器在中断头文件中,中断触发设置在中断C文件中,外部中断作为一个单独的模块使用。28335支持8 个可屏蔽的外部中断(XINT1–XINT7, XNMI)。XNMI 可设置成INT13 或者CPU 的NMI 中断。每一个中断可设置成负边沿、正边沿或者正负边沿触发,并且设置启用或禁用(包括XNMI 在内)。XINT1, XINT2,和XNMI 还包含一个16 位自由运行的递增计数器,当检测到一个有效的中断边沿时,该计数器复位为0。这个计数器可被用于中断精确计时。与281x 器件不同,28335没有专用的外部中断引脚。XINT1,XINT2 和XINT 中断可设置成GPIO0-GPIO31 引脚的输入。XINT3–XINT7 中断可设置成GPIO32-GPIO63 引脚的输入。外部中断控制寄存器的位定义如下图所示。

由上可知,配置外部中断的步骤为:

1、配置GPIO为外部中断引脚。

2、设置外部中断触发条件。

3、开启PIE中断。

4、设置中断向量表。

5、开启CPU中断。

6、编写中断函数,清除PIE中断标志位。

TMS320C6455外部中断实现

中断模块CSL库使用

上面介绍了很多,其实就是想说清楚C6455的中断机制。实际使用还是CSL比较方便。

使用CSL配置中断需要如下几个步骤:

1. 初始化中断模块

2. 使能NMI

3. 全局中断使能

4. 打开中断模块

5. 绑定中断服务程序

6. 使能相应事件

完整中断配置例子----把GPIO4事件映射到INT4

CSL_Status intStat;

CSL_IntcContext gpiocontext;

CSL_IntcEventHandlerRecord isr_gpio;

CSL_IntcEventHandlerRecord record[1];

CSL_IntcGlobalEnableState state;

CSL_IntcParam vectId;

CSL_IntcHandle gpioIntcHandle;

CSL_IntcObj gpioIntcObj;

static void HANDLE_INTR4(void *arg)

{

//中断服务程序

}

/*-----------------------------------------------------------------------------------

*

* 初始化外部中断4

*

-----------------------------------------------------------------------------------*/

void InitAndEnableIntc4(void)

{

//初始化

gpiocontext.numEvtEntries = 1;

gpiocontext.eventhandlerRecord = record;

intStat = CSL_intcInit(&gpiocontext);

//使能NMI(不可屏蔽中断)

intStat = CSL_intcGlobalNmiEnable();

//全局中断使能

intStat = CSL_intcGlobalEnable(&state);

//打开中断模块(把GPIO4中断事件映射到系统中断INT4)

vectId = CSL_INTC_VECTID_4;

gpioIntcHandle = CSL_intcOpen(&gpioIntcObj, CSL_INTC_EVENTID_GPINT4, &vectId, &intStat);

//绑定中断服务程序

isr_gpio.handler = (CSL_IntcEventHandler)&HANDLE_INTR4;

CSL_intcPlugEventHandler(gpioIntcHandle, &isr_gpio); //绑定

//使能该事件(开始监听)

CSL_intcHwControl(gpioIntcHandle, CSL_INTC_CMD_EVTENABLE, NULL);

}

CSL_Status intStat;

CSL_IntcContext gpiocontext;

CSL_IntcEventHandlerRecord isr_gpio;

CSL_IntcEventHandlerRecord record[1];

CSL_IntcGlobalEnableState state;

CSL_IntcParam vectId;

CSL_IntcHandle gpioIntcHandle;

CSL_IntcObj gpioIntcObj;

static void HANDLE_INTR4(void *arg)

{

//中断服务程序

}

/*-----------------------------------------------------------------------------------

*

* 初始化外部中断4

*

-----------------------------------------------------------------------------------*/

void InitAndEnableIntc4(void)

{

//初始化

gpiocontext.numEvtEntries = 1;

gpiocontext.eventhandlerRecord = record;

intStat = CSL_intcInit(&gpiocontext);

//使能NMI(不可屏蔽中断)

intStat = CSL_intcGlobalNmiEnable();

//全局中断使能

intStat = CSL_intcGlobalEnable(&state);

//打开中断模块(把GPIO4中断事件映射到系统中断INT4)

vectId = CSL_INTC_VECTID_4;

gpioIntcHandle = CSL_intcOpen(&gpioIntcObj, CSL_INTC_EVENTID_GPINT4, &vectId, &intStat);

//绑定中断服务程序

isr_gpio.handler = (CSL_IntcEventHandler)&HANDLE_INTR4;

CSL_intcPlugEventHandler(gpioIntcHandle, &isr_gpio); //绑定

//使能该事件(开始监听)

CSL_intcHwControl(gpioIntcHandle, CSL_INTC_CMD_EVTENABLE, NULL);

}

【TMS320C6455】

Features 12

• High-Performance Fixed-Point DSP (C6455) – 1.25-, 2.5-, 3.125-Gbps Link Rates

– 1.39-, 1.17-, 1-, 0.83-ns Instruction Cycle – Message Passing, DirectIO Support, Error

Time Mgmt Extensions, Congestion Control

– 720-MHz, 850-MHz, 1-GHz, 1.2-GHz Clock – IEEE 1149.6 Compliant I/Os

Rate • DDR2 Memory Controller

– Eight 32-Bit Instructions/Cycle – Interfaces to DDR2-533 SDRAM

– 9600 MIPS/MMACS (16-Bits) – 32-Bit/16-Bit, 533-MHz (data rate) Bus

– Commercial Temperature [0°C to 90°C] – 512M-Byte Total Addressable External

– Extended Temperature [-40°C to 105°C] Memory Space

• EDMA3 Controller (64 Independent Channels) • TMS320C64x+™ DSP Core

– Dedicated SPLOOP • 32-/16-Bit Host-Port Interface (HPI) Instruction

– Compact • 32-Bit 33-/66-MHz, 3.3-V Peripheral Component Instructions (16-Bit)Interconnect (PCI) Master/Slave Interface – Instruction Set EnhancementsConforms to PCI Local Bus Specification (v2.3)

– Exception Handling

• One Inter-Integrated Circuit (I2C) Bus

• TMS320C64x+ Megamodule L1/L2 MemoryArchitecture: • Two McBSPs

• 10/100/1000 Mb/s Ethernet MAC (EMAC) – 256K-Bit (32K-Byte) L1P Program Cache

– IEEE 802.3 Compliant [Direct Mapped]

– 256K-Bit – Supports Multiple Media Independent (32K-Byte) L1D Data CacheInterfaces (MII, GMII, RMII, and RGMII) [2-Way Set-Associative]

– 16M-Bit (2048K-Byte) L2 Unified Mapped – 8 Independent Transmit (TX) andRAM/Cache [Flexible Allocation] 8 Independent Receive (RX) Channels

– 256K-Bit • Two 64-Bit General-Purpose Timers, (32K-Byte) L2 ROMConfigurable as Four 32-Bit Timers – Time Stamp Counter

• Enhanced Viterbi Decoder Coprocessor (VCP2) • UTOPIA

– UTOPIA Level 2 Slave ATM Controller – Supports Over 694 7.95-Kbps AMR

– 8-Bit Transmit and Receive Operations up to – Programmable Code Parameters50 MHz per Direction

• Enhanced Turbo Decoder Coprocessor (TCP2)

– User-Defined Cell Format up to 64 Bytes

– Supports up to Eight 2-Mbps 3GPP

• 16 General-Purpose I/O (GPIO) Pins (6 Iterations)

• System PLL and PLL Controller – Programmable Turbo Code and DecodingParameters • Secondary PLL and PLL Controller, Dedicatedto EMAC and DDR2 Memory Controller • Endianess: Little Endian, Big Endian

• Advanced Event Triggering (AET) Compatible • 64-Bit External Memory Interface (EMIFA)

• Trace-Enabled Device – Glueless Interface to Asynchronous

Memories • IEEE-1149.1 (JTAG™) Boundary-Scan- (SRAM, Flash, and EEPROM) and Synchronous Memories (SBSRAM, ZBT Compatible SRAM) • 697-Pin Ball Grid Array (BGA) Package

– Supports Interface to Standard Sync Devices (CTZ, GTZ, or ZTZ Suffix), 0.8-mm Ball Pitch

and Custom Logic • 0.09-μm/7-Level Cu Metal Process (CMOS)

(FPGA, CPLD, ASICs, etc.) • 3.3-/1.8-/1.5-/1.25-/1.2-V I/Os,

– 32M-Byte Total Addressable External 1.25-/1.2-V Internal

Memory Space

• Four 1x Serial RapidIO® Links (or One 4x),v1.2 Compliant1Please be aware that an important notice concerning availability, stand

TMS320C6455技术文档:![]() TMS320C6455.pdf

TMS320C6455.pdf

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)