基于AD公司ADSP-21160M核心的含DSP电路板的测试方法与诊断分析

208

208

拍明

拍明

1.引言

在现代雷达系统中,含DSP电路板应用很广,含DSP电路板通常是以某种DSP芯片为核心,外围配以双口RAM(DRAM)和闪存(Flash)等器件。DSP芯片大多支持IEEE1149.1标准,并且在电路板中形成了边界扫描链,支持边界扫描。本文采用边界扫描技术与传统的外部输入矢量测试方法相结合,为含DSP电路板的测试与诊断提供了可以借鉴的方法。

2.电路原理简介及总体测试思想

2.1 电路原理介绍

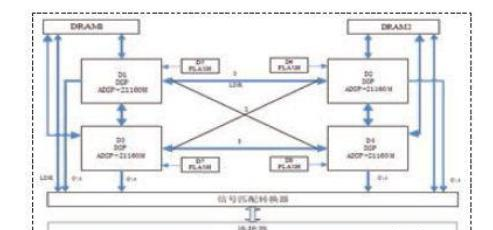

本文以雷达系统中某含DSP电路板为例对测试方法进行介绍,该电路以AD公司的ADSP-21160M为核心,外加DRAM、Flash、信号匹配转换器组成,Flash为DSP工作提供配置程序,4个DSP之间通过Link口进行数据交换,同时DSP的部分数据线和地址线与DRAM的数据线和地址线相连,DSP的Link口通过信号匹配转换器与外部连接器进行数据交换。该电路板在电路器件构成上使用了集成度较高的器件,芯片封装采用了PQFP132、PLCC100等多种表贴器件,器件引脚间距极小,采用探笔测试可能破坏电路工艺;并且电路上的DSP芯片不能从电路板上取下,所以采用边界扫描技术较为合理。如图1所示。

2.2 测试与诊断分析

对电路中核心器件DSP的资料分析,芯片具有JTAG测试接口,具备边界扫描测试的条件。但边界扫描测试不是基于IP内核的测试,使用边界扫描技术可以对电路测试但无法达到全面的测试与诊断,所以可以利用与传统的外部输入矢量测试方法相结合的方式实现电路的互连以及器件功能的测试,达到故障定位的目的。

2.3 测试系统组成

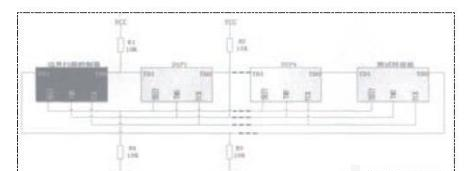

根据测试与诊断需求、测试工具以及电路本身的特点,设计稳压电路、JTAG测试接口转换电路以及加入一片具有边界扫描功能的芯片(FPGA)构成的电路实现了对电路测试所需的资源。

*稳压电路。稳压电路对测试系统程控电源发送过来的电压进行滤波、稳压后提供被测板的工作电压,保证被测板电源不会因为意外的原因产生突变。

*FPGA电路。该部分电路为被测板提供测试的地址和数据信号,测试时使用系统平台上的边扫控制器将被测电路板上DSP的测试链路的JTAG口与适配板上的FPGA的JTAG口构成一个测试链路,实现4个DSP之间互连测试、DSP与连接器连线测试、通过对FPGA配置程序实现FPGA与DSP间互连线测试。

*JTAG测试接口转接电路。将被测板上的DSP与测试转接板上的FPGA的JTAG接口构成一个测试通道,形成一个边界扫描测试链路。如图2所示。

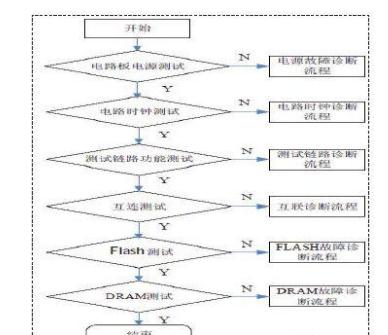

3.测试与诊断流程开发

基于边界扫描技术的测试诊断流程开发主要内容包括对边扫器件链路设计、引脚映射关系设置、边界扫描控制器相关文档设置,以及测试脚本语言的开发。图3是该电路板的测试诊断流程图。

*测试链路功能测试。实现对边扫器件构成的测试链路的连接情况进行测试,以及完成边扫器件引脚输入输出功能是否正常测试,只有在测试链路测试通过后才能使用边界扫描控制器进行后续测试。

*互连测试。依据被测板电路原理图和测试转接板原理图的网表文件,通过边界扫描测试软件实现对被测电路板上的边扫器件(DSP)、测试转接板上FPGA共五个器件间两两互连线的是否出现开路、短路、虚焊等问题的测试。

*Flash测试。被测电路板上的每个Flash的控制使能信号由不同的器件进行控制,在对Flash的测试过程中需要开发针对各Flash测试与诊断的测试脚本,在测试的过程中完成对故障的分析和定位,开发的测试脚本能够定位到器件的具体引脚故障。

*DRAM测试。通过连接器发送DRAM配置程序的触发信号,FPGA产生DRAM的读写时序,对DRAM的读写功能进行测试,FPGA读写的测试结果进行判读并生成一定的测试结果数据由连接器采集至测试系统,判断该部分电路功能是否正常。

按照上述开发过程实现的测试诊断流程的故障覆盖率≥83%,故障检测率约为92%,隔离到3个器件以内的故障隔离率≥95%.

4.总结

通过在测试转接板上放置具有边界扫描功能的芯片将该芯片与被测板上的边扫芯片构成测试簇,传统的外部输入矢量测试弥补了边扫测试的不足,进而实现了较高的电路测试覆盖率。

【ADSP-21160M】

80 MHz、600 MFLOPS、3.3v I/O、2.5v内核浮点SHARC

产品详情

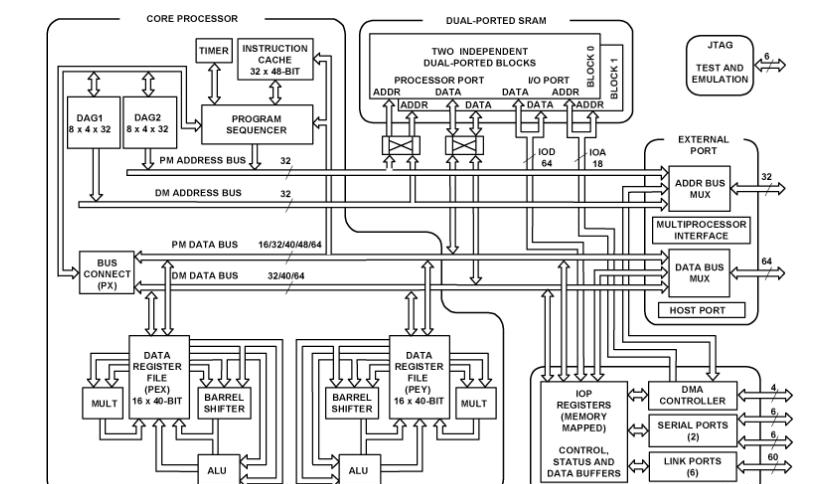

ADSP-21160M DSP是一款SHARC处理器,专门针对电话、医疗成像、雷达/声纳电子、通信、3D图形和成像等应用而进行了优化。ADSP-21160M采用一种单指令多数据(SIMD)架构。

利用2个计算单元(ALU,柱式移位器,MAC,寄存器文件),ADSP-21160M在一系列DSP算法的性能表现比ADSP-2106x高出5倍。该器件与广受欢迎的ADI第一代ADSP-2106x SHARC DSP代码兼容。与其他SHARC一样,ADSP-21160M是一款针对高性能DSP应用而优化过的32位处理器。ADSP-21160M包括一个可以处理32位定点和(32位、40位)浮点数据类型的80 MHz内核、一个双端口4 Mb片内SRAM、一个支持多处理的集成I/O处理器以及旨在消除I/O瓶颈的多个内部总线。

ADSP-21160M专门针对多处理拓扑结构而优化;SHARC通过链路端口或外部端口可以支持多处理。以下示意图显示了群集和链路端口多处理。通过外部端口,最多可以将6个21160M连接在一起,无需添加任何支持逻辑。该共享总线的仲裁集成于芯片上。群集中的每个SHARC都可以访问每个SHARC的内部存储器。通过外部端口连接,还可以共享可选的外部存储器。

6个链路端口则为无缝连接多处理系统提供了另一种方式。链路和群集可以同时使用,借助两种外设,可以开发出拥有数百个SHARC DSP的系统。

提高速度、减小尺寸

ADSP-21160M采用27mm x 27mm 400引脚PBGA(塑封球栅阵列)封装,比同性能处理器小40%。

提高单位功率的处理效率

21160M不但尺寸小、性能强,而且功耗低,使每瓦特MFLOPS达到新的水平。ADSP-21160M的典型功耗为2 w,使每瓦特性能达240 MFLOPS。使设计师可以在不超过PCI 25 w功耗上限的情况下,在PCI卡上使用多个处理器。利用8个21160M DSP,每个提供480 MFLOPS性能,标准PCI卡设计可以获得3.84 GFLOPS的性能,并为其他电路留出9 w的功率。

ADSP-21160M支持数百种现成的第三方软硬件产品和功能强大的ADI VisualDSP++开发系统,全面支持快速、简单的开发、调试和部署。

优势和特点

无缝群集最多支持6个SHARC

2维和3维阵列链路端口

分布式总线仲裁

统一的存储器空间

每个链路端口提供最高80MB/s I/O速率

320 MB/s外部端口

硬件支持令牌

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)