epm240数据手册

1

1

拍明芯城

拍明芯城

EPM240数据手册详尽介绍

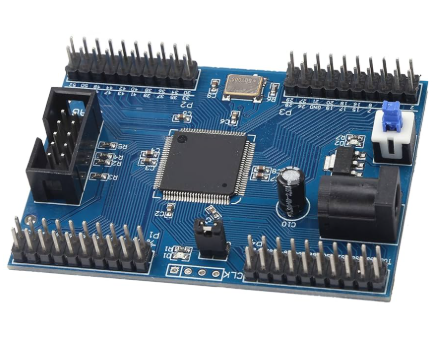

本文档旨在为用户提供关于EPM240系列可编程逻辑器件(CPLD)的详尽数据手册,涵盖其核心特性、架构、电气规格、引脚配置、编程与配置、应用指南等多个方面。

第一章:概述

EPM240是Altera公司(现为Intel®的一部分)推出的一款高效、低功耗的CPLD,属于MAX® II系列。该系列器件以其非易失性、高性能和低成本而闻名,广泛应用于各种数字系统设计中。EPM240的核心优势在于其基于闪存(Flash)的架构,无需外部配置芯片,即可在系统上电时立即开始工作。这种即时启动(Instant-on)特性对于许多对启动时间有严格要求的应用至关重要。

EPM240内部集成了可编程逻辑阵列、宏单元、I/O端口和丰富的时钟网络。其逻辑资源相对适中,非常适合作为控制逻辑、接口桥接、地址译码以及其他中小型数字逻辑任务的解决方案。该器件支持多种封装形式,以满足不同设计对尺寸和引脚数量的需求。其低功耗设计,特别是静态功耗极低,使其成为电池供电和对功耗敏感应用的理想选择。

在设计流程方面,EPM240利用Altera的Quartus® II设计软件进行编程。Quartus II提供了一整套从设计输入(如原理图或HDL语言)、综合、布局布线到编程下载的完整工具链。软件还包括了时序分析、功耗分析和仿真等高级功能,帮助设计者验证和优化其设计。EPM240还支持JTAG(Joint Test Action Group)接口,方便用户进行在线编程和系统内调试。

第二章:核心架构

EPM240的核心架构是其高性能和灵活性的基础。理解其内部结构对于高效利用该器件至关重要。

逻辑阵列模块(Logic Array Block, LAB)

EPM240的逻辑资源被组织成多个逻辑阵列模块(LAB)。每个LAB都包含一定数量的宏单元(Macrocell)。宏单元是EPM240最基本的逻辑构建块,每个宏单元都包含一个乘积项阵列、一个可编程寄存器和一个I/O控制块。

乘积项阵列:这部分是实现组合逻辑的核心。它由多个**乘积项(Product Term)**组成,每个乘积项都可以是多个输入变量的与(AND)运算结果。这些乘积项最终通过一个或(OR)门进行合并,以实现复杂的布尔函数。EPM240的乘积项分配机制非常灵活,一个宏单元可以共享来自其他宏单元的乘积项,从而高效地实现更复杂的逻辑。

可编程寄存器:每个宏单元都包含一个D触发器,可以用作存储元件。该触发器可以配置为D型、T型、JK型或SR型,并支持同步或异步清零和预置。这使得宏单元既可以实现组合逻辑,也可以实现时序逻辑,例如状态机、计数器和移位寄存器等。

I/O控制块:这部分负责控制宏单元输出信号到外部引脚的连接。它允许用户配置引脚为输入、输出、双向或三态,并提供多种驱动强度和上拉/下拉电阻选项。

可编程互连矩阵(Programmable Interconnect Array, PIA)

PIA是EPM240内部连接各个LAB和I/O引脚的全局路由资源。它是一个高速、低延迟的互连网络,能够将来自任何宏单元的输出、任何输入引脚的信号连接到任何其他宏单元的输入端。PIA的灵活性决定了EPM240可以实现复杂而高效的逻辑功能。通过PIA,设计者可以轻松地在不同LAB之间共享信号,无需担心布线拥塞或时序延迟。

第三章:电气规格

本章详细列出了EPM240系列器件的主要电气规格,包括工作电压、功耗、时序参数和I/O标准等。

工作电压

EPM240系列支持多种核心电源电压,通常为1.8V或2.5V。I/O电源电压(VCCIO)独立于核心电源,通常支持1.8V、2.5V和3.3V,这使得EPM240可以与不同电压标准的外部器件进行接口。

| 参数 | 描述 | 最小值 | 典型值 | 最大值 | 单位 |

| VCCINT | 核心电源电压 | 1.71 | 1.8 | 1.89 | V |

| VCCIO | I/O电源电压 | 1.71 | 1.8/2.5/3.3 | 3.6 | V |

功耗

EPM240的低功耗特性是其主要卖点之一。

静态功耗:由于其基于闪存的非易失性架构,EPM240的静态功耗非常低,通常在几十微安(μA)级别。这使其非常适合电池供电和便携式设备。

动态功耗:动态功耗与器件的开关频率、使用的逻辑资源和负载电容有关。Quartus II软件提供了详细的功耗分析工具,可以帮助设计者估算并优化其设计的动态功耗。

时序参数

EPM240的时序性能主要由输入到输出延迟(tPD)、寄存器到寄存器延迟(tSU)和最大工作频率(fMAX)等参数决定。

tPD(输入到输出延迟):该参数表示一个输入信号变化到相应的输出信号变化所需的时间。EPM240的tPD通常在几纳秒(ns)级别,这保证了其可以实现高速的组合逻辑功能。

fMAX(最大工作频率):fMAX表示EPM240内部寄存器可以稳定工作的最高时钟频率。该值与器件的内部时序路径和布线延迟有关。通常,EPM240可以支持数百兆赫兹(MHz)的时钟频率。

I/O标准

EPM240支持多种I/O标准,以确保与不同类型的外部器件兼容。常见的支持标准包括:

LVTTL/LVCMOS:低电压TTL/CMOS,支持1.8V、2.5V和3.3V电平。这是最常用的I/O标准,用于与微控制器、DSP和ASIC等器件连接。

PCI:用于与PCI总线接口,支持3.3V电平。

HSTL/SSTL:高速收发逻辑,用于高速存储器接口。

第四章:引脚配置与封装

EPM240提供了多种封装形式,以适应不同的应用需求。每种封装都有其独特的引脚排列和数量。

封装类型

EPM240系列常见的封装类型包括:

TQF144:薄型四方扁平封装,144个引脚,引脚间距0.5mm。这种封装提供了更多的I/O引脚,适合需要更多外部连接的设计。

BGA:球栅阵列封装,例如FBGA100(100个引脚)和FBGA256(256个引脚)。BGA封装具有更小的尺寸和更好的电气性能,适合高密度互连和高速设计。

QFP:四方扁平封装,例如QFP100。

引脚功能

每个引脚在EPM240中都可能具有多种功能。主要引脚类型包括:

专用输入引脚:通常用于时钟、清零和预置等全局信号。这些引脚具有特殊的时序特性,可以确保信号在器件内部的低延迟传播。

I/O引脚:这些引脚可以配置为输入、输出或双向引脚。它们与宏单元的I/O控制块相连,可以被编程为多种I/O标准。

电源引脚:包括VCCINT(核心电源)、VCCIO(I/O电源)和GND(地)。

编程引脚:这些引脚用于JTAG接口,例如TCK、TDI、TDO和TMS。

在设计中,正确连接和配置这些引脚至关重要。设计者需要参考Quartus II软件生成的引脚分配报告,以确保引脚连接正确,并且没有违反任何电气规格。

第五章:编程与配置

EPM240的编程与配置是其使用过程中的核心环节。

闪存(Flash)架构

EPM240基于非易失性闪存(Flash)技术,其配置数据永久存储在芯片内部。这意味着:

即时启动:EPM240上电后,其配置数据会自动从闪存加载到内部逻辑阵列中,无需外部配置芯片,实现了即时启动。

可重复编程:闪存可以被擦除和重新编程,允许设计者在开发过程中反复修改和测试其设计。

安全:EPM240提供了位流加密功能,可以防止未经授权的访问和复制,保护知识产权。

JTAG接口

JTAG接口是EPM240进行在线编程和调试的标准接口。它由四个引脚组成:

TCK(Test Clock):测试时钟引脚。

TDI(Test Data In):测试数据输入引脚。

TDO(Test Data Out):测试数据输出引脚。

TMS(Test Mode Select):测试模式选择引脚。

通过这些引脚,Quartus II软件可以与EPM240进行通信,将编译好的位流文件下载到芯片中。JTAG接口还支持边界扫描(Boundary Scan)功能,用于对PCB上的芯片进行测试和诊断。

编程过程

典型的EPM240编程过程如下:

设计输入:使用HDL语言(如VHDL或Verilog)或原理图输入设计。

综合与布局布线:Quartus II软件将设计综合成网表,并进行布局布线,将逻辑映射到EPM240的宏单元和互连矩阵中。

时序分析:软件对布局布线后的设计进行时序分析,生成时序报告,确保设计满足时序要求。

生成位流文件:软件生成用于编程的

.pof(Programmer Object File)文件。编程下载:使用Altera的USB Blaster等编程器,通过JTAG接口将

.pof文件下载到EPM240中。

第六章:应用指南与设计技巧

本章提供了一些关于如何高效利用EPM240的设计技巧和应用指南。

时钟管理

正确的时钟管理对于任何时序逻辑设计都至关重要。EPM240提供了一些专用的全局时钟网络,用于将时钟信号低延迟地分发到所有宏单元。

使用专用时钟引脚:为了获得最佳时序性能,应尽可能使用专用的时钟输入引脚来驱动全局时钟网络。

避免时钟歪斜:在多时钟域设计中,需要特别注意时钟歪斜(Clock Skew),即不同时钟路径上的时钟到达时间差异。Quartus II的时序分析工具可以帮助识别和解决这个问题。

时钟使能:如果需要控制某个模块的时钟,应使用时钟使能信号(Clock Enable),而不是通过组合逻辑门控时钟。门控时钟会导致时钟歪斜,甚至产生毛刺,对时序逻辑造成严重影响。

I/O设计

正确配置I/O标准:在Quartus II中,为每个I/O引脚正确配置其I/O标准,以匹配外部器件。

驱动强度与上拉/下拉电阻:根据外部器件的需求,配置I/O引脚的驱动强度。在需要时,启用内部上拉或下拉电阻,以确保引脚在未连接时的状态。

三态缓冲器:利用宏单元中的三态缓冲器(Tri-state Buffer)功能,可以实现双向总线接口。

优化技巧

资源共享:EPM240的乘积项共享功能非常强大,可以利用它来减少逻辑资源的使用。例如,在实现多个布尔函数时,如果它们共享一些乘积项,Quartus II的综合器会自动进行优化。

流水线设计:对于高速设计,可以使用流水线(Pipelining)技术来提高工作频率。流水线通过在关键路径上插入寄存器,将长路径分割成多个短路径,从而降低延迟。

利用Quartus II的高级功能:Quartus II提供了许多高级功能,如TimeQuest时序分析器、PowerPlay功耗分析器和SignalTap嵌入式逻辑分析仪。这些工具可以极大地帮助设计者验证和优化其设计。

应用实例

EPM240的典型应用包括:

微处理器接口:作为微处理器和外设之间的胶水逻辑(Glue Logic),实现地址译码、总线仲裁和数据转换等功能。

通信接口:实现SPI、I2C、UART等串行通信协议。

电机控制:生成PWM信号,实现步进电机或伺服电机的控制。

LED显示驱动:驱动多段LED或点阵LED显示屏。

传感器接口:对来自传感器的信号进行预处理和逻辑控制。

第七章:封装与订购信息

本章详细列出了EPM240系列器件的封装、引脚数量以及相关的订购信息。

EPM240封装类型

EPM240提供多种封装,以满足不同设计和成本要求。以下是一些主要封装类型及其特点:

TQF144封装:这是一种薄型四方扁平封装,共有144个引脚,引脚间距为0.5mm。该封装的优势在于引脚数量多,便于进行手动焊接和调试,且成本相对较低。它通常用于对尺寸要求不那么苛刻,但需要较多I/O引脚的应用。

FBGA100封装:球栅阵列封装,具有100个引脚。FBGA封装以其更小的尺寸和更优异的电气性能而著称。由于引脚为球形焊球,它更适合采用表面贴装技术(SMT)进行自动化生产。这种封装通常用于对空间有限制或对信号完整性有较高要求的应用。

QFP100封装:四方扁平封装,100个引脚。与TQF144类似,QFP封装也是一种引脚在外侧的封装形式,但通常尺寸更小。它在引脚数量和封装尺寸之间提供了一个很好的平衡。

QFP44封装:44个引脚的QFP封装,适用于资源需求较少、成本敏感且尺寸紧凑的设计。

每种封装都有其对应的可编程I/O引脚数量、专用时钟引脚数量和电源引脚数量。在选择封装时,设计者需要根据其设计所需的I/O数量、时钟资源和板级空间进行综合考虑。

订购信息

EPM240的订购型号通常由以下几个部分组成:

前缀:通常为EPM,表示产品系列。

逻辑单元数:240表示该器件包含240个逻辑单元。

封装类型:如T144(TQF144)、M100(FBGA100)、C100(QFP100)等。

速度等级:通常用数字表示,如**-5**、-7等。数字越小,速度等级越高,器件的时序性能越好,但价格也越高。

温度范围:I表示工业级温度范围(-40°C至+85°C),C表示商用级温度范围(0°C至+70°C)。

电源电压:如V表示3.3V I/O。

例如,一个典型的订购型号可能是EPM240T144C5,这表示一个具有240个逻辑单元、TQF144封装、商用级温度范围和速度等级为5的EPM240器件。在进行采购时,设计者应仔细核对完整的订购型号,以确保获得正确的器件。

第八章:设计流程与软件工具

Quartus II软件

Quartus II是Altera公司为EPM240等可编程逻辑器件提供的集成开发环境(IDE)。它提供了一套完整的工具链,覆盖了从设计输入到编程下载的整个流程。

设计输入:Quartus II支持多种设计输入方式,包括:

硬件描述语言(HDL):VHDL和Verilog是主流的HDL,用于描述复杂而高效的数字逻辑。

原理图输入:对于简单的逻辑或需要直观表示的设计,原理图输入是一种有效的选择。

State Machine Editor:用于方便地创建和编辑有限状态机(FSM)。

IP核(IP Core):Quartus II提供了一系列预先设计和优化的IP核,如处理器、存储器控制器、通信协议接口等,可以加速设计过程。

综合(Synthesis):Quartus II的综合器会将设计输入(HDL代码或原理图)转换成与EPM240内部结构相对应的网表。这一步是设计优化的关键,综合器会尝试将逻辑映射到乘积项和寄存器,并进行逻辑优化以减少资源使用和提高性能。

布局布线(Place and Route):综合完成后,布局布线器将网表中的逻辑单元(宏单元)放置到EPM240的物理位置上,并使用PIA连接这些逻辑单元。布局布线过程直接影响设计的时序性能,Quartus II会尽力优化布线以最小化延迟。

仿真与验证:Quartus II集成了多种仿真工具:

功能仿真:在综合前对HDL代码进行仿真,验证其逻辑功能是否正确。

时序仿真:在布局布线后进行仿真,考虑了物理延迟,以验证设计在实际硬件上的时序性能。

SignalTap II:这是一款嵌入式逻辑分析仪,允许设计者在硬件上实时捕获和分析内部信号,极大地简化了调试过程。

编程器:Quartus II的编程器工具用于将编译好的配置文件(

.pof)通过USB Blaster等编程器下载到EPM240中。

设计流程的最佳实践

分模块设计:将复杂的设计分解成多个小模块,每个模块实现一个特定的功能。这有助于提高设计的可读性和可维护性,也便于模块的复用。

使用同步设计:尽量避免异步逻辑,所有时序逻辑都应由一个或几个同步时钟驱动。这可以简化时序分析,避免竞争和冒险。

约束文件(Constraint File):使用**.qsf**文件对设计进行约束,例如指定时钟频率、输入输出延迟和引脚分配等。正确的约束可以指导Quartus II进行更有效的布局布线和时序优化。

迭代优化:设计不可能一次就完美。通常需要通过多次迭代,利用Quartus II的时序报告和功耗报告,不断调整设计、优化代码或改变约束,以满足所有设计要求。

第九章:EPM240与其他CPLD/FPGA的比较

为了更好地理解EPM240的定位和优势,本章将对其与同类器件进行比较。

EPM240 vs. EPM570

EPM570是MAX II系列中逻辑资源更多的一款器件。

逻辑资源:EPM570拥有更多的逻辑单元(570个),因此可以实现更复杂的逻辑功能。

功耗:由于逻辑资源更多,EPM570的功耗通常高于EPM240。对于功耗敏感的低端应用,EPM240是更合适的选择。

成本:EPM240的成本低于EPM570,适用于对成本有严格限制的项目。

EPM240 vs. MAX V系列

MAX V系列是Altera MAX®系列的下一代产品,具有更低的功耗和更优化的架构。

功耗:MAX V系列进一步优化了功耗,尤其是在静态功耗方面。

架构:MAX V采用了新的架构,提供了更高效的逻辑单元和更灵活的路由资源。

兼容性:MAX V系列在软件和引脚上与MAX II系列有一定的兼容性,但可能需要进行一些设计修改。

成本与性能:MAX V系列通常在性能上略胜一筹,但对于许多中低端应用,EPM240的性能已足够,且成本更具优势。

EPM240 vs. FPGA

FPGA(Field-Programmable Gate Array)与CPLD在架构和应用上存在显著差异。

架构:CPLD(如EPM240)基于乘积项阵列和闪存,而FPGA则基于查找表(LUT)和SRAM。

配置:CPLD是非易失性的,配置数据存储在内部闪存中,上电即启动。FPGA的配置数据存储在易失性的SRAM中,上电后需要从外部配置芯片加载,因此启动时间较长。

逻辑资源:FPGA的逻辑资源比CPLD多得多,可以实现更复杂的系统级功能,如软核处理器、高速接口等。

时序性能:CPLD的路由资源是固定的,时序性能相对可预测。FPGA的布线资源更灵活,时序性能更依赖于布局布线结果。

应用领域:CPLD通常用于中小型控制逻辑、胶水逻辑和时序关键的小模块。FPGA则用于高性能计算、通信、视频处理等需要大量逻辑资源和高速处理的应用。

总而言之,EPM240以其即时启动、低功耗和低成本的优势,非常适合作为中低端数字逻辑设计的首选。它在接口桥接、地址译码和简单的状态机实现等应用中表现出色。

第十章:技术支持与资源

Altera(现为Intel®)为EPM240用户提供了丰富的技术支持和学习资源。

官方网站

Intel® FPGA的官方网站是获取最新信息、下载软件和访问技术文档的主要渠道。用户可以在网站上找到:

产品页面:详细介绍EPM240的特性、应用和技术规格。

Quartus II软件下载:提供最新版本的Quartus II软件以及相关的更新和补丁。

数据手册与应用笔记:提供本手册的官方版本以及各种详细的应用笔记,介绍EPM240在特定应用中的设计方法。

在线培训:提供免费的在线课程和视频,帮助用户学习如何使用Quartus II和EPM240。

社区与论坛

除了官方资源,还有许多在线社区和论坛可以帮助用户解决设计中遇到的问题。在这些社区中,用户可以与其他工程师交流经验、分享代码和讨论设计技巧。

技术支持

如果用户在设计中遇到无法解决的难题,可以联系Intel® FPGA的技术支持团队。技术支持通常通过电子邮件、在线表单或电话提供,能够提供专业的指导和帮助。

通过充分利用这些资源,设计者可以更高效地学习和使用EPM240,从而加快产品开发周期,提高设计质量。

结论

EPM240作为MAX II系列中的一款经典CPLD,以其非易失性、即时启动、低功耗和低成本的特点,在众多中小型数字逻辑设计中占据了重要地位。本文档详细介绍了其核心架构、电气规格、编程与配置、设计技巧以及与其他器件的比较,旨在为读者提供一个全面而深入的参考。无论是初学者还是经验丰富的工程师,都可以通过本手册加深对EPM240的理解,并将其成功应用于实际项目中。希望本手册能成为您设计过程中的得力助手。

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)