74ls20逻辑图

1

1

拍明芯城

拍明芯城

引言:74LS20的数字电路核心地位

在数字逻辑设计领域,74LS20作为一款经典的双四输入与非门集成电路,自诞生以来便以其高可靠性、低功耗和灵活的应用特性,成为工程师构建复杂数字系统的核心组件之一。本文将从逻辑图解析、功能特性、应用场景到设计实践,全方位剖析74LS20的技术细节,为读者呈现一篇兼具理论深度与实用价值的指南。

第一章:74LS20基础架构与逻辑图解析

1.1 芯片内部结构图谱

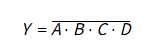

74LS20采用标准的14引脚DIP封装,其内部集成两组完全独立的四输入与非门单元。每组逻辑单元由四个输入端(A、B、C、D)和一个输出端(Y)构成,逻辑表达式为:

当所有输入均为高电平(1)时,输出为低电平(0);若任意输入为低电平(0),则输出高电平(1)。这种特性使其天然适合实现“全1出0,有0出1”的逻辑判断。

1.2 引脚功能与逻辑连接图

芯片引脚布局严格遵循TTL系列规范:

输入引脚:每组门包含四个输入端(如第一组为1A、1B、1C、1D,第二组为2A、2B、2C、2D)。

输出引脚:两组门的输出分别为1Y(Pin6)和2Y(Pin8),采用开路集电极结构,需外接上拉电阻(通常3.3kΩ~10kΩ)以确保高电平稳定。

电源与地:VCC(Pin14)接+5V电源,GND(Pin7)接地。

逻辑连接示意图:

A1 ----|B1 ----|C1 ----|---- NAND ---- Y1D1 ----|A2 ----|B2 ----|C2 ----|---- NAND ---- Y2D2 ----|

1.3 真值表与逻辑功能验证

通过真值表可直观验证74LS20的逻辑行为:

| A | B | C | D | Y |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 1 |

| 1 | 1 | 1 | 1 | 0 |

实验中可通过LED指示电路观察输出状态:当输入全为高电平时LED熄灭(输出低电平),否则LED点亮(输出高电平)。

第二章:74LS20核心技术特性详解

2.1 电气参数与性能边界

电源电压:典型工作电压+5V,允许范围±5%,静态电流消耗约1.6mA。

输入/输出特性:

高电平输入电压(VIH)最小2.0V,低电平输入电压(VIL)最大0.8V。

输出低电平(VOL)最大0.4V(@8mA负载),高电平依赖上拉电阻。

传播延迟:输入到输出延迟约16ns,满足高速数字系统需求。

2.2 抗干扰与可靠性设计

噪声容限:高输入阻抗与宽噪声裕度(0.4V~2.0V)使其在电磁干扰环境中表现稳定。

级联能力:开路集电极输出支持多芯片并联,通过共享上拉电阻实现“线与”逻辑。

2.3 封装与热设计

DIP-14封装:便于手工焊接与原型开发,工业级版本支持-40°C~85°C宽温范围。

散热考量:在高频大电流场景下,建议加装散热片以避免热失效。

第三章:74LS20典型应用场景剖析

3.1 组合逻辑电路设计

译码器扩展:与74LS138配合实现多级译码,例如构建3-8线译码器的扩展电路。

多路复用器:通过逻辑组合实现16选1数据选择器,显著减少芯片数量。

3.2 工业控制与自动化

安全联锁系统:在机械手臂控制中,通过四输入与非门实现多传感器信号的“与”逻辑,确保操作安全。

电机驱动保护:监测电流、温度、电压等多参数,任意异常触发保护动作。

3.3 汽车电子与通信设备

引擎管理单元:结合节气门位置、转速、氧传感器等信号,通过74LS20实现点火时序控制。

数据通信接口:在RS-232/RS-485转换电路中,用于电平转换与信号调理。

3.4 消费电子创新应用

四人表决器:通过两组四输入与非门实现少数服从多数逻辑,LED与数码管直观显示结果。

电子密码锁:多按键组合输入验证,任意错误触发报警电路。

第四章:74LS20设计实践与调试技巧

4.1 电路设计规范

输入保护:串联220Ω限流电阻,防止静电或过压损坏芯片。

上拉电阻选择:根据负载电流计算,典型值4.7kΩ平衡功耗与速度。

去耦电容配置:VCC与GND间并联0.1μF陶瓷电容,抑制电源噪声。

4.2 仿真与原型验证

Proteus仿真:搭建四人表决器模型,验证逻辑功能与时序。

硬件调试步骤:

检查电源与地连接,确保无短路或虚焊。

逐级测试输入信号,用示波器观测输出波形。

通过LED或逻辑分析仪确认逻辑状态。

4.3 故障排查与优化

常见问题:

输出恒定低电平:检查上拉电阻是否断路或输入短路。

逻辑翻转异常:确认输入信号电平是否符合VIH/VIL规范。

性能优化:

减少传输线长度,降低寄生电容影响。

在高频应用中,采用表面贴装封装(如SOIC-14)减小寄生参数。

第五章:74LS20与现代数字电路的融合

5.1 CMOS版本对比(74HC20)

性能提升:74HC20工作电压范围更宽(2V~6V),静态功耗更低(<1μA)。

兼容性设计:TTL与CMOS电平转换时需注意输入阈值差异。

5.2 FPGA/CPLD中的软核实现

HDL描述示例:

module NAND4 (input A, B, C, D, output Y);assign Y = ~(A & B & C & D);endmodule

优势分析:软核实现可灵活调整输入数量与逻辑功能,但需权衡资源占用与速度。

5.3 未来趋势:74LS20在物联网中的应用

低功耗设计:在传感器节点中,74LS20可用于信号调理与逻辑判断,延长电池寿命。

边缘计算:结合微控制器,实现本地决策逻辑,减少云端通信延迟。

结论:74LS20的技术遗产与创新空间

历经数十年技术迭代,74LS20凭借其简洁的逻辑结构、稳定的性能表现,仍在现代数字系统中占据一席之地。从工业控制到消费电子,从经典TTL到新兴物联网,74LS20的设计哲学——通过基础逻辑门构建复杂系统——持续启发着工程师的创新实践。未来,随着低功耗设计、异构集成等技术的演进,74LS20及其衍生器件必将继续拓展数字逻辑的应用边界。

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)