什么是stm8s103f3p6,stm8s103f3p6的基础知识?

20

20

拍明芯城

拍明芯城

一、STM8S103F3P6概述

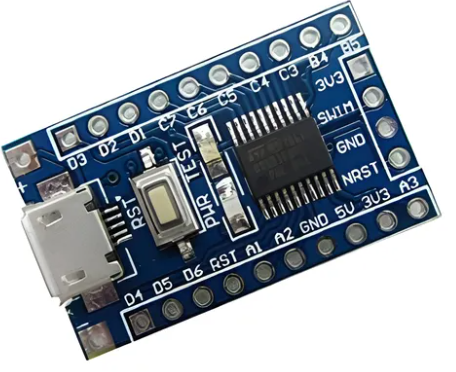

STM8S103F3P6是意法半导体(STMicroelectronics)推出的一款基于STM8内核的高性能8位微控制器。这款芯片集成了多种常用外设,具有成本低、功耗低、性能稳定、易于开发等优点,广泛适用于消费电子、工业控制、家用电器、智能仪表等领域。本章将从芯片定位、产品系列、应用场景等方面对STM8S103F3P6进行初步介绍。

STM8系列微控制器是ST在8位领域的旗舰产品,具有非常完善的生态系统和开发工具链,其中STM8S系列定位为高性能、高性价比的通用MCU,核心时钟频率最高可达16MHz,内部集成了多种通讯接口和模拟外设。STM8S103F3P6属于STM8S《STM8S Medium-density Access Line》系列中的代表型号之一,其主要特点如下:

CPU内核:STM8内核,基于哈佛结构,采用CISC指令集,最高主频16MHz。

存储资源:集成8KB闪存(Flash)、1KB SRAM,以及128字节EEPROM,满足嵌入式应用对代码、数据存储的需求。

片上外设:包括定时器、通用I/O、ADC、USART、I²C、SPI等常用接口,能够支持多种外部设备扩展。

封装形式:32引脚LQFP(7×7mm)封装,适合中小型应用场景。

工作电压:2.95V至5.5V宽范围供电,兼容多种供电设计。

STM8S103F3P6的目标市场主要集中在对成本、功耗、外设资源有一定要求,但对处理能力没有特别高负载的场景。典型应用包括家电面板控制、安防系统、智能仪表、玩具电子、工业传感器接口等。由于STM8系列在国内外均有良好的技术支持和丰富的应用案例,针对初学者与有经验的工程师都提供了丰富的软件库、开发板和技术手册,使得基于STM8S103F3P6的方案更容易实施和量产。

二、STM8S103F3P6基本参数

在了解STM8S103F3P6之前,首先要掌握其主要的技术参数和功能模块,以便在工程设计中进行评估和选型。以下内容着重列举并解释STM8S103F3P6的各项关键参数。

CPU与时钟系统

核心:STM8CIS架构的8位CPU;

工作频率:最高可达16MHz;

时钟源:内部高速振荡器(HSI,16MHz)和内部低速振荡器(LSI,38kHz),外部晶振支持最高16MHz;

时钟控制:具有PLL倍频功能,可将HSI内部振荡器分频后倍频以获得稳定的系统时钟。

存储器

闪存(Flash):8KB,用于存储程序代码,支持全片擦写与页擦写;

数据EEPROM:128字节,可用于存储非易失性数据,如配置信息、标定信息等;

SRAM:1KB,供程序运行时存放变量和堆栈使用;

读保护级别:具备三种安全级别,可根据需求锁定闪存,防止程序被非法读取或篡改。

供电与功耗

工作电压:2.95V至5.5V范围内;

低功耗模式:具备三种省电模式(Wait、Stop和Halt),可根据应用场景降低功耗;

典型功耗:在运行模式下,16MHz时钟、典型负载条件下约3–5mA;在Stop模式下一般为几十微安;

时钟与重置

多种复位源:上电复位(POR/PDR)、盗用时钟复位(IWDG)、看门狗复位(WWDG)、软件复位等;

独立看门狗(IWDG):32 kHz内部时钟,时间可编程;

窗口看门狗(WWDG):内置复位窗口功能,可以更安全地监控程序运行;

I/O与封装

通用I/O口:多达37个I/O引脚(具体可用I/O数量与封装形式相关);

封装:STM8S103F3P6常见为LQFP32(7×7mm)封装,也有其他封装形态;

I/O电气特性:可推挽或开漏输出,多种中断触发方式,带有上拉或下拉功能;

定时器与PWM

高级控制定时器(TIM1):16位定时器,带有三相PWM输出,适合电机驱动应用;

通用定时器(TIM2、TIM3):均为16位定时器,可生成PWM、输入捕获、输出比较功能;

基本定时器(TIM4):8位定时器,支持溢出中断,适用于简单的延时或定时任务;

串行接口

USART:一个综合性串口,支持异步模式、同步模式、LIN协议及多主机多从机模式;

SPI:一个全双工、3线或4线SPI接口,支持主/从模式,最高速可达2.25 Mbps;

I²C(两线接口):一个硬件I²C接口,支持标准模式(100kHz)和快速模式(400kHz);

模数转换器(ADC)

10位分辨率ADC:三个独立的12通道模拟输入(内部通道加外部通道总共达15路);

转换模式:单次转换、连续转换和扫描模式;

数据对齐:左对齐和右对齐选择;

精度:典型误差为±1 LSB至±2 LSB,通过校准可进一步提高测量精度;

其他外设

看门狗定时器(IWDG、WWDG):保证系统在异常情况下复位;

看门狗复位保护:可配置看门狗标准模式或窗口模式;

RTC(实时时钟):可通过LSE(低速外部晶振)实现时钟功能;

控制器局域网络(CAN):STM8S103F3P6不具备本地CAN控制器;

低电压检测器(PVD):可设置比较阈值,在VDD低于设定电压时触发中断或复位;

工作温度与可靠性

工作温度范围:–40°C至+85°C(工业级);

存储温度范围:–65°C至+150°C;

片上自测试功能:包含工作内部参考电压(VREFINT)监控,可检测电压异常;

通过以上参数可以看出,STM8S103F3P6在资源配置上较为均衡,既满足了对存储容量、安全保护、外设丰富度的需求,又保持了较低的系统成本与功耗。这也为开发者在各种嵌入式场景下提供了充足的设计空间和稳定性保障。

三、STM8S103F3P6硬件架构

在深入了解STM8S103F3P6具体功能之前,需要对其内部硬件架构进行整体把握,了解各模块之间的关系和数据流向。本节从核心子系统、存储子系统、总线架构、外设子系统四个方面进行分析。

核心子系统

STM8S103F3P6采用STM8核心,具备如下特点:

哈佛结构:指令总线和数据总线分离,支持同时获取指令和数据,提高了指令吞吐率;

CISC指令集:丰富的指令集,使得在汇编编程时更加灵活;

单周期指令执行:绝大多数指令在一个时钟周期内完成,执行效率较高;

内核供电:独立的供电域以保证内核在不同电压下依然稳定工作;

调试与仿真支持:内置On-Chip Debug(OCD)模块,通过SWIM接口即可对芯片进行在线调试与单步跟踪。

存储子系统

STM8S103F3P6内部存储资源主要包括Flash、EEPROM和SRAM:

1KB容量,用于存放程序运行时工作变量、堆栈和寄存器映射区;

位于数据存储区与外设寄存器区之间,通过数据总线与CPU连接;

容量128字节,字节可独立擦写;

内置Flash控制器提供自动写入和擦除功能,支持行擦写与行写入操作;

数据可在掉电后保持较长时间,适合保存配置信息、电量数据等;

分为Boot区与应用区:Boot区大小一般为1KB,用于存放系统引导、Bootloader或安全启动代码;应用区则用于存放用户程序;

擦写粒度:整个扇区(页)擦写,页大小为1KB;

可在运行时通过特定寄存器组合进行页写充和页擦除;

读保护级别(RDP):三级保护机制,可对Flash内容进行锁定,防止外界读取或更改;

Flash(程序存储)

EEPROM(数据存储)

SRAM(数据缓存)

总线架构与互联矩阵

STM8S103F3P6采用分级总线(Bus matrix)架构,主要包括:

PRINC(主总线):连接CPU、Flash、DMA、系统配置模块(SYSCFG)等;

HSI(高速总线):连接外设寄存器、SRAM;

LSI(低速总线):连接模拟子系统(ADC、电压参考)、看门狗定时器、RTC等;

互联矩阵:协调各主设备对总线的访问优先级,采用轮询或优先级仲裁,以保证关键外设(如Flash、SRAM)的及时访问;

DMA(直接存储器访问):STM8S103F3P6本身不带硬件DMA,数据传输由CPU软实现;

外设子系统

STM8S103F3P6集成了丰富的外设模块,分为时钟与重置模块、I/O与GPIO模块、定时器模块、通信接口模块、ADC模块、系统管理模块等:

看门狗定时器(IWDG、WWDG):确保系统在异常状态下自动复位;

低电压检测(PVD):可在供电电压低于阈值时触发中断或复位,保护系统;

实时时钟(RTC):可选用内部LSI或外部低速晶振(LSE)作为时钟源,实现计时与唤醒功能;

参考电压(VREFINT):用于ADC校准与系统监测;

10位分辨率,具备15路模拟输入通道(包括内部温度传感器、内部参考电压);

多种转换模式:单次转换、连续转换、扫描模式,可根据应用需求灵活选择;

数据寄存器支持左对齐与右对齐,方便不同精度应用;

可通过DMA方式读取数据(STM8S103F3P6无硬件DMA,可通过软件模拟);

USART

SPI

I²C

支持异步(UART)与同步通信,最高波特率可达115200 bps;

支持多主机通讯、半双工模式,可配置为LIN协议;

支持主从模式,最高通信速率为fMASTER/4;

三线或四线模式可选,支持硬件 NSS 管脚管理,以及软件片选;

支持标准模式(100 kHz)与快速模式(400 kHz);

支持多主、多从拓扑结构,具备仲裁和使能仲裁捕获功能;

硬件自动ACK,无需软件干预;

TIM1(高级定时器)

TIM2与TIM3(通用定时器)

TIM4(基本定时器)

16位进/降计数,支持三相互补PWM输出,死区时间可编程;

支持死区插入、刹车功能、电流采样、紧急停止等高级特性;

主要面向电机驱动、逆变器等对PWM性能要求较高的场景;

16位计数器,支持单脉冲模式、PWM、输入捕获、输出比较;

具备可编程预分频器与自动重装载寄存器,精确控制定时周期;

通道数分别为4路(TIM2)和4路(TIM3),可配合GPIO做高精度测量和信号生成;

8位计数器,具备中断功能,适用于简单定时、看门狗驱动等;

最小时钟可分频到LSI频率,功耗更低;

每个I/O口可单独配置为推挽输出、开漏输出、输入模式、复用功能等;

每个引脚具备可编程上下拉或高阻状态;

可配置外部中断(EXTI),支持上升沿、下降沿或双沿触发;

引脚复用:同一引脚既可作为通用I/O,也可映射为定时器通道、通信接口、ADC通道等;

CLK:支持HSI、LSI、HSE(外部低速晶振)等多种时钟源;可通过时钟控制寄存器(CKDIVR、SWIMCCR等)选择主时钟及分频;

PCKENR寄存器:可按位使能或关闭各外设的时钟,以降低功耗;

多种复位源(POR、PDR、IWDG、WWDG、软件复位)通过RSTR寄存器进行配置;

时钟与重置模块(CLK & RST)

I/O与GPIO模块

定时器模块(TIM1、TIM2、TIM3、TIM4)

通信接口模块

ADC模块

系统管理模块

通过对STM8S103F3P6硬件架构的分析可以看出,该器件在总线设计、外设丰富度、功耗控制方面进行了充分优化。分级总线架构使得关键资源能够在多外设同时访问时保持性能;丰富的定时器及通信接口能够满足工业控制、消费电子等多种应用需求;低功耗模式与安全保护机制也为系统的可靠性与稳定性提供了保证。

四、引脚功能与电气特性

在设计硬件系统时,正确理解STM8S103F3P6的引脚分配与电气特性至关重要。本节将详细介绍该芯片的引脚排列、复用功能以及电气参数。

引脚分配(Pinout)

STM8S103F3P6常见封装为LQFP32(7×7mm),其引脚布局如下:

markdown复制编辑 _________ | 1 32 | | | | | | 16 17 | |________|

具体引脚功能请参考数据手册,这里仅列举主要引脚及其功能:

VDD(1、20脚):电源正极,2.95V–5.5V;

VSS(8、16脚):电源地;

PA0–PA7(引脚2、3、4、5、6、7、9、10):通用I/O口组A,部分引脚复用ADC、USART功能;

PB0–PB7(引脚11、12、13、14、15、17、18、19):通用I/O口组B,部分引脚支持I²C、SPI、TIM功能;

PC0–PC7(引脚21、22、23、24、25、26、27、28):通用I/O口组C,部分引脚支持外部中断、TIM、ADC功能;

PD0–PD7(引脚29、30、31、32及引脚9、10):通用I/O口组D,部分引脚支持I²C、SPI等;

CLK(引脚31):时钟输出,可将HSI定时信号输出到外部;

RESET(引脚19):外部复位输入,复位引脚具有上拉电阻,低电平触发复位;

SWIM(引脚30):串行线调试接口,用于在线仿真与编程;

ADC输入:PA2、PA3、PA5、PA7、PB2、PB3、PB4、PB5、PB6、PB7、PC0、PC1、PC2、PC3、PC4;

引脚复用与功能映射

STM8S103F3P6的引脚复用设计使得同一个物理引脚可以通过寄存器配置实现多种功能。例如:

在开发中,通常使用TIM2/3/4与GPIO配置寄存器(CR1、CR2)及AFR(Alternate Function Register)来选择引脚功能。例如,要将PB5配置为I²C SDA,需要在I2C模块及相应AF寄存器中启用I²C功能,并在PB5的DDR寄存器中设置为输入/上拉模式。

PA5可以配置为GPIO,也可配置为ADC通道5;

PB3可以配置为USART TXD,也可用于TIM2通道2输出;

PC3可以作为外部中断EXTI3,也可作为SPI MOSI引脚;

电气特性

在电气设计时,应关注STM8S103F3P6的输入/输出电流能力、电平兼容性等参数:

最大电源电压:VDD最大为5.5V,超过此电压可能损坏内部电路;

输入高电平阈值:在VDD=5.0V时,VIH约为0.7×VDD以上;

输入低电平阈值:VIL约为0.3×VDD以下;

输出驱动能力:在VDD=5.0V时,推挽输出可提供最大20mA电流;但为了保证引脚可靠性与长期寿命,推荐工作电流不超过10mA;

上拉/下拉电阻:内部可配置约30–50kΩ的上拉或下拉电阻,用于输入浮空时保持稳定电平;

开漏输出:某些引脚可配置为开漏模式,以连接外部上拉并实现I²C总线或需要线与逻辑的场景;

ESD保护:每个I/O引脚具有±4kV(人体模型)的ESD保护能力,但在设计时仍应注意外部浪涌保护和滤波;

外部设备互联与PCB设计注意事项

在实际电路设计中,遵循以下原则可以提高系统稳定性与抗干扰能力:

电源去耦:在VDD与VSS引脚间放置0.1μF和10μF的陶瓷/钽电容滤波,靠近芯片封装;

复位电路:建议在RESET引脚外部增加10kΩ上拉电阻和0.1μF电容,以保证在上电或电源干扰时产生干净的复位脉冲;

晶振布局:如果使用外部晶振(HSE),保持晶体与微控制器引脚之间走线最短,并在晶振引脚旁放置小电容;

模拟地与数字地分离:ADC等模拟输入引脚应尽量靠近模拟地,并避免与高速数字信号线并行;

布线规整:高速信号线(如USART TX/RX、SPI SCK/MOSI/MISO)应尽量短并保持阻抗可控;

上拉/下拉电阻:对外部按钮、开关等输入引脚,建议在必要时使用外部上拉/下拉电阻,与内部电阻配合实现更稳定的输入检测;

通过对STM8S103F3P6引脚功能和电气特性进行深入分析,可以为硬件设计人员提供明确的指导,确保在PCB布局、器件选型、外围电路设计等方面做到兼顾性能和可靠性,从而降低系统故障率和后期维护成本。

五、STM8内核与指令集

STM8S微控制器搭载的是STM8核心,属于8位精简指令集计算机(CISC)架构。理解STM8内核及其指令集特点,对于开发者在进行程序优化、底层驱动编写和调试时具有重要意义。本节重点介绍STM8内核结构、寄存器组、指令集体系、寻址模式以及中断与异常处理等内容。

STM8内核架构

STM8核心采用哈佛结构:

指令总线与数据总线分离,CPU可同时访问指令存储器与数据存储器;

流水线设计:典型地分为取指、译码、执行三个阶段,支持多级流水操作;

寄存器组:包括通用寄存器、堆栈指针(SP)、程序计数器(PC)、状态寄存器(CCRL、CCRH)等;

单周期指令执行:绝大多数指令仅需一个主频周期完成,部分复杂指令可能需要多个周期;

核心寄存器与状态寄存器

Z(零标志):结果为0时置位;

C(进位标志):算术运算发生进位或借位时置位;

N(符号标志):结果最高位为1时置位;

V(溢出标志):有符号运算产生溢出时置位;

H(半进位标志):BCD运算时用于检测低四位进位;

I(中断使能标志):全局中断使能位;

X(扩展标志):扩展结果位,用于多字节算术运算中;

A寄存器:累加器,主要用于算术与逻辑运算;

W寄存器:辅助寄存器,用于数据移动、处理;

R0–R5:可用于数据暂存,也可作为地址寄存器进行指针寻址;

D寄存器:16位宽寄存器,用于处理16位数据访问与运算;

通用寄存器:STM8共有六个8位通用寄存器R0–R5,以及一个16位寄存器R6(也称为D寄存器,高字节为A寄存器,低字节为W寄存器),其中:

堆栈指针(SP):16位,可访问内部SRAM区域;

程序计数器(PC):16位,用于跟踪下一条执行指令的地址;

状态寄存器(CCR):拆分为CCRH和CCRL两个8位寄存器,包含若干标志位:

指令集与寻址模式

STM8指令集包含180余条指令,可分为以下几大类:

STM8支持以下寻址模式:

立即寻址:操作数直接嵌入指令,如 MOV A, #0x55;

寄存器寻址:操作对象为内部寄存器,如 ADD A, R1;

寄存器间接寻址:通过寄存器指向内存,如 LD A, (HL);

绝对地址寻址:指定直接地址,如 LDW X, $2000;

相对寻址:跳转指令常用,偏移量相对于PC,如 JR $+10;

堆栈寻址:通过SP寄存器访问栈区,如 PUSH R2;

位寻址:可以对位变量进行直接操作,如 BSET (PORTA.3);

数据传送指令:MOV、LD、ST、LDW、STW等,用于寄存器、内存、常量之间的数据移动;

算术与逻辑指令:ADD、SUB、MUL、DIV、AND、OR、XOR、CP(比较)、INC、DEC等;

位操作指令:BSET(置位)、BRES(清位)、BCLR(清位)、BTG(翻转)等,用于对寄存器或内存中的单个位进行操作;

跳转与分支指令:JR(无条件短跳转)、JRE(有条件短跳转)、JRA(绝对无条件跳转)、Jxx(各种条件跳转)、CALL、RET等,用于程序流程控制;

堆栈操作:PUSH、POP,用于保存与恢复寄存器、标志、PC等;

中断控制与系统指令:EI(使能全局中断)、DI(禁止全局中断)、RETF(从中断返回)、HALT(低功耗挂起)等;

特殊指令:NAP、WFE(等待事件)等,用于处理低功耗和并发事件;

中断系统与异常处理

STM8S103F3P6内部包含多达32个中断向量,用于响应不同外设或系统事件,如外部中断、定时器中断、ADC中断、USART中断、I²C中断等。中断优先级由硬件固定,优先级从0(最高)到31(最低)排列。中断处理流程如下:

除此之外,STM8还支持软件中断(SWI),由 SWI 指令触发,用于系统调用或仿真测试。由此可见,STM8中断系统既保证了实时响应能力,又保持了嵌入式系统常见的嵌套与优先级特性。

触发条件成立,将对应中断请求标志位置位;

如果I位(全局中断使能)为1且当前无高优先级中断,则进行中断响应;

CPU自动将PC和CCR压入堆栈,切换至中断服务程序(ISR);

中断服务结束后,通过RETF指令恢复PC和CCR,返回中断前执行状态;

六、系统时钟与功耗管理

对于嵌入式系统来说,时钟系统与功耗管理是设计重点。合理配置时钟源与时钟分频可以兼顾性能与功耗;同时,巧妙使用低功耗模式有助于延长电池供电设备的工作时间。本节从时钟选型、时钟树结构及功耗优化三个方面进行探讨。

时钟源与时钟树结构

STM8S103F3P6具有多种时钟源选择:

STM8S时钟树结构:

HSI或HSE通过PLL倍频器,可获得高达16MHz的系统时钟;

主系统时钟分配给CPU、Flash、外围外设;

各外设还能通过PCKENR寄存器单独开关时钟,以节省功耗;

当进入低功耗模式时,主时钟可切换至LSI或LSE,以保持最低功耗下的基本功能;

通常为32.768kHz晶体,用于RTC或低功耗唤醒;

精度高但启动时间长,适合超低功耗、长时间计时需求。

频率约为38kHz,可用于看门狗定时器(IWDG)或RTC唤醒;

精度较差(±5%或更差),用于不要求高精度但需低功耗的计时;

可连接外部晶体或陶瓷谐振器,频率范围可达16MHz;

精度高于HSI,常用在对时钟精度要求较高的应用,如USB、精确定时器等;

频率为16MHz,无需外部晶体,启动时间较快;

典型精度±3%,适合对时钟精度要求不高但启动速度要求高的场景;

内部高速振荡器(HSI)

外部高速振荡器(HSE)

内部低速振荡器(LSI)

外部低速振荡器(LSE)

时钟配置寄存器

常用的时钟配置寄存器有:

CKDIVR(Clock Divider Register):配置系统时钟分频值,可设置CPU时钟与外设时钟的比例;

PCKENR1/PCKENR2(Peripheral Clock Gating Registers):分别控制APB1与APB2外设的时钟使能,写0可关闭对应外设时钟,降低功耗;

CSSR(Clock Security System Register):时钟安全系统寄存器,可启用HSE故障检测;

SWIMCCR(SWIM Clock Control Register):配置SWIM调试接口时钟;

低功耗模式

STM8S103F3P6支持三种主要低功耗模式:

在实际应用中,可根据系统功耗需求与响应速度要求,在功耗和性能之间进行平衡。例如:在数据采集完成后,系统可以进入Stop模式,等待外部中断唤醒;当需要快速响应时,则选择Wait模式。

与Stop类似,但更彻底地关闭系统,仅保留必需时钟;

唤醒方式比Stop更严格,仅支持外部中断;

CPU和大多数外设时钟关闭,仅保留LSI或LSE时钟以供看门狗和RTC;

唤醒来源包括外部中断、RST中断、IWDG重置等;

适用于对功耗极度敏感的应用,如低功耗待机;

CPU停止工作,但外设时钟继续运行;

退出Wait模式时通过任何外设中断或复位恢复;

适用于需要保持外设工作但暂停CPU处理的场景;

Wait模式

Stop模式

Halt模式

功耗优化策略

关闭不必要外设时钟:通过PCKENR寄存器关闭未使用的外设,以减少时钟源切换造成的功耗;

降低系统时钟频率:如果应用对处理速度要求不高,可将主时钟降至8MHz或4MHz,以降低功耗;

使用内部振荡器:HSI启动快,功耗相对可控;对于精度要求不高的应用,可直接使用HSI,避免外部晶振功耗;

合理进入低功耗模式:在系统空闲时及时调用HALT或STOP指令,使MCU进入低功耗状态;

优化软件算法:减少CPU空循环等待,采用定时器中断或DMA(通过软件模拟)减少CPU负担;

外部硬件电源管理:在单片机控制下,可通过外部稳压器实现动态调节电压,进一步降低功耗;

通过以上时钟与功耗管理策略,可以实现在满足性能需求的前提下最大程度压低系统功耗,为便携式、无线传感节点、工业远程终端等应用场景提供更长的电池寿命与更稳定的运行环境。

七、ADC与模拟子系统

STM8S103F3P6的模拟子系统主要体现在其内部集成的10位ADC。对于需要进行传感器数据采集、模拟信号处理的应用而言,ADC性能与使用方法十分关键。本节将从ADC结构、工作模式、校准方法、典型应用及注意事项等方面进行详细阐述。

ADC硬件结构与资源分配

STM8S103F3P6内置一个10位分辨率ADC模块,具备15路模拟输入通道(编号0–14),包括16个通道:通道0–11对应外部ADC引脚,通道12为内部参考电压(VREFINT),通道13为内部温度传感器,通道14为地(GND),通道15为VDD/2;

ADC模块时钟来源可选HSI/2或HSI/4,内部ADC预分频器可进一步降低ADC时钟频率;

ADC数据寄存器(ADCR)为16位,转换结果以右对齐或左对齐方式存放,转换值范围为0–1023;

ADC工作模式与配置步骤

在使用ADC时,一般遵循如下配置与启动流程:

监测ADC标志寄存器(ADCSR)中的EOC(End of Conversion)标志,当标志置位时,读取ADDR(ADC Data Register)中转换结果;

清除EOC标志,以便下一次采样;

设置ADCR寄存器中的ADON位,开启ADC模块;

对于单次转换模式,写ADCR的ADON位两次,第一次上电激活ADC内部,第二次启动转换;

在连续转换模式或扫描模式下,触发一次ADON即可持续采样;

设置ADC时钟分频,保证ADC时钟在1–14MHz范围内以满足10位转换精度;

配置转换模式(单次模式、连续模式或扫描模式);

配置数据对齐方式(左对齐或右对齐),通常使用右对齐以便于读取数据;

选择要转换的通道编号(在ADCSR寄存器中设置CH[3:0]);

配置相应GPIO引脚为模拟输入模式(即DDR置0、CR1置0、CR2置0),禁止数字输入、上拉或下拉,确保引脚为高阻状态;

在CLK·PCKENR2寄存器上使能ADC模块时钟,写入相应位;

步骤一:时钟使能

步骤二:引脚复用配置

步骤三:ADC寄存器配置

步骤四:启动ADC

步骤五:读取转换结果

ADC校准与精度优化

内部温度传感器可用于检测芯片温度,通过测量通道13获得原始电压值,再根据参考手册公式换算成温度;

为补偿温度对ADC的影响,可在运行时周期性测量内部温度,并根据查表或线性公式进行软件校正;

ADC采样电容较小,输入阻抗过高会导致采样时间延长,增加采样误差;

建议在信号源与ADC输入之间加入低阻抗缓冲(如运放),或在软件中设置足够长的采样延迟;

ADC在初始上电后存在一定偏置电流,通常通过短接ADC输入为固定电压(如GND),测量输出并做软件修正;

对多路输入进行交替采样时,不同通道因采样电容充电时间不同导致精度差异,可通过对比测试或多次采样取平均的方法提高精度;

偏置电流与通道一致性校准

采样时间与输入阻抗

温度漂移与内部温度传感器

典型应用案例

压阻式或电容式压力传感器输出电压经前端放大后接入ADC,实现压力数据采集;

通过多次采样去噪,并根据温度补偿曲线提高测量精度;

光敏电阻或光电二极管经运放电压放大后接入ADC通道,计算光照强度;

可搭配PWM控制恒流源实现自动增益调整,以适应不同光照条件;

通过PT100、热敏电阻(NTC)或热电偶等传感器接入ADC通道,采样后进行线性或非线性校正;

对于需要高精度测温的场景,可采用14位或16位外置ADC,并使用SPI或I²C与STM8S通讯;

利用ADC采样电池分压后的电压值,通过软件计算电池剩余电量;

由于电池内阻和ADC输入阻抗的影响,建议在电池电压分压网络后面加运放跟随器;

电池电量监测

温度传感器接口

光照强度测量

压力传感器应用

ADC使用注意事项

避免共地干扰:模拟地与数字地应分区域走线,在系统接地端汇合;

滤波与抗干扰:在ADC输入端添加RC滤波电路或L-C滤波,以抑制高频噪声;

正确选择采样时钟:ADC时钟过快会降低采样精度,过慢则降低采样速度;根据系统需求在1–14MHz范围内选择合适分频;

连续采样与通道切换延时:当切换不同通道时,需等待足够的采样时间以让采样电容充电到稳定值;

温度与电压漂移补偿:在环境温度或供电电压波动剧烈时,可定期校准ADC或利用内部参考进行补偿;

通过对STM8S103F3P6 ADC模块的深度解析,可以发现虽然其仅为10位分辨率,但在适当架构和电路设计下,完全可以满足大多数中低端传感应用的需求。同时,通过软件校准与多种滤波手段,可以在一定程度上提高测量精度与稳定性。

八、定时器与PWM应用

STM8S103F3P6集成了四个定时器(TIM1、TIM2、TIM3和TIM4),能够满足从电机驱动、PWM信号生成到简单延时与事件捕获等多种需求。本节将分别介绍各定时器特点、寄存器配置、典型应用与注意事项。

TIM1(高级定时器)

使能TIM1时钟:CLK_PCKENR1 |= (1 << 7);

设置预分频:TIM1_PSCR = pre_div_value;

设置自动重装载:TIM1_ARRH = (period >> 8) & 0xFF; TIM1_ARRL = period & 0xFF;

配置PWM通道模式:TIM1_CCMR1 = 0x60; // PWM模式1,输出比较预装载使能

设置占空比:TIM1_CCR1H = (duty >> 8) & 0xFF; TIM1_CCR1L = duty & 0xFF;

使能输出:TIM1_CCER1 |= (1 << 0);

使能死区与刹车:TIM1_BDTR = dead_time_config;

使能计数器:TIM1_CR1 |= (1 << 0);

电机驱动:控制三相BLDC或无刷直流电机,利用互补输出与死区时间保证MOSFET安全切换;

DC-DC变换器:在同步整流应用场景中,通过双通道或三通道PWM实现多相变换;

功率逆变器:生成高频PWM波形,驱动功率器件输出对应频率与幅值的交流电;

TIM1_CR1/CR2:控制寄存器,用于设置计数模式、预分频、自动重装载预装载使能、死区插入、刹车功能等;

TIM1_CCMR1/CCMR2/CCMR3:捕获/比较模式寄存器,配置通道输出模式(PWM模式1/2、OC模式等);

TIM1_CCER1/CCER2:捕获/比较使能寄存器,用于使能或禁止通道输出、配置输出极性;

TIM1_BDTR:刹车与死区时间寄存器,用于设置死区时间长度、刹车输入极性、刹车锁定等;

TIM1_PSCR:预分频寄存器,用于分频系统时钟;

TIM1_ARR:自动重装载寄存器,用于设定PWM周期;

16位可编程计数器,支持上升沿或下降沿计数,带预分频器和自动重装载寄存器;

具备三组互补输出(CH1/CH1N、CH2/CH2N、CH3/CH3N),支持死区时间插入;

独立刹车功能,可通过外部信号立即关闭PWM输出,适合安全停机需求;

支持死区生成(Dead-Time Generator),确保功率管切换时不会出现短路;

包含刹车输入(BKIN)、使能输出(MOE)等控制信号,方便对上层电机驱动逻辑进行硬件保护;

基本特性

主要寄存器

典型应用

配置示例(概念性描述)

TIM2与TIM3(通用定时器)

使能TIM2时钟:CLK_PCKENR1 |= (1 << 5);

设置预分频:TIM2_PSCR = pre_div_value;

设置自动重装载:TIM2_ARRH = (period >> 8) & 0xFF; TIM2_ARRL = period & 0xFF;

配置通道1 PWM模式:TIM2_CCMR1 = 0x68; // PWM模式1,输出比较预装载使能

设置占空比:TIM2_CCR1H = (duty >> 8) & 0xFF; TIM2_CCR1L = duty & 0xFF;

使能通道输出:TIM2_CCER1 |= (1 << 0);

使能计数器:TIM2_CR1 |= (1 << 0);

PWM信号生成:通过TIM2或TIM3输出PWM波,可用于LED调光、直流电机调速等;

输入测量:利用输入捕获功能测量外部信号频率、占空比、周期等;

定时与周期性中断:在TIM2或TIM3溢出时产生中断,用于定时任务调度或周期性处理;

TIMx_CR1/CR2:控制寄存器,设置计数模式、预分频、中心对齐使能等;

TIMx_PSCR:预分频寄存器;

TIMx_ARR:自动重装载寄存器;

TIMx_CCMR1/CCMR2:通道配置寄存器,用于设置通道为输出模式、输入捕获模式或PWM模式;

TIMx_CCER1/CCER2:通道使能寄存器,用于配置输出或捕获极性;

TIMx_CCRx:通道捕获/比较寄存器,用于设置占空比或获取捕获值;

均为16位预分频计数器,具备四路通道(CH1、CH2、CH3、CH4)可进行输入捕获、输出比较和PWM输出;

支持单脉冲模式、中心对齐模式、边缘对齐模式等多种计数模式;

具有DMA请求功能,可在数据传输密集应用中配合DMA降低CPU开销(STM8S103F3P6无硬件DMA,但可模拟类似功能);

基本特性

主要寄存器

典型应用

配置示例(概念性描述)

TIM4(基本定时器)

使能TIM4时钟:CLK_PCKENR1 |= (1 << 3);

设置预分频:TIM4_PSCR = prescaler_value;

设置自动重装载:TIM4_ARR = auto_reload_value;

使能溢出中断:TIM4_IER |= (1 << 0);

使能计数器:TIM4_CR1 |= (1 << 0);

系统节拍:通过固定时间间隔产生中断,用于操作系统或任务调度;

看门狗模拟:在没有IWDG或WWDG的场景下,通过TIM4定时检测系统是否卡死;

低速PWM:若不需要高精度PWM,可利用TIM4在GPIO中断中手动切换引脚状态;

TIM4_CR1:控制寄存器,设置预分频、计数模式、溢出中断使能等;

TIM4_PSCR:预分频寄存器,可将系统时钟分频到最低频率;

TIM4_ARR:自动重装载寄存器,用于设定溢出周期;

TIM4_SR1:状态寄存器,用于检测溢出标志;

8位计数器,可生成溢出中断;

无输出比较功能,仅支持基本的时间计数;

适合低资源占用的延时或周期性中断需求;

基本特性

主要寄存器

典型应用

配置示例(概念性描述)

定时器应用注意事项

时钟源稳定性:在需要高精度计时的场景下,应使用外部晶振(HSE)并关闭HSI,以减少频率漂移;

中断优先级配置:定时器中断可能与其他外设中断竞争,需合理设置优先级并避免在中断中执行过长代码;

死区与刹车实现:在高功率开关电源或电机驱动中,必须根据功率管参数准确设置死区时间;

避免中断嵌套崩溃:在多定时器同时工作时,需关注中断嵌套与堆栈深度,避免因中断优先级冲突导致系统崩溃;

PWM输出滤波:若外部负载对电压变化敏感,可在PWM输出端加LC滤波器以降低纹波;

通过对STM8S103F3P6各定时器的功能与应用进行剖析,开发者可以根据项目需求灵活运用不同定时器完成多种任务,从简单的延时到复杂的电机控制或功率转换,实现功能丰富且性能可靠的设计方案。

九、串行通信接口

STM8S103F3P6内置多种串行通信接口,包括USART、SPI和I²C,为嵌入式系统与外部设备之间的数据交换提供了丰富选择。本节将详细介绍各接口的功能特性、配置要点及典型使用场景。

USART(通用同步/异步收发器)

串口调试:通过UART与PC终端进行调试信息输出或命令交互;

模块通信:与GPS、蓝牙、Wi-Fi模块等通过USART接口进行数据交换;

RS-485总线:通过外部收发器将UART信号转换为差分信号,实现远距离通信;

LIN总线节点:配置为LIN主机或从机,实现车辆低速通信;

步骤一:时钟使能

步骤二:GPIO复用

步骤三:波特率设置

步骤四:使能USART

步骤五:中断/DMA配置(可选)

在CLK_PCKENR2寄存器上使能USART时钟;

将相应引脚配置为复用推挽输出(TX)和输入浮空或上拉输入(RX);

根据系统时钟频率,通过USART_BRR1和USART_BRR2寄存器配置波特率生成;

设置USART_CR2寄存器的TEN(发送使能)和REN(接收使能)位;

通过USART_CR2使能TXEIE、RXNEIE中断;配置NVIC或中断向量;

如果使用DMA(模拟),可在TX中断中手动触发数据发送;

USART_CR1/CR2/CR3:控制寄存器,用于配置传输模式、波特率、校验、CPol、CPha等;

USART_BRR1/BRR2:波特率寄存器,配置通信波特率;

USART_SR:状态寄存器,包含TXE(发送数据寄存器空)标志、RXNE(接收寄存器非空)标志、ORE(溢出)等;

USART_DR:数据寄存器,用于读写发送/接收数据;

USART_GTR:Guard time寄存器,用于LIN协议中定义保护时间;

USART_PSCR:Prescaler寄存器,用于更精确的波特率分频;

支持异步UART模式与同步模式;

支持LIN 1.x协议,具备自动波特率检测功能;

支持多主机/多从机通信模式,可实现多机共享单条信号线;

波特率范围:300 bps至115200 bps,最高可配置到整型预分频;

数据帧格式:1起始位、5–9位数据位(可选)、1位或2位停止位、可选校验位(奇偶校验);

功能特性

主要寄存器

配置流程

典型应用场景

SPI(串行外设接口)

显示屏驱动:与SPI接口OLED、TFT、LCD等显示模块进行通信,传输显示数据;

SD卡读写:通过SPI模式与SD卡进行块读写操作;

外部ADC/DAC:与SPI外设ADC或DAC芯片进行高速数据采集或输出模拟量;

无线模块:与NRF24L01、W5500等无线通信模块进行收发数据;

步骤一:时钟使能

步骤二:GPIO配置

步骤三:控制寄存器设置

步骤四:使能SPI

步骤五:中断/轮询模式

在CLK_PCKENR2寄存器使能SPI时钟;

将MISO引脚配置为浮空输入,将MOSI和SCK引脚配置为复用推挽输出,引入NSS作为输入(从模式)或输出(主模式);

在SPI_CR1中选择主/从模式,配置CPOL/CPHA;在SPI_CR2中选择数据帧长度;

在SPI_CR1中置SPE(使能SPI)位;

轮询方式:在发送时检查TXE标志,在接收时检查RXNE标志;

中断方式:使能RXNEIE或TXEIE,在中断服务程序中进行数据收发;

SPI_CR1:控制寄存器1,配置SPI主/从模式、CPOL、CPHA、LSB/MSB优先、内部软件管理片选等;

SPI_CR2:控制寄存器2,配置数据帧格式(8位/16位)、NSS O/P或I/P模式等;

SPI_ICR:中断控制寄存器,配置RXNEIE(接收非空中断)、TXEIE(发送空中断)等;

SPI_SR:状态寄存器,包含BSY(忙标志)、OVR(溢出)、MODF(模式故障)等;

SPI_DR:数据寄存器,用于读写数据;

支持全双工通信,最高通信速率可达fMASTER/4(在16MHz时钟下可达4MHz);

支持主模式与从模式切换;

可配置数据帧格式(8位或16位)、时钟相位(CPHA)、时钟极性(CPOL);

硬件支持NSS(片选)信号管理,或采用软件控制NSS;

功能特性

主要寄存器

配置流程

典型应用场景

I²C(两线串行总线接口)

EEPROM读写:与I²C接口EEPROM(如24Cxx系列)进行数据存储与读取;

温度/湿度传感器:与DHT12、Si7021等I²C传感器采集环境数据;

RTC芯片:与外部RTC(如DS1307、PCF8563)同步时间信息;

显示模块:与I²C接口OLED显示屏(如SSD1306)进行图形或文字显示;

步骤一:时钟使能

步骤二:GPIO配置

步骤三:模式与速率配置

步骤四:使能I²C

步骤五:数据传输

在CLK_PCKENR2寄存器使能I²C时钟;

将SCL、SDA引脚配置为开漏推挽输出,外部接10kΩ左右上拉电阻;

写入FREQR寄存器:I2C->FREQR = 系统时钟/MHz;;

写入CCRL和CCRH寄存器:根据速率和模式(标准/快速)计算CCR值;

设置I2C->CR1的PE位;

发送START:设置CR2的START位;

等待START标志(SR1的SB置位),写入SLAVE地址和读/写位到DR;

等待地址应答(SR1的ADDR置位),读取SR2以清除ADDR;

在发送数据阶段,检查TXE(DR空)标志后向DR写入数据;在接收阶段,等待RXNE(接收非空)后读取DR;

发送STOP:在最后一个字节传输完后,置CR2的STOP位;

I2C_CR1:控制寄存器,用于使能I²C、生成START、STOP条件等;

I2C_CR2:控制寄存器2,配置位定时器、DMA请求等;

I2C_FREQR:时钟控制寄存器,设置I²C时钟频率;

I2C_OARL/OARH:本地地址寄存器,配置设备的7位(或10位)地址;

I2C_SR1/SR2:状态寄存器,用于检测START/STOP、中断、总线错误等状态;

I2C_DR:数据寄存器,用于发送/接收数据;

I2C_CCRL/CCRH:配置寄存器,用于设置传输速率与模式;

支持标准模式(100kHz)与快速模式(400kHz);

支持多主机模式与多从机模式;

硬件自动生成START、STOP条件以及ACK/NAK响应;

支持7位或10位地址格式(以软件配置为准);

功能特性

主要寄存器

配置流程

典型应用场景

通信接口应用注意事项

收发冲突:在全双工或半双工通信中,应合理设置时序,避免TX与RX冲突,特别是在多主机I²C或多种接口同时工作的场景;

缓冲区与中断优先级:在高速通信中,若读取或写入数据不及时,可能导致溢出错误。可通过设定适当中断优先级或使用循环缓冲来缓解;

错误检测与重传:对于UART通信,可通过在协议层添加CRC校验;对于I²C,可检查NACK信号并在收到NACK时重新发送;

电平匹配与隔离:如果外部模块与STM8S103F3P6工作电压不同,需要使用电平转换器或隔离电路;

总线带载能力:I²C总线上的设备越多,电容负载越大,可能导致信号变形,需对SCL与SDA线进行适当RC或LC滤波;

通过以上对STM8S103F3P6串行通信接口的详细讲解,开发者可以根据外设特性选择合适的接口,设计稳定的总线拓扑,并通过正确的软件流程实现高效、可靠的数据传输。

十、I/O与GPIO应用

STM8S103F3P6具备多个通用I/O端口(PORTA、PORTB、PORTC、PORTD、PORTE),每个端口包含8个引脚。GPIO在嵌入式系统中经常用于与外部设备进行状态控制、按键、LED指示灯、继电器驱动、传感器读写等。本节将围绕引脚配置、I/O寄存器、外部中断、模拟输入与数字输出应用展开。

GPIO引脚配置

DDR寄存器:决定引脚为输入(0)或输出(1);

CR1寄存器:用于选择输入模式(浮空或上拉)和输出类型(推挽或开漏);

CR2寄存器:用于配置输出速度(高速/低速)和输入中断使能;

在STM8中,每个GPIO引脚均可通过DDR(Direction Register)、CR1(Control Register 1)和CR2(Control Register 2)三个寄存器组来配置其模式:

配置示例:将PA3配置为推挽输出,低速模式:

c复制编辑PA_DDR |= (1 << 3); // 输出模式PA_CR1 |= (1 << 3); // 推挽输出PA_CR2 &= ~(1 << 3); // 低速输出

将PC4配置为浮空输入,启用下降沿中断:

c复制编辑PC_DDR &= ~(1 << 4); // 输入模式PC_CR1 &= ~(1 << 4); // 浮空输入PC_CR2 |= (1 << 4); // 上升/下降中断使能EXTI_CR1 |= (1 << 4); // 配置为下降沿触发

数字输入与输出

浮空输入:不使用内部上下拉,适合高阻抗输出设备;

上拉输入:内部置约30–50kΩ上拉电阻,适合按键输入且无需外部上拉;

电压容限:输入引脚电压应在VSS–0.3V到VDD+0.3V之间,否则可能损坏引脚;

中断触发:可配置为上升沿、下降沿或双沿触发,通过EXTI模块实现外部事件响应;

推挽输出:可驱动高/低电平,适合连接LED、继电器驱动器等;

开漏输出:在输出低电平时导通,输出高电平时呈高阻,需外部上拉电阻,多用于I²C信号、总线通信等;

输出电流限制:单引脚最大驱动电流为20mA,建议工作电流不超过10mA;

输出切换延时:在高速切换应用(如SPI模拟或LED调频调光)时,需留意输出切换时间;

数字输出

数字输入

外部中断(EXTI)

按键扫描:将多个按键输入引脚配置为外部中断,一旦按键按下就中断响应,实现低功耗唤醒;

频率脉冲计数:外部脉冲信号输入引脚(如PC3)配置为输入捕获或外部中断,统计脉冲次数以计算频率;

外部事件检测:光电开关、霍尔传感器等检测到状态变化,通过中断快速响应;

当引脚输入状态满足触发条件(如下降沿),对应EXTI标志被置位;

CPU检测到中断请求后,若I位(全局中断使能)为1,则跳转到相应中断向量;

在中断服务程序中,需清除EXTI标志,否则会重复触发;

EXTI_CR1:配置PC、PD、PE组外部中断触发模式;

EXTI_CR2:配置PA、PB端口的中断触发模式;

每个引脚可单独设置为上升沿、下降沿或双沿触发;

STM8S103F3P6支持多路外部中断,每个GPIO引脚均可配置为中断源。中断触发由EXTI_CR寄存器组控制:

中断响应流程:

典型应用:

模拟输入与数字输出结合应用

模拟输入:光敏电阻经分压后接入ADC通道,测量环境光照强度;

PWM输出:使用TIM2生成PWM信号,通过GPIO输出连接到LED驱动模块,实现自动亮度调节;

在光照强度降低到指定阈值时,自动增加LED亮度,反之自动降低;

模拟输入:将温度传感器经运放后接入ADC通道,例如PA0;周期性读取ADC值,计算温度;

数字输出:根据测得温度与阈值比较结果,控制GPIO输出驱动MOS管或继电器,以打开或关闭风扇;

通过定时器中断(如TIM4定时1s)周期性采集与判断,并在ADC采样过程中关闭不必要的外设,提高功耗性能;

在需要同时进行模拟量采集与数字控制的场景,如温度测量与风扇控制,可采用以下流程:

另一典型场景为灯光调节:

I/O应用注意事项

防抖处理:对于机械按键、低速开关输入,应在硬件或软件层面加入消抖措施,以避免短时干扰造成误触发;

上拉下拉选择:当外部设备本身带上下拉时,应将GPIO配置为浮空输入,以避免多重上拉/下拉导致供电浪费;

电流平衡:在多个输出同时驱动高电流负载时,需要考虑VDD与VSS电源走线宽度,并在供电线上放置电容滤波,避免电压跌落;

高频干扰抑制:对于受干扰影响较大的环境,如工业电机驱动,应在GPIO输入端加RC滤波或光耦隔离;

关断模式:在MCU进入Stop模式时,所有I/O引脚默认浮空,可能导致外部器件误动作,需要在必要时配置为上拉或下拉;

综上所述,通过对STM8S103F3P6 GPIO与I/O外设的深入剖析,开发者可以在设计之初明确各引脚的功能与电气特性,合理进行引脚复用与外设配置,以实现可靠、稳定、灵活的I/O控制系统。

十一、看门狗与安全功能

在嵌入式系统中,为了保障系统在异常情况(如软件死循环、总线挂起、外部电压干扰)下能够及时复位恢复,STM8S103F3P6集成了多种看门狗(Watchdog)与安全防护功能。本节将重点介绍IWDG(独立看门狗)、WWDG(窗口看门狗)及相关安全机制。

独立看门狗(IWDG)

系统可靠性保护:在主循环或定时器中断中调用IWDG重载,若程序卡死或进入未知区域,则IWDG超时复位;

多任务调度检测:在RTOS环境中,可在各任务或监控任务中完成IWDG重载,若有任务未及时响应则触发复位;

抗干扰设计:结合硬件电源检测,当CPU进入死循环或被干扰锁死时,IWDG可确保系统重新启动;

启动IWDG:连续写入0xCCCC到IWDG_KR寄存器;

预分频设置:在IWDG_SR的PVU标志清零后,写入IWDG_PR;

重载计数:在IWDG_RVU标志清零后,写入IWDG_RLR;

定期重载:在主循环或关键代码段中定期写0xAAAA到IWDG_KR,以防止超时复位;

IWDG_KR(关键寄存器):写入0xCCCC以启动看门狗,引导写入;写入0xAAAA可重载计数器;

IWDG_PR(预分频寄存器):设置IWDG时钟预分频,可选分频系数为4、8、16、32、64、128、256;

IWDG_RLR(重载寄存器):设置计数器重装载值(0–255);

IWDG_SR(状态寄存器):指示PR和RLR是否完成更新;

基于LSI内部振荡器(约38kHz),运行独立于系统时钟;

在IWDG启动后无法关闭,除非系统复位;

支持8位预分频,定时范围可通过PR寄存器设置(从1ms至几秒级别);

一旦IWDG计数超时,会触发系统复位;

功能特性

寄存器与配置

使用步骤

典型应用

窗口看门狗(WWDG)

关键时序检测:在要求程序在特定时间窗口内执行代码的场景,通过WWDG保证程序实时性;

系统安全防护:防止恶意攻击或意外操作导致程序过早或过晚重载WWDG,触发复位并进行重启;

启用WWDG:设置WWDG_CR寄存器的WDGA位;

设置预分频:在WWDG_SR的EWU标志清零后,配置WWDG_CR寄存器中的T[6:0]和WDGA;

设置窗口值:在WWDG_SR的EWU标志清零后,写入WWDG_WR寄存器;

计数重载:在窗口期内写入合法计数值,否则触发复位;

WWDG_CR(控制寄存器):用于使能WWDG、设置预分频、设置当前计数值;

WWDG_WR(窗口寄存器):设置窗口值,在该值之后才能进行计数重装载;

WWDG_SR(状态寄存器):指示更新窗口是否可写;

基于高速时钟(HSI/128)或外部时钟(HSE),具有窗口检测特性;

在倒计时过程中仅在预设窗口期内更新计数器才有效,提前或滞后更新均触发复位;

支持7位预分频,时间窗可通过T[6:0]设置;

功能特性

寄存器与配置

使用步骤

典型应用

低电压检测(PVD)

电池供电系统:当电池电压过低时,通过PVD中断提示用户及时更换电池或切换电源模式;

UPS不间断系统:在市电断电情况下,PVD可检测市电电源转换时的瞬态,确保切换过程安全;

设置PVD阈值:在PVD_CR1寄存器中配置相应电平;

使能PVD中断:配置中断向量和优先级;

编写PVD中断服务程序:检测PVD_SR标志,以正确处理电压低警告或复位;

PVD_CR1:配置PVD阈值电平,可选择1.8V、2.2V、2.4V、2.6V、2.8V、3.0V、3.2V、3.4V;

PVD_SR:状态寄存器,指示PVD状态;

IE(Interrupt Enable):使能PVD中断;

PVD(Programmable Voltage Detector)可监测VDD电压是否低于设定阈值;

当VDD低于阈值时,触发PVD中断或复位,保护系统在不稳定电源下运行;

功能特性

寄存器与配置

使用步骤

典型应用

安全与保护功能综合应用

IWDG作为系统死循环保护;

WWDG用于确保关键任务在预设窗口内完成;

在工业现场或关键安全系统中,可将IWDG与WWDG结合使用:

采用PVD检测电源异常,并配合软件逻辑保护电机、电源等外部设备,避免因电压瞬变损坏硬件;

结合定时器与外部中断,在IWDG与WWDG复位触发后记录故障码,并写入EEPROM或Flash,以便后续故障分析;

通过对STM8S103F3P6看门狗与安全功能的详细讲解,开发者可以在设计中构建多层安全保障,确保系统在软件或硬件故障时能及时响应并重启,从而提高系统的稳定性和可靠性。

十二、开发工具与软件生态

硬件性能再强大,也离不开完善的软件开发环境和调试工具的支撑。STM8S103F3P6作为ST的主流8位系列产品,享有丰富的开发生态系统,包括IDE、编译器、调试器以及配套的中间件与示例代码。本节将介绍常用的开发工具链、软件库及调试方法,帮助开发者快速上手。

集成开发环境(IDE)

IAR提供的专业商业IDE,支持STM8架构;

拥有非常优秀的编译器优化与静态分析工具;

适合对代码尺寸与性能要求极高的项目;

开源免费的C编译器,支持STM8架构;

可通过命令行编译,并配合第三方IDE(如Eclipse)进行项目管理;

虽然体积小巧免费,但在代码优化与库支持方面相对不如Cosmic;

Cosmic提供的商业级C编译器,针对STM8系列进行优化;

支持C99标准,代码优化较好,生成代码体积小;

与STVD集成良好,可在STVD中选择Cosmic作为编译工具链;

ST官方推出的免费IDE,支持STM8 MCU开发;

集成Keil、Cosmic、RnD等多种C编译器;

界面类似Visual Studio,支持项目管理、代码编辑、编译、下载及仿真调试;

内置示例项目和代码示例,便于初学者快速了解外设驱动;

STVD(ST Visual Develop)

Cosmic C Compiler

SDCC(Small Device C Compiler)

IAR Embedded Workbench for STM8

调试与编程工具

Raisonance、SEGGER等厂商提供的仿真器也支持STM8系列;

SEGGER J-Link支持SWIM仿真,并提供高性能调试特性,但价格相对较高;

ST官方独立编程软件,无需IDE即可对STM8芯片进行Flash/EEPROM烧写;

支持ST提供的STVP脚本,通过脚本可实现批量编程或自动化烧录;

ST官方仿真器,支持SWIM(Single Wire Interface Module)接口,用于STM8调试与编程;

通过USB与PC连接,兼容STVD、IAR、Cosmic等IDE;

ST-Link/V2-ISOL增加了电气隔离功能,适用于工业环境;

ST-Link/V2、ST-Link/V2-ISOL

STVP(ST Visual Programmer)

第三方仿真器/调试器

标准外设库(SPL)与固件包

ST官方网站提供了大量应用手册与技术文档,如AN2733(STM8定时器应用)、AN3469(ADC应用)等;

社区、论坛中也有丰富的开源示例,涵盖无线通信、图形界面、协议栈等;

ST近年推出了Cube系列硬件抽象层(HAL),并将其扩展至STM8平台;

提供与STM32类似的HAL API,使用风格统一,方便跨平台迁移;

包含RTOS移植范例,可基于FreeRTOS等开源RTOS进行多任务开发;

ST官方提供的外设库,包含ADC、USART、SPI、I²C、GPIO、TIM等模块驱动代码;

代码封装良好,调用方便,可大幅缩短开发周期;

同时提供了大量示例工程,覆盖板级支持包(BSP)和不同外设功能演示;

ST标准外设库(STM8S SPL)

STM8固件库(STM8 Cube HAL 等)

示例项目与应用笔记

常用开发流程

项目创建

外设驱动调用

代码编写与调试

上电/上电复位测试

仿真与性能分析

通过STVD的实时监测功能或IAR的Tune功能进行代码性能评估;

优化关键算法,提高执行效率,降低功耗;

完成基础调试后,断开调试器,使用实际电源给MCU上电;

验证程序在不同电压、不同温度下的稳定性;

在中断向量表(stm8s_it.c)中添加相应中断服务函数;

通过ST-Link将程序烧录到STM8S103F3P6芯片;

使用SWIM调试,设置断点、观察寄存器和变量值;

将STM8S SPL拷贝到项目目录,在项目中引用外设驱动代码;

在 main.c 中调用 CLK_Config(), GPIO_Config(), TIM_Config(), ADC_Config() 等函数;

在STVD中新建STM8项目,选择器件型号STM8S103F3P6;

选择编译工具链(Cosmic/SDCC/IAR);

通过上述对STM8S103F3P6开发工具链与软件生态的剖析,可以发现ST为STM8系列提供了完备的支持,从IDE、编译器、调试器到外设库、应用示例,都极大地降低了开发门槛。结合社区资源与开源项目,开发者可以快速搭建原型,并在此基础上进行功能扩展与优化。

十三、典型应用案例与设计指南

在理解了STM8S103F3P6的硬件架构、外设功能、开发工具链后,将其应用于实际项目设计中需综合考虑系统需求、硬件布局、软件实现和系统可靠性。以下通过若干典型应用案例,结合设计要点与优化建议,为读者提供实用参考。

家电面板控制(如洗衣机、微波炉)

任务调度:采用循环+中断方式,主循环负责人机交互逻辑,中断处理按键扫描、定时采样等;

按键消抖:利用定时器中断为每个有效按键按下时间计时,只有持续按下达到设定时间(如20ms)才判定为有效按键;

状态机设计:PLC式状态机管理各功能模块,如“待机”、“运行”、“暂停”、“故障”,便于功能扩展;

温度控制算法:对采集的ADC值进行滤波与温度换算,结合PID算法控制加热元件;

上电自检与安全保护:利用IWDG和PVD保护系统,如果传感器异常或通信超时,进入安全停机状态,并通过LCD显示错误代码;

按键扫描矩阵:通过GPIO引脚实现矩阵式扫描,减少I/O占用,并通过外部中断实现快速响应;

显示驱动:根据显示屏类型选择合适通信接口,SPI或并行接口;配合TPM(触控面板)时,需优化I/O复用以节省管脚;

传感器接口:如温度传感器(NTC)接入ADC通道,光照传感器接入ADC通道;在信号线加滤波与缓冲;

输出驱动:DC电机驱动可通过TIM1输出PWM控制,通过MOSFET驱动继电器或电机;

电源与滤波:家电系统通常干扰较大,需在VDD输入增加滤波电容,并在关键电路(如ADC输入)加颗粒滤波;

驱动按键、旋钮、指示灯、LCD背光;

控制显示屏(如7段数码管或小型LCD);

采集温度、湿度、转速等传感器数据;

控制电机、继电器等输出;

保证基本人机交互与安全保护;

功能需求

硬件设计要点

软件实现要点

工业传感器数据采集与无线传输

ADC多通道扫描:使用DMA(软件模拟)方式循环采样,每次采样后计算平均值,减少单次异常值影响;

数据滤波与校准:对原始ADC数据进行滑动平均或卡尔曼滤波,并根据厂商数据手册进行线性/非线性校准;

无线传输协议:定义简洁可靠的包头、校验码、ACK机制;遇到传输失败时进行重传,记录重传次数;

低功耗策略:在非采集与非传输阶段进入Stop模式,利用定时器或外部中断唤醒;仅在数据发送时短暂切换到Wait模式;

故障检测与重置:利用IWDG保护长时间死机,PVD检测电压异常,进入安全模式并通过LED或其他方式报警;

多路ADC输入:利用ADC扫描模式连续读取多个通道,并在每个通道前加入RC低通滤波;

数字传感器接口:I²C接口连接温湿度传感器,SPI接口连接数字压力传感器;需注意时序与地址冲突;

无线模块通信:NRF24L01通过SPI接口连接STM8,引脚复用配置SS、MOSI、MISO、SCK为SPI;

电源管理:采用DC-DC降压模块或LDO稳压,输出3.3V给传感器和无线模块,并通过FET或MOS关闭无线模块电源降低功耗;

PCB布局:数据采集通道尽量远离无线天线,减少射频干扰;ADC地与数字地分区,汇合于转向点;

多路模拟量采集(压力、温度、湿度、流量等);

通过I²C或SPI与数字传感器通信;

数据存储与预处理(降噪、滤波);

通过USART或SPI与无线模块(如NRF24L01、ESP8266)进行数据传输;

低功耗设计,实现现场长时间稳定运行;

功能需求

硬件设计要点

软件实现要点

智能仪表及数据记录仪

精度与稳定性:对内置ADC进行温度补偿与校准,对外置ADC则根据芯片手册进行I²C/SPI时序优化;

文件系统:若使用SD卡,可集成FatFs或TinyFS文件系统,通过SPI读写SD卡扇区;

图形显示驱动:移植ST官方LCD驱动库或Thin-Film Transistor(TFT)驱动库,实现菜单、图表等显示;

数据保存与读取:通过实时戳(RTC或外部时间源)记录数据时间,遇到断电或重启时从EEPROM读取最后写入位置;

远程传输协议:GPRS模块可使用MQTT或HTTP协议上传数据到服务器,Bluetooth可使用串口服务与移动终端APP通信;

高精度ADC:虽然STM8内置10位ADC,但对于高精度测量需求可选用外置16位ADC,STM8通过SPI或I²C读取;

信号隔离与隔离放大:电流采样可采用分流电阻+隔离放大器,保证对MCU的电气安全;

LCD与按键背光:LCD通过SPI或并口驱动,背光可通过PWM输出控制亮度;按键矩阵需加消抖电容并采取软件消抖;

数据存储:选择I²C EEPROM保存短期数据记录,SD卡通过SPI接口实现大容量数据保存;

无线模块:GPRS模块通过USART接口连接STM8,模块独立电源并配备电平转换器;Bluetooth模块(如HC-05)可采用软UART或硬UART连接;

精确测量电压、电流、功率等参数;

多路模拟量采样,精度要求较高;

LCD界面显示、按键操作、背光控制;

数据存储于EEPROM或SD卡;

可选配GPRS或Bluetooth模块,实现远程数据上传;

功能需求

硬件设计要点

软件实现要点

玩具与智能家居控制

红外解码算法:通过定时器捕获脉宽,解析NEC、RC5、RC6等常见协议;

PWM色彩渐变:在TIM2或TIM3的PWM通道上设置不同占空比,并通过定时器中断实现渐变效果;

蓝牙通信:通过UART中断接收AT命令或数据协议,并解析后执行对应动作;

按键与菜单:使用有限状态机完成多级菜单显示与按键处理;

系统低功耗:进入待机模式时关闭不必要的外设,将外部中断(如按键中断、蓝牙唤醒)作为唤醒源;

RGB LED驱动:通过PWM通道生成不同频率与占空比的PWM信号,分别控制R、G、B脚,实现色彩混合;

红外接收:在GPIO配置为外部中断模式,检测红外接收模块输出脉宽,进行解析;

蜂鸣器与振动马达控制:蜂鸣器可直接通过GPIO输出方波驱动,振动马达则通过MOSFET或BJT做驱动;

蓝牙模块集成:通过USART连接HC-05/HC-06,配合UART中断处理;

供电管理:通常为3.3V或5V供电,使用稳压芯片提供稳定电压,电池供电需加入降压电源并监测电量;

驱动RGB LED、蜂鸣器、振动马达等装置;

通过红外遥控、RF射频、蓝牙等方式接收指令;

集成人机界面(按键、指示灯、OLED显示);

低成本、易于生产与维护;

功能需求

硬件设计要点

软件实现要点

通过以上典型应用案例可以看出,STM8S103F3P6在家电控制、工业采集、智能仪表和智能家居等领域具备广泛的适用性。合理利用其丰富的外设资源与低功耗特性,结合可靠的硬件设计与优化的软件架构,能够快速搭建满足市场需求的产品。

十四、电源管理与供电设计

电源设计直接影响STM8S103F3P6系统的可靠性、性能与功耗表现。本节将介绍常见的电源设计方案、稳压芯片选型、滤波与去耦,以及电压监测与保护措施。

电源方案选型

优点:效率高、热损耗低,适合大电流或电池供电;

缺点:电路复杂,需要更多外围元件(电感、肖特基整流二极管、电容等),EMI需注意;

典型选择:MP2307(3A同步升降压)、LM2596(3A降压)、TPS62125(高效降压)等;

优点:输出干净、纹波小、设计简单;

缺点:效率较低,尤其在输入与输出电压差大时转换效率低;在大电流应用中会产生较多热量;

典型选择:AMS1117-5.0(5V转5V)、LD1117系列(5V转3.3V)、MCP1700(高精度低压差)等;

线性稳压(LDO)

开关电源(DC-DC)

稳压与滤波设计

同步降压芯片通常带有内置开关,需要在输出端增加LC滤波器(电感+陶瓷电容)以减小纹波和噪声;

对于敏感模拟电路(如ADC),在模拟地附近再加一个小容量的陶瓷电容进行局部滤波;

LDO稳压器后面需放置至少一个0.1μF的陶瓷电容与一个10μF陶瓷/钽电容并联,以确保稳定;

某些高精度LDO对输出电容ESR(等效串联电阻)要求严格,需参考其数据手册选择合适电容;

对于易受干扰的电源输入(如直流母线、工业电源),需先通过LC滤波或Pi滤波网络抑制高频噪声;

串联共模电感(EMI抑制环)与大容量电解电容可有效降低导轨噪声;

输入滤波

LDO输出滤波

DC-DC输出滤波

电压监测与复位电路

如需更精准的电压检测,可在VDD与ADC之间加分压电路,通过ADC采样VDD并对软件进行判断;

或者选择集成电压检测与看门狗功能的PMIC(如AXP2101、bq24195)对供电进行管理;

STM8内置上电复位,当VDD升至POR阈值(典型2.7V)时产生复位信号,确保程序在电压稳定后才开始执行;

通过PVD模块可实现对VDD电压的实时监测,当VDD低于阈值(如2.8V、3.0V)时触发中断或复位;

PVD(片内电压监测)

上电复位(POR/PDR)

外部电压监测

电源保护与抗干扰措施

对于LDO或DC-DC模块,若电流较大,应在PCB上设计散热铜箔或散热孔;

在系统长期运行环境下,监测稳压芯片温度,一旦过温,可通过软件降低主频或进入低功耗模式;

开关电源输出端与敏感模拟信号线应分开走线,电源与地回流路径应尽量短;

在电源线上加入共模电感和差模电感组合滤波,减少电磁辐射;

对于直流母线或不稳定电源,需在输入端加TVS二极管或MOV压敏电阻,防止瞬态浪涌损坏芯片;

对于工业电源环境,可加一只过压保护器(OVP)与过流保护器(OCP);

浪涌与稳压

EMI/EMC设计

热管理

电源布局与接地策略

电源线宽度应足够,根据电流大小计算Trace宽度;

避免电源线与高频信号线并行,减少串扰;

在每个电源引脚附近布置至少一个0.1μF陶瓷电容,用于高频去耦;

增加4.7μF或10μF的低ESR电容用于中低频滤波;

将数字地与模拟地分开走线,在电源输入端汇合,避免数字噪声干扰模拟电路;

若有大功率模块(如DC-DC电源模块、继电器),应单独布置电源轨,并通过低阻抗铜箔连接到主板;

电源分区与接地分割

去耦电容布置

走线规则

通过上述电源管理与供电设计相关内容,开发者可以充分考虑电源的稳定性、可靠性与EMI/EMC性能,制定合理的电源方案与PCB布局策略,以确保STM8S103F3P6系统在各类工况下稳定、可靠地运行。

十五、编程与调试技巧

STM8S103F3P6的应用开发离不开高效的编程与调试技术。本节将总结一些常见的编程技巧、调试方法以及优化建议,帮助开发者提高开发效率与代码质量。

编译器优化与代码尺寸控制

避免使用大段级联条件语句和深度递归,以减少编译器调用堆栈;

使用 static 或 const 修饰常量与函数,以便编译器将它们放在只读存储区,减少RAM使用;

在外设库中,针对只用到某些模块时,裁剪不必要的驱动代码;对于外置库,可只引用需要的头文件与源文件;

在Cosmic中,可选择 -O1、-O2、-O3 优化等级;一般推荐在调试阶段使用 -O0,在发布版本使用 -O2 或 -O3;

在IAR中,可通过Project Options中的“Optimization”选项卡配置代码优化与尺寸优化;

Cosmic编译器在代码尺寸与性能方面表现优秀,但为商业收费软件;

SDCC开源免费,适合预算有限或教育领域,但生成代码体积较大;

IAR具有极佳的优化能力,适合对尺寸与速度要求极高的项目;

编译器选型

优化级别选择

代码尺寸控制

调试工具使用

虽然STM8S不支持SWD接口,但可以通过第三方JTAG快速烧录与调试;

部分高端调试器(如SEGGER J-Link)支持STM8接口,可以进行更高速下载与调试;

对于简单的功能测试,可通过控制LED闪烁进行状态指示;

通过蜂鸣器发声(固定频率或变频)辅助诊断系统状态;

在应用关键位置添加串口打印信息,通过USART或USB转串口模块实时查看日志;

串口波特率一般设置为115200 bps,以保证足够的输出速度;

注意在正式版本中去除或屏蔽日志输出,减少干扰与代码尺寸;

在STVD中配置SWIM接口,设置调试时钟与复位模式;

支持单步执行、断点设置、变量与寄存器观察;

对于需要跟踪寄存器值或外设寄存器配置的场景,可在寄存器窗口实时监测;

SWIM仿真与在线调试

串口调试与日志输出

LED与蜂鸣器调试

JTAG/SWD分析(仅限支持设备)

常见Debug技巧

利用STM8S的Bootloader功能,可实现UART或SPI方式的固件升级,无需外部编程器;

Bootloader区通常为闪存前1KB,将固件升级程序放置于该区域,并通过开机进入特定模式时执行;

上电后检测特定按键或外部设备命令,如果满足进入Boot模式,则启动Bootloader进行接收与编程流程;

STM8的中断优先级由向量号决定,向量地址越低优先级越高;

在编写中断服务程序时,应尽量缩短中断处理时间,避免多个中断冲突;

对于中断可能产生的共享资源(如缓冲区),在访问时应禁止其他中断或使用原子操作进行访问保护;

在需要精准时间延迟(如串口波特率校准、协议时序控制)时,可通过定时器输出比较或捕获功能测量实际时钟频率,校准CKDIVR中的分频值;

定时器校准

中断嵌套与优先级

Flash编程与Bootloader

软件架构与模块化设计

在底层驱动函数中返回错误码或状态标志,供上层应用进行判断与处理;

在关键操作(如Flash擦写、I²C通信)失败时及时恢复或重试,并在调试阶段通过串口输出错误信息;

将外设驱动(GPIO、USART、I²C、SPI、ADC、TIM等)写成独立模块,提供初始化与基本API;

对于项目中通用功能(如串口调试、EEPROM读写、CRC校验),可以封装通用函数库;

通过头文件引用与Makefile或项目配置管理,保证模块独立、易于移植与维护;

底层驱动层(HAL):封装对寄存器的直接操作,实现对外设的初始化与基本功能;

中间层(Middleware):在HAL基础上封装通用协议(如I²C、SPI驱动器)、文件系统、网络协议等;

应用层(App):具体业务逻辑实现,如温度控制、数据采集、通信协议实现等;

层次化分层设计

模块化与可重用性

错误处理与日志记录

性能优化建议

避免使用浮点运算,可采用定点运算或查表法实现复杂计算;

对于快速傅里叶变换(FFT)等需要大量计算的算法,可选择精简版或直接在外部DSP芯片上实现;

在空闲时刻调用 HALT 或 STOP 指令降低功耗,而无需频繁轮询,同时时钟保持在低速;

虽然STM8S103F3P6不具备硬件DMA,但可在SPI或USART传输中使用双缓冲机制,通过中断在缓冲区之间切换,实现类似DMA效果;

对于高频率输入捕获或PWM计数,可将中断入口函数尽量简单,数据处理放到主循环或低优先级任务中;

在定时器中断中仅读取数据并放入环形缓冲,降低中断时长;

减少中断开销

使用DMA或模拟DMA

利用低功耗指令

算法优化

通过以上编程与调试技巧的总结,开发者能够在项目开发过程中更加高效地定位问题、优化代码、提升系统性能,并在后期维护中快速迭代升级。

十六、应用注意事项与最佳实践

在实际工程项目中,除了对STM8S103F3P6功能的掌握与开发工具的使用外,还需要关注一些常见的应用注意事项、风险控制以及最佳实践。本节将从可靠性、兼容性、维护性、安全性四个方面进行探讨。

系统可靠性与容错设计

STM8S103F3P6在–40°C至+85°C温度范围内可稳定工作,但若应用环境温度接近极限时,要考虑降频或增加散热;

在高湿、高腐蚀环境中,可在PCB上涂覆防护漆或使用金属防护壳;

在电源设计中要充分考虑浪涌、电磁干扰,采用软硬件结合方式进行抑制,如采用滤波网络、隔离措施;

对关键模拟信号(如ADC)进行差分采集,并在线性测量前进行均值滤波;

在对可靠性要求极高的系统(如工业自动化控制)中,可采用双机热备,通过看门狗监控对方健康状态,一旦检测到异常,切换到备机;

关键外设(如EEPROM、外部ADC)宜采用双通路设计,保证单点故障时仍有备用;

必须在项目中启用IWDG或WWDG,并确保在关键代码中及时重载;

在启动阶段检测复位原因寄存器(RST_SR),对上一次复位类型(如IWDG复位、电源复位)进行记录与处理;

看门狗与复位策略

冗余设计与双机热备

电压异常与抗干扰

温度与环境影响

兼容性与升级策略

如果后续需要升级到STM8S系列更高容量Flash或更高性能产品(如STM8S105C6),应保持引脚及外设一致性,以实现无缝替换;

在原理图与PCB布局中注明关键信号走线与后续替换方案,避免因更换芯片导致的走线问题;

在板卡设计时,尽量保留部分引脚用于将来升级或扩展外设功能;

使用通用外设接口(如I²C总线、UART总线),便于在后期添加新传感器或模块;

在生产环境中要对不同固件版本进行标识,通过Flash的特定区块或外部EEPROM保存版本号,便于后续升级与回滚;

采用模组化固件设计,将Bootloader与应用代码分离,以便在现场通过串口或网络方式远程升级;

固件版本管理

外设升级与接脚兼容

硬件兼容性

维护性与故障诊断

对于传感器、通信模块等易损或易升级的外设,采用插拔式接口(如杜邦线或插座),方便维护与更换;

保留测试点(测试针脚)用于调试与测量,如VDD、VSS、SWIM、USART_TX/RX等;

上电自检流程中检测关键外设(如ADC、时钟、通信接口)是否正常工作,如若不正常则通过IWDG复位并记录异常;

看门狗触发前可记录系统堆栈或调用链,以便后续分析死机原因;

在关键故障或异常事件发生时,将故障码与故障状态存储到EEPROM或Flash指定区块,以便后期维护人员读取诊断;

结合串口输出与LED指示,在现场快速定位问题;

日志与故障码设计

自检与看门狗协同

硬件接口可插拔设计

安全性与防护策略

在设计中加入PCB防拆检测(如涂覆防篡改涂层、安装微动开关检测板盖打开);

对于特别敏感的场景,可增加自毁电路,一旦检测到非法拆卸或破解,触发EEPROM清除;

在Bootloader中设置访问密码,避免外部非法人士通过SWIM或USART轻易下载或修改固件;

对UART、I²C、SPI等通信接口在不使用时关闭中断与时钟,使其处于高阻态;

对存储在EEPROM或外部存储器中的重要数据(如用户密码、配置信息)进行简单加密(如异或或AES),防止被轻易读取;

通信过程中使用对称加密算法(如AES-128)保护数据传输安全;

利用STM8的Flash读保护功能(RDP级别2),完全禁止外部读出Flash内容,防止程序被窃取;

在重要通信协议中加入CRC校验或CRC-16校验,以防止数据被恶意篡改;

代码安全与加密保护

数据完整性与加密

外部访问控制

硬件抗攻击

通过以上最佳实践与应用注意事项,开发者可以在设计之初便将可靠性、兼容性、维护性与安全性纳入考量,减少项目后期维护成本,提升产品综合竞争力。

十七、常见问题与解决方案

在基于STM8S103F3P6进行开发时,工程师经常会遇到各种硬件与软件问题。以下列举若干典型问题与对应解决方案,供读者参考。

上电后程序不运行或无法进入主函数

在项目设置中检查“Option Bytes”中的复位向量地址,确保指向主程序入口;

外部复位电路:在RESET引脚加10kΩ上拉电阻与0.1μF电容,形成上电延迟;

确保SWIM引脚未短接到低电平,BOOT引脚应浮空或上拉;

复位向量错误:程序入口地址不正确;

上电复位时间过短:供电电压未稳定即开始执行;

SWIM或BOOT引脚状态异常:可能误认为要进入Bootloader模式;

原因分析

解决方案

UART通信乱码或不稳定

计算并校验BRR寄存器值,确保波特率误差在3%以内;

建议使用HSE或外部晶振作为系统时钟以提高UART时序精度;

在GPIO配置中将TX设置为推挽输出,RX设置为浮空输入;

波特率不匹配:串口波特率与终端设置不一致;

时钟源不稳定:使用HSI作为时钟源时,波动影响串口速率;

TX/RX引脚复用错误:GPIO配置不正确,导致电平异常;

原因分析

解决方案

ADC测量值漂移、大幅波动或偏差较大

在ADC输入与信号源之间加运放跟随器或缓冲电路,降低源阻抗;

在ADC输入端加RC滤波,小信号电容与电阻结合滤除高频噪声;

在切换通道后延时几微秒再启动采样;

对采集结果进行多次采样并计算平均值,减小随机噪声;

输入源阻抗过高,采样电容无法及时充电;

电源纹波与地线噪声耦合到ADC输入;

未进行足够的采样时间等待或采样通道切换时未清空采样电容;

原因分析

解决方案

外部中断无法触发或重复触发

检查对应EXTI_CR寄存器位设置,确保触发条件(上升沿/下降沿)正确;

为输入引脚添加上拉或下拉电阻,避免浮空抖动;

在中断服务程序开始时及时清除EXTI标志位(在读取SR寄存器后再写1清零);

GPIO中断配置错误:CR1/CR2寄存器设置不当;

输入引脚处于浮空状态,无稳定电平,导致抖动触发;

中断标志位未及时清除,导致重复中断;

原因分析

解决方案

看门狗复位频繁但不清楚原因

在主循环中调用 IWDG_KR = 0xAAAA; 重载看门狗,并确保重载周期小于看门狗超时;

调整WWDG窗口大小,保证实际重载时机落在窗口期内;

在调试阶段通过RST_SR寄存器读取复位原因,定位具体复位触发源;

主循环或关键中断执行时间过长,未及时刷新IWDG;

误将WWDG窗口参考值配置不当,导致窗口期外重载触发复位;

原因分析

解决方案

PWM输出不符合预期或无输出

在CLK_PCKENR1相关位上写1,使能TIM1/TIM2/TIM3时钟;

在GPIO配置中将对应引脚设置为复用推挽输出,并在AF寄存器中选择定时器功能;

在TIM_CR1中置CEN位,在TIM_CCER中置CCxE位,启动PWM输出;

定时器时钟未开,PCKENR相应位未使能;

GPIO引脚未配置为复用输出,导致无法输出PWM;

TIM_CR1中未使能计数器,或TIM_CCER中未使能通道输出;

原因分析

解决方案

通过对常见问题与解决方案的总结,开发者在遇到实际问题时可以迅速定位并解决,大大缩短调试时间,提升开发效率。

十七、总结

STM8S103F3P6凭借其成本低廉、性能稳定、外设丰富、易于开发的优势,成为许多中低端嵌入式系统设计首选方案。从硬件架构、外设功能到开发工具链和典型应用案例的全方位介绍,可以看出STM8S103F3P6在家电控制、工业传感、智能仪表、智能家居等领域具有广泛的应用潜力。在实际项目设计中,需要结合系统需求,合理规划时钟与功耗管理、ADC与定时器配置、通信接口与I/O布局,并注重电源设计与EMI抑制、看门狗与安全防护等细节。通过标准外设库与调试工具的配合,开发者能够快速搭建原型,实现功能验证,并在优化软件结构与硬件布局后完成产品量产。掌握好了STM8S103F3P6的基础知识与最佳实践,必能为您的嵌入式应用带来更高的可靠性与竞争力。

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)