74LS74 D型正边触发触发器详解

一、引言

74LS74是一个广泛使用的D型正边触发触发器(D Flip-Flop),属于74系列集成电路中的一员。作为数字电路中重要的存储元件,D型触发器在数据存储和状态保持等多种应用中扮演着重要角色。本文将深入探讨74LS74的常见型号、参数、工作原理、特点、作用和应用。

二、常见型号

74LS74系列有多个型号,以下是一些常见型号:

74LS74:标准D型触发器,正边触发,具有两个触发器。

74HCT74:高电平兼容TTL的D型触发器,适用于CMOS电路。

74HC74:高电平兼容的D型触发器,适用于更广泛的电压范围。

三、主要参数

在分析74LS74的性能时,以下是一些关键参数:

工作电压:4.75V至5.25V(标准TTL电压)

最大功耗:约为100mW

输入电压范围:0V至5V(逻辑电平范围)

输出电流:最大可达20mA(每个输出)

时钟频率:最大为30MHz(具体频率取决于电路设计)

四、工作原理

4.1 D型触发器的基本概念

D型触发器是一个时序逻辑电路,其主要功能是将输入的数据在特定时钟信号的边沿采样并存储。74LS74包含两个相同的D触发器,分别称为D1和D2,通常可以独立使用。

4.2 触发器的工作原理

D型触发器的工作过程如下:

输入端:触发器有一个D输入(数据输入),一个CLK输入(时钟输入)和两个输出Q和Q'(反相输出)。

时钟信号:当时钟信号的上升沿到达时,D输入的状态被锁存到Q输出。换句话说,D的状态在时钟上升沿时被“采样”并保存。

保持状态:一旦数据被锁存,无论D输入如何变化,Q输出都会保持该状态,直到下一个时钟边沿到来。

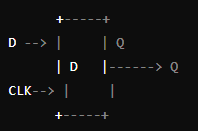

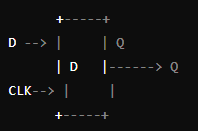

4.3 逻辑符号

D型触发器的逻辑符号通常如下所示:

在时钟信号CLK的上升沿,D的值被传送到Q输出。

五、特点

74LS74 D型触发器具有以下显著特点:

正边触发:触发器仅在时钟信号的上升沿有效,这有助于消除抖动和干扰带来的错误。

双触发器结构:74LS74内部包含两个独立的D触发器,可以同时进行数据存储和处理。

高速:74LS系列具有较高的工作速度,适用于快速时序逻辑电路。

TTL兼容性:与其他TTL逻辑电路兼容,便于集成和使用。

六、作用

74LS74 D型触发器在数字电路中起到以下几方面的作用:

数据存储:能够存储单比特数据,在数据处理和传输中起到缓冲作用。

状态保持:用于保持电路的状态,尤其在同步时序电路中。

数据锁存:在需要将数据从一个时钟周期转移到另一个周期时,74LS74能够在时钟边沿锁存数据。

计数器和寄存器:可用于构建计数器、移位寄存器等更复杂的数字电路。

七、应用

74LS74 D型触发器广泛应用于各种数字电路中,主要包括:

时序电路:如计数器、分频器等。

数据寄存器:用于存储数据,特别是在微处理器和控制系统中。

状态机设计:在有限状态机(FSM)中用于状态存储和转换。

同步数据传输:用于在多个逻辑电路之间同步数据传输。

7.1 时序电路

在时序电路中,74LS74 D型触发器可以作为基本的存储元件,结合其他逻辑门实现更复杂的功能。例如,在计数器电路中,多个D触发器可连接在一起,实现对输入脉冲的计数。

7.2 数据寄存器

74LS74可用于构建数据寄存器,用于在计算机中存储和转移数据。例如,在CPU中,D触发器可以存储操作数或指令,确保在特定时钟周期内正确执行。

7.3 状态机设计

在状态机设计中,74LS74用于实现状态的存储和转移。例如,在交通信号控制系统中,状态机可以根据交通流量变化切换信号灯的状态。

7.4 同步数据传输

在需要同步数据传输的系统中,74LS74 D型触发器能够确保数据在时钟信号的控制下可靠地传输。例如,在数据总线的应用中,可以通过D触发器实现数据的锁存和传送。

八、数字电路中不可或缺的基本元件

74LS74 D型正边触发触发器是数字电路中不可或缺的基本元件,具有数据存储、状态保持、数据锁存等多种功能。其双触发器设计、TTL兼容性和高速性能,使其在时序电路、数据寄存器、状态机设计和同步数据传输等应用中发挥着重要作用。了解和掌握74LS74的工作原理及应用,可以为设计和开发数字电子系统提供强有力的支持。通过合理利用74LS74,我们能够设计出更为复杂和高效的数字电路,为各类电子产品的性能提升打下基础。

九、74LS74 的电气特性

9.1 电气特性

了解74LS74的电气特性对于设计电路至关重要。以下是其主要电气特性参数:

输入电流:当输入高电平时,输入电流通常在-0.2至-1.0毫安之间(最大值为±20μA),而在低电平状态下,输入电流几乎为零。

输出电压:在逻辑高状态时,输出电压通常接近于Vcc(5V),而在逻辑低状态时,输出电压接近于0V。

开关时间:74LS74的开关时间(包括传播延迟和上升/下降时间)约为15纳秒,具体数值依赖于电路的负载条件和工作频率。

功耗:74LS74的静态功耗通常较低,典型值为20mW,最大功耗可达100mW。由于其低功耗特性,使其在低功耗应用中表现出色。

9.2 时序特性

74LS74的时序特性对于确保电路正常工作至关重要。其时序参数主要包括:

传播延迟时间(tpd):表示输入信号在时钟边沿到达输出状态所需的时间。通常为15-25纳秒,具体取决于负载电流和电源电压。

时钟高电平持续时间(th):要求时钟信号在高电平时应持续一定的时间,通常为10纳秒。

数据保持时间(th):在时钟上升沿到来之前,D输入的数据必须保持有效的时间,通常为5纳秒。

数据建立时间(ts):在时钟信号的上升沿之前,D输入的数据应被设置好的时间,通常为5纳秒。

这些时序参数可以帮助工程师确保74LS74在高速应用中正确工作。

十、74LS74 的优缺点

10.1 优点

高速度:74LS74的快速响应能力使其适合于高频应用,如高速计数器和数据锁存器。

双触发器设计:集成两个D触发器节省了电路板空间,同时简化了电路设计。

良好的兼容性:与TTL电路良好的兼容性使其在各种数字电路中广泛应用。

简单的接口:D型触发器的输入和输出接口简单易用,适合各种应用场景。

10.2 缺点

功耗:尽管74LS74的功耗较低,但在高频应用中,功耗仍然是一个需要考虑的重要因素。

温度敏感性:74LS74在高温环境下可能会导致性能下降,因此在某些特定应用中需要进行温度管理。

时序限制:在复杂的时序逻辑电路中,设计者需要非常注意时序参数,确保信号不会出现错误。

十一、74LS74 的设计考虑

在设计基于74LS74的电路时,有几个关键因素需要考虑:

电源管理:确保电源稳定,避免电压波动影响74LS74的工作。

时钟信号:设计稳定且清晰的时钟信号,以确保触发器在正确的时钟边沿锁存数据。

输入输出设计:合理设计D输入和Q输出,以防止短路或过载。

11.1 电路布局

在PCB设计中,74LS74的布局也需要特别关注,尤其是在高频应用中:

减少走线长度:尽量减少信号线长度,以降低延迟和噪声干扰。

合理的地线设计:为触发器提供稳定的地线连接,避免地线噪声对触发器工作的影响。

电源旁路电容:在电源引脚上使用旁路电容,以减少电源波动对性能的影响。

11.2 逻辑分析与仿真

在设计完成后,使用逻辑分析仪或仿真软件进行验证,可以帮助确认电路在实际应用中的表现。这对于发现潜在问题和优化设计至关重要。

十二、74LS74 的替代品

在现代电子设计中,可能会遇到需要使用74LS74的替代品。这些替代品包括:

74HC74:更高的速度和更广泛的电源电压适用范围,更适合现代CMOS设计。

74HCT74:TTL兼容性更强,适合多种逻辑电路的应用。

在选择替代品时,需要综合考虑电路的性能要求和兼容性。

十三、74LS74 在实际应用中的案例

13.1 计数器设计案例

在一个简单的二进制计数器设计中,可以使用两个74LS74触发器构成一个4位二进制计数器。在此设计中,时钟信号连接至每个D触发器的CLK输入,而D输入则连接至Q'输出,以形成反馈回路。这种设计确保每个触发器在时钟边沿时对输入数据进行采样,从而实现计数功能。

13.2 状态机应用

在某些控制系统中,可以使用74LS74构建有限状态机(FSM)。例如,在交通信号控制系统中,D触发器可以用来表示不同的信号灯状态(红灯、绿灯、黄灯),并根据传感器输入和定时器生成的时钟信号进行状态转换。

13.3 数据存储应用

在数据传输系统中,74LS74可以用作数据锁存器。通过时钟信号的控制,系统可以在特定时刻锁存输入的数据,并在后续处理过程中保持数据不变,直到需要再次更新。

十四、总结与展望

74LS74 D型正边触发触发器是现代数字电路中不可或缺的基本组件。凭借其高速性能、低功耗特点以及广泛的应用范围,它在许多电子设备中发挥着重要作用。随着技术的发展,未来可能会出现更高性能的触发器,以满足更复杂电路设计的需求。

通过对74LS74的深入了解,设计者能够更有效地利用这一组件进行电路设计,实现更高效、更可靠的数字系统。掌握74LS74的使用与设计原则,将有助于工程师在日益复杂的电子设计中做出明智的决策。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)