触发器原理:基本概念、工作原理、应用场景和未来发展

19

19

拍明芯城

拍明芯城

触发器原理

摘要:

触发器是数字电路中一种重要的元件,它能够存储和传输信息,并在特定条件下改变输出状态。本文将从四个方面对触发器原理进行详细阐述:基本概念、工作原理、应用场景和未来发展。通过深入了解触发器的工作原理,可以更好地应用于实际电路设计中。

一、基本概念

触发器是一种具有两个稳定状态(0或1)的数字元件,它可以根据输入信号的变化而改变自身状态,并且在特定条件下保持当前状态不变。触发器由多个逻辑门组成,最常见的是D型触发器和JK型触发器。

D型触发器具有一个数据输入端(D)、时钟输入端(C)和输出端(Q),当时钟信号为高电平时,在上升沿或下降沿时,将数据输入到输出端;当时钟信号为低电平时,则保持之前的输出状态不变。

JK型触发器除了具有数据输入端(J, K)、时钟输入端(C)和输出端(Q),还增加了一个使能控制端(E),使得其更加灵活可控制。当使能控制信号为高电平并且满足特定条件(根据J和K的取值),触发器将改变输出状态。

二、工作原理

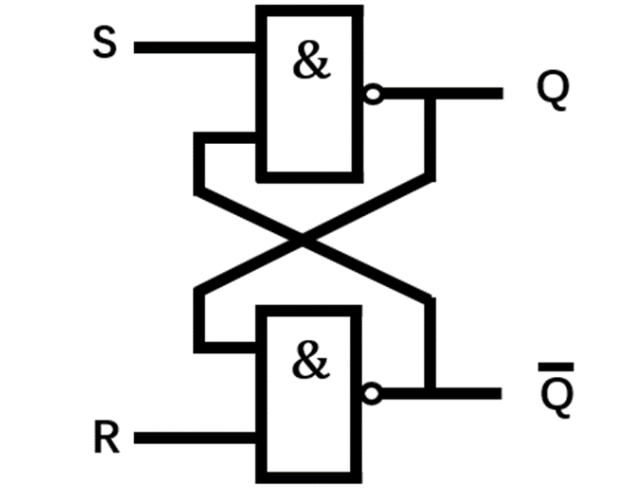

触发器的工作原理是基于逻辑门电路实现的。D型触发器通过与非门(NOT)和与门(AND)构成,JK型触发器则由与非门、或门(OR)和异或门(XOR)组成。

在D型触发器中,当时钟信号为高电平时,通过与非门将数据输入反相后再输入到与非门中,并且通过与非门和AND门形成一个锁存功能。当时钟信号为低电平时,锁存功能失效,输出保持不变。

在JK型触发器中,使能控制端可以对输入进行控制。当使能控制信号为高电平并且J=1, K=0时,在上升沿或下降沿改变输出状态;当J=0, K=1时,在上升沿或下降沿反转输出状态;当J=1, K=1时,在上升沿或下降沿保持之前的状态不变;当使能控制信号为低电平,则无论J和K如何取值都不会改变输出状态。

三、应用场景

触发器广泛应用于数字系统设计中。它可以用来存储数据、实现计数功能以及完成各种逻辑运算等任务。

在计算机中,触发器被用于存储和传输数据,构成寄存器、缓冲器等重要组件。在时序电路中,触发器可以实现状态机、计数器等功能。此外,在通信系统、控制系统和数字信号处理等领域也有着广泛的应用。

四、未来发展

随着科技的不断进步,触发器原理也在不断演变和完善。目前已经出现了更多种类的触发器,如T型触发器、SR型触发器等,并且还有更高速度和更低功耗的设计。

同时,在大规模集成电路(VLSI)领域,对于多位宽数据传输以及高速时钟频率要求下的稳定性问题提出了新挑战。因此,在未来的研究中需要进一步优化设计方案,并探索新型材料与结构以满足不同应用场景下对于稳定性和可靠性的需求。

总结:

本文从基本概念、工作原理、应用场景和未来发展四个方面详细阐述了触发器原理。通过深入了解其工作原理,我们可以更好地应用于实际电路设计中,并为未来相关技术研究提供参考。

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)