SNIA规范获取在CXL环境中移动的数据

30

30

拍明芯城

拍明芯城

原标题:SNIA规范获取在CXL环境中移动的数据

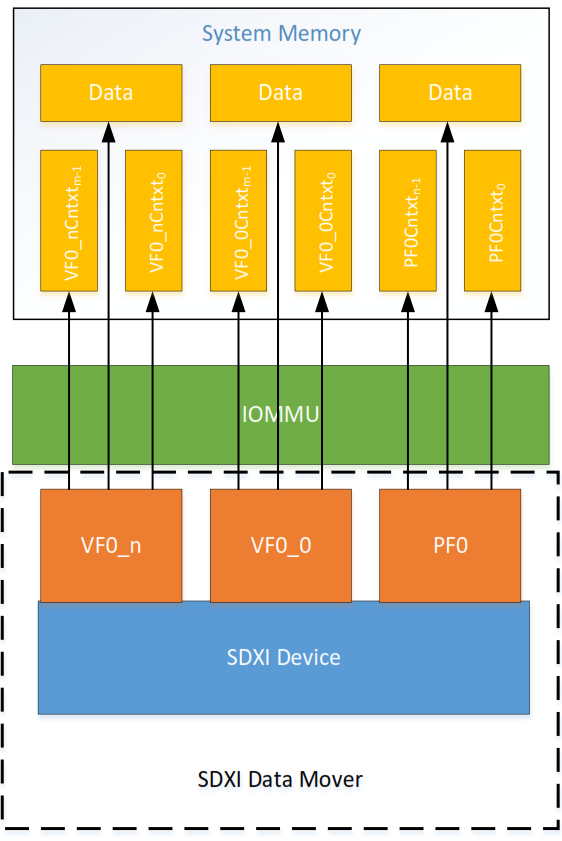

SDXI 规范是内存到内存数据移动器和加速接口的标准。

计算高速链路 (CXL) 规范可以说是半导体行业中成熟最快的接口之一。它的广泛支持意味着许多供应商将产品设计为 构建生态系统,存储网络行业协会 (SNIA) 是最新推出的,以帮助进一步改善数据移动。

11月28日,SNIA推出了 智能数据加速器接口 (SDXI) 规范.与 CXL 类似,SDXI 规范优先考虑高效的数据移动;具体来说,SDXI是存储器到存储器数据移动器和加速接口的标准。该规范的起源可追溯到 2020 年 9 月,当时 SNIA 技术工作组 (TWG) 着手实现直接内存访问 (DMA) 数据移动器设备的概念并解决常见的限制。

DMA 的作用是卸载基于软件的复制循环,以释放 CPU 执行周期。尽管这个概念是众所周知的,但DMA的采用通常仅限于特定的特权软件和I/O用例,这些用例使用特定于设备的接口,这些接口不向前兼容。这些限制意味着用户模式应用程序在非虚拟化环境中使用很困难,在多租户虚拟化环境中几乎不可能。

DMA 数据移动器设备来卸载基于软件的复制循环以释放 CPU 执行周期的概念并不新鲜,但采用主要限于特定的特权软件和 I/O 用例,这些用例使用非常特定于设备的接口,这些接口不向前兼容。(来源:SNIA)

SDXI 可与 CXL 和异构计算配合使用

SNIA开发了SDXI标准,以提供一个架构接口来解决当前的DMA限制,SNIA TWG主席Shyam Iyer在SDXI平台数据移动器的在线简报中表示。除了克服DMA的现有限制外,SDXI还将支持异构计算与 CXL,现已进入第三次迭代。

根据Iyer的说法,当今系统架构的大多数需求都是从应用程序级别开始的,计算需求通常由CPU解决。当计算发生时,数据存储在内存中,内存与 CPU 共享一致性关系以提高性能。

“当应用程序需要扩展时,它会向其添加更多线程,”他说。Iyer补充说,这意味着CPU上有更多的内核,而每当数据需要从内存中传输出来时,就会使用I / O设备,并优化以解决延迟和带宽问题。“这是一个运行良好的系统架构,但最近,我们看到对应用程序的需求增加,这意味着典型的计算架构正在发展。

Iyer解释说,当今的典型架构具有CPU和特定于应用的标准部件,包括驱动器,网络接口控制器和现场可编程门阵列(FPGA),所有这些都试图提高应用性能以及许多存储器类型。混合使用链路和结构,例如 CXL,一切都可以连接。“这意味着内存类型通过这些类型的链接和结构真正民主化,应用程序可以利用所有这些,”他说。“但它们也有相同的设计限制,无论是延迟、带宽、一致性还是控制。

一切都与数据移动有关

在基本层面上,CXL 就是将数据轻松移动到可用的最佳资源(包括内存或存储),部分原因是减少数据必须传输的距离。它作为标准迅速获得了动力,最近成立了 CXL 联盟 已发布 3.0 版 在八月的闪存峰会上。CXL 财团还收购了 Z世代联盟的知识产权,具有类似特征的规范。OpenCAPI资产也被纳入CXL联盟,以推进标准。

CXL 联盟贡献者和 AMD 的 CXL 系统架构师 Rita Gupta 表示,CXL 规范经历了业界非常积极的参与,“谁是谁”参与了该联盟。“CXL 正在成为相干 I/O 标准的行业焦点。”

Gupta表示,与DMA的努力一样,I/O一致性也有适当的尝试,但过去几年的趋势不仅反映了对数据处理和计算的需求增加,而且还反映了对异构计算的需求。这种需求意味着将不同类型的内存和设备连接在一起并一起执行。“所有这些都意味着您需要越来越多的内存容量和带宽。

CXL 是第一个全面解决 I/O 互连问题的开放标准。作为处理器的高速缓存相干互连标准,CXL 利用 PCIe 基础设施 混合搭配三种协议:CXL.io、CXL.cache 和 CXL.memory。

“这是一个低延迟标准,”古普塔说。“如果你看一下CXL.memory和CXL.cash访问,它们的目标是接近CPU延迟的地方。她补充说,CXL还提供了不对称的复杂性,以便减轻设备实现的维护一致性的负担。

混合和匹配三种 CXL 协议允许许多不同的用例。Gupta说,例如,您可以将具有 CXL.io 和CXL.memory接口的设备视为CXL内存缓冲区,而使用所有三种协议的设备可以由主机管理其内存。

CXL 的第一次迭代引入了三种类型的设备,主要功能是点对点连接,而版本 2.0 增加了扇出、交换和内存池。在 CXL 3.0 中,重点转移到了可扩展性上。“如果你看看CXL规范的进展,它不仅仅是关注我们今天面临的计算行业的问题,而是着眼于未来的问题,”Gupta说。

Gupta指出,由于CXL是一个与媒体无关的接口,因此可以在系统中添加低成本的存储器,以降低其总体拥有成本(TCO)。这是因为内存分层使“热”数据可以放置在较快的内存中,而“冷”数据可以放置在较慢的层中。“这就是数据时刻变得极其关键的地方。

Gupta解释说,通过这种使用模式,可以将容量和带宽添加到系统中,同时降低其TCO,并且多个主机可以访问一个内存位置,并通过 CXL 协议.“这些使用模型旨在减少内存搁浅,因为如果你看看非常昂贵的内存资源,它们在不同的系统中得到了有效的利用,”她说。“这种资源分解有助于提高数据使用效率。

CXL 的流动性通过 SDXI 加速

前进到 异构计算,数据移动变得越来越重要,Gupta说。“CXL 实现的是一个非常流畅和灵活的内存模型。”

不同的内存类型、扩展器和加速器都可以作为资源使用,但至关重要的是,在所有内存中数据移动都尽可能高效。

Iyer说,今天的数据移动通常是一个基于软件的内存副本,它使用稳定的指令集架构 - 应用程序可以轻松使用的标准,因为它很熟悉。然而,根据Iyer的说法,应用程序性能会下降,因为计算机被用来执行数据复制。与此同时,现有DMA的问题在于它们都是特定于供应商的。“在这些DMA引擎的帮助下,用户级软件没有标准化的访问。

这就是SDXI变得至关重要 - “X”代表加速器。Iyer表示,SNIA提出的标准是内存到内存的数据移动接口,该接口可扩展,向前兼容且独立于I / O互连技术。“SDXI 接口实现可以存在于不同的外形规格上。

例如,它可以以集成方式在CPU上实现,也可以在GPU或FPGA等离散芯片甚至智能I / O设备中实现,而该设计消除了所有软件上下文隔离层,以提高性能并实现应用程序的直接用户模式访问,根据Iyer的说法。

基本的 SDXI 体系结构由一些智能数据加速器组成,这些加速器枚举为一个或多个 SDXI 函数。(来源:SNIA)

与 CXL 一样,SDXI 针对不同类型的内存。他说,通过拥有一个本质上是架构的规范,你可以构建利用相同接口的额外卸载。

在许多用例中,标准化 DMA(如 SDXI)很有价值,因为它允许应用程序以描述符的形式指示工作项 — 数据复制可以在应用程序可以自由执行其他操作的同时完成,并在复制完成后收到通知。Iyer 指出,使用 SDXI 可以以不同的方式执行的另一种情况是数据的存储和检索,这通常由多个内存缓冲区副本完成,这些副本可能会降低性能——即使借助内存架构中的持久内存区域也是如此。

Iyer说,SDXI大放异彩的第三种情况是,当两台机器想要将数据移动到彼此的地址空间时,这可以通过加速器进行优化,该加速器可以安全可靠地从一台来宾版本的机器上读取数据缓冲区,旋转它,然后将该数据缓冲区写入第二个虚拟机。“这是两全其美的。”

尽管SDXI提供了好处,但这是一项正在进行的工作,Iyer说。目前,SNIA的TWG正在探索如何在发出数据移动请求之前在多个地址空间之间建立连接,以及SDXI在CXL和异构环境中更好地工作的不同方式。“它独立于架构,独立于实现和互连,”他说。

本文最初发表于 电子电气时报.

加里·希尔森 是一位自由撰稿人和编辑,为北美各地的印刷和像素出版物撰写了数千字。他感兴趣的领域包括软件、企业和网络技术、研究和教育、可持续交通和社区新闻。他的文章发表在Network Computing,InformationWeek,Computing Canada,Computer Dealer News,Toronto Business Times,Strategy Magazine和Ottawa Citizen上。

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)