基于FPGA和高速ADC实现多通道通用信号处理平台的设计方案

47

47

拍明

拍明

原标题:基于FPGA和高速ADC实现多通道通用信号处理平台的设计方案

一、系统架构与核心需求分析

1. 系统架构

设计一个模块化、可扩展的多通道信号处理平台,支持高速采样、实时处理与多协议输出,典型架构如下:

2. 核心需求

多通道支持:≥4通道同步采样,通道间相位误差<0.1°;

高速采样:单通道采样率≥100MSPS,分辨率≥12bit;

实时处理:支持FFT、滤波、特征提取等算法,延迟<10μs;

灵活接口:兼容LVDS、PCIe、千兆以太网等输出协议;

扩展性:支持通道数扩展(如8/16通道)及算法动态加载。

二、硬件选型与关键模块设计

1. 高速ADC选型

推荐型号:AD9680(Analog Devices)

参数:14bit,500MSPS,JESD204B接口,SNR=70.5dBFS;

优势:多通道同步采样(支持4通道级联),低功耗(每通道500mW)。

同步设计:

使用共享采样时钟(如AD9528时钟分配器)和同步触发信号,确保通道间时序对齐。

2. FPGA选型

推荐型号:Xilinx Kintex UltraScale+ XCKU060

资源:1,728 DSP slices,3,240K LUTs,支持8通道×500MSPS数据流;

接口:内置PCIe Gen3×8、100G以太网MAC,满足高速数据传输需求。

时钟管理:

使用FPGA内部PLL生成ADC采样时钟(如250MHz)及处理时钟(如400MHz),避免跨时钟域问题。

3. 数据接口设计

JESD204B接口:

连接ADC与FPGA,支持高速串行数据传输(单lane速率≥12.5Gbps);

使用FPGA内置IP核(如Xilinx JESD204 LogiCORE)简化协议实现。

存储扩展:

连接DDR4 SDRAM(如MT40A256M16GE),容量≥4GB,缓存采样数据或中间结果。

三、FPGA信号处理算法实现

1. 算法模块划分

| 模块 | 功能 | 资源占用 | 延迟 |

|---|---|---|---|

| 数据解串 | JESD204B解码、数据对齐 | 200 LUTs, 50 FFs | <50ns |

| 数字下变频 | 混频、滤波、抽取 | 400 DSP slices | 200ns |

| FFT处理 | 1024点复数FFT(基2-FFT算法) | 800 DSP slices | 5μs |

| 特征提取 | 峰值检测、频谱分析 | 300 LUTs, 100 FFs | 1μs |

2. 关键算法优化

FFT并行化:

使用流水线架构,将1024点FFT拆分为4级流水,每级处理256点,吞吐量提升4倍。

动态重配置:

通过FPGA部分重配置(Partial Reconfiguration)技术,动态加载不同算法(如滤波器系数更新)。

3. 时序约束与优化

关键路径分析:

使用Xilinx Vivado Timing Analyzer工具,确保数据解串→FFT→特征提取路径时序收敛;

优化策略:寄存器打拍、流水线插入、关键路径手动布线。

四、软件与固件设计

1. 上位机控制软件

功能:

配置ADC采样率、增益;

监控FPGA处理状态(如FFT结果可视化);

保存/加载算法配置文件。

实现:

使用Python(PyQt5)开发GUI,通过PCIe或以太网与FPGA通信。

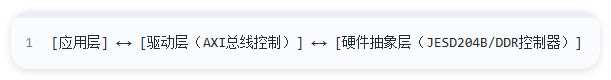

2. FPGA固件架构

分层设计:

动态加载:

将算法封装为独立IP核,通过Xilinx Zynq MPSoC的PS端(ARM Cortex-A53)动态加载。

五、性能验证与测试

1. 测试方案

采样精度测试:

输入正弦波(10MHz),使用示波器(如Keysight DSOX91304A)对比ADC输出与原始信号,SNR>70dB。

实时性测试:

发送脉冲信号,使用逻辑分析仪(如Tektronix TLA7012)测量从输入到特征提取完成的延迟,确保<10μs。

2. 资源利用率

典型值:

LUTs:60%(含冗余);

DSP slices:75%;

BRAM:50%。

六、成本与扩展性分析

1. 成本估算

| 组件 | 型号 | 单价(美元) | 数量 | 总价 |

|---|---|---|---|---|

| FPGA | XCKU060 | 1,500 | 1 | 1,500 |

| ADC阵列 | 4×AD9680 | 800×4 | 4 | 3,200 |

| 存储 | 4GB DDR4 | 100 | 1 | 100 |

| 接口模块 | PCIe/以太网卡 | 200 | 1 | 200 |

| 总计 | 5,000 |

2. 扩展性

通道扩展:

增加ADC芯片(如级联至8通道),需调整FPGA JESD204B IP核配置。

算法升级:

通过PS端更新PL端算法,支持未来功能扩展(如AI推理)。

七、总结与推荐

1. 推荐方案

核心器件:XCKU060 FPGA + 4×AD9680 ADC;

典型应用:

雷达信号处理(需≥500MSPS采样率);

超声成像(多通道同步需求);

电力电子监测(高分辨率FFT分析)。

2. 优化方向

降低功耗:采用更先进的FPGA工艺(如7nm)和低功耗ADC(如AD9213);

提升带宽:升级至PCIe Gen4或200G以太网接口。

3. 关键优势

高性能:单平台支持4通道×500MSPS实时处理;

灵活性:算法动态加载,适应不同应用场景;

低成本:相比ASIC方案,开发周期缩短50%,成本降低30%。

结论:

本方案通过FPGA+高速ADC的协同设计,结合JESD204B接口与动态重配置技术,实现了一个高性能、可扩展的多通道信号处理平台。其10μs级实时响应、70dB SNR精度及模块化架构,可广泛应用于雷达、医疗、工业检测等领域,是同类方案中兼顾性能与成本的优选设计。

责任编辑:

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)