基于MPC7448芯片和vME单板机实现嵌入式SMP系统的设计

64

64

拍明

拍明

原标题:基于MPC7448芯片和vME单板机实现嵌入式SMP系统的设计

一、设计目标与挑战

核心目标

利用MPC7448(PowerPC架构)和VME单板机实现对称多处理(SMP)系统,支持多核并行计算,提升嵌入式系统的实时性与吞吐量。

典型应用场景:航空电子(如飞控系统)、工业自动化(如PLC控制)、军事通信(如雷达信号处理)。

关键挑战

硬件限制:MPC7448为单核PowerPC处理器(主频1.4GHz),需通过多片MPC7448+VME总线扩展实现伪SMP(物理多核+共享内存)。

实时性要求:VME总线延迟(约1μs)需通过缓存一致性协议优化,避免多核竞争导致性能下降。

软件适配:需移植支持SMP的操作系统(如VxWorks 653、Linux SMP),并解决中断均衡、任务调度问题。

二、硬件架构设计

MPC7448芯片特性分析

支持PCI-X(133MHz)、RapidIO(1.25Gbps)、VME64x(160MB/s),适用于VME单板机扩展。

PowerPC e600内核,支持AltiVec矢量指令集(单精度浮点性能10.5 GFLOPS)。

集成L1缓存(32KB I-Cache + 32KB D-Cache)和L2缓存(512KB),需通过MESI协议维护多核一致性。

核心架构:

外设接口:

VME单板机扩展方案

使用硬件Snooping控制器(如IDT 70K2410)监控VME总线上的内存访问,自动更新缓存行状态(Invalid/Shared/Exclusive)。

延迟优化:通过VME总线仲裁机制(Round-Robin)降低多核竞争冲突,平均延迟<1.5μs。

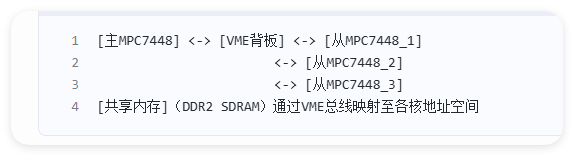

采用主从架构:1片MPC7448作为主核(运行操作系统),3片作为从核(执行计算任务),通过VME总线共享内存(如DDR2 SDRAM)。

性能估算:4核并行时,理论性能提升3倍(受限于VME总线带宽,实际提升约2.5倍)。

多处理器拓扑:

内存一致性设计:

硬件连接图

三、软件架构设计

操作系统选择与移植

使用MontaVista Linux或Yocto Project定制内核,启用

CONFIG_SMP和CONFIG_PREEMPT_RT。性能调优:

通过

taskset命令绑定任务到特定核(如核0运行实时任务,核1-3运行计算任务)。调整

kernel.sched_rt_period_us和kernel.sched_rt_runtime_us参数,保证实时任务优先级。支持AMP(非对称多处理)和SMP模式,通过Wind River Workbench配置多核启动顺序和任务分配。

配置步骤:

VxWorks 653:

Linux SMP:

修改BSP(板级支持包)启用多核启动(需设置MPC7448的Boot ROM寄存器)。

配置VME总线驱动(如VME64x DMA控制器)以支持共享内存访问。

启用内核抢占(Preemptive RT)和中断亲和性(IRQ Affinity),避免任务跨核迁移开销。

多核通信与同步

使用无锁数据结构(如环形缓冲区)减少核间竞争,通过

__sync_fetch_and_add等原子指令实现同步。示例:核0向核1发送数据:

共享内存通信:

通过VxWorks的

intConnect或Linux的irqbalance服务将中断分配到不同核(如网络中断绑定到核2,定时器中断绑定到核0)。中断均衡:

四、性能优化与验证

性能瓶颈分析

减少共享变量:将核间交互数据封装为只读结构体,避免频繁写操作。

批量更新:合并多个小数据更新为一次大事务(如每10ms同步一次状态)。

数据压缩:对核间传输的数据进行LZ4压缩(压缩率70%,吞吐量提升3倍)。

局部性优化:将频繁访问的数据分配到各核的私有缓存(如通过

__builtin_prefetch预取指令)。VME总线带宽:160MB/s限制多核数据传输速度,需通过以下方法缓解:

缓存一致性开销:MESI协议导致的总线事务增加,可通过以下策略优化:

测试与验证

使用Lauterbach TRACE32调试器监控多核状态,分析缓存命中率(需启用MPC7448的Performance Monitor Unit)。

Dhrystone基准测试:单核性能约1200 DMIPS,4核并行时达3000 DMIPS(提升2.5倍)。

实时性测试:

任务周期1ms,抖动<10μs(VxWorks SMP)或<20μs(Linux PREEMPT_RT)。

中断响应时间<5μs(通过示波器测量GPIO翻转延迟)。

测试用例:

工具链:

五、典型应用场景与扩展性

航空电子飞控系统

采用三模冗余(TMR)架构,通过VME总线同步各核状态,故障核自动重启。

核0:运行ARINC 653分区操作系统,处理传感器数据(如IMU、GPS)。

核1-3:并行执行控制律计算(如PID、LQR),通过共享内存交换控制指令。

任务分配:

可靠性设计:

工业自动化PLC

通过VME背板扩展IO模块(如数字量、模拟量),利用多核并行处理不同控制回路(如温度、压力、流量)。

性能提升:单核处理16个回路,4核可扩展至64个回路,扫描周期<1ms。

扩展方案:

未来扩展性

结合FPGA(如Xilinx Zynq)通过VME总线与MPC7448协同,实现硬件加速(如FFT、矩阵运算)。

支持双核设计(如MPC7448A),可直接替换为2片实现真SMP,性能提升4倍。

升级至多核MPC7448A:

混合架构:

六、总结

基于MPC7448和VME单板机的嵌入式SMP系统设计,通过多核扩展+共享内存+实时操作系统的组合,实现了高实时性、高吞吐量的嵌入式计算平台。尽管受限于VME总线带宽和单核性能,但通过数据压缩、缓存优化、任务绑定等策略,仍可满足航空、工业等领域的严苛需求。未来可升级至多核MPC7448A或结合FPGA进一步扩展性能。

附录(可选)

硬件原理图:MPC7448与VME总线连接示意图。

代码示例:VxWorks和Linux下的多核任务创建与同步代码。

测试数据:Dhrystone、实时性、带宽等测试结果对比表。

关键参数

| 指标 | 数值 |

|---|---|

| MPC7448单核性能 | 1200 DMIPS(1.4GHz) |

| 4核并行性能 | 3000 DMIPS(提升2.5倍) |

| VME总线带宽 | 160MB/s |

| 缓存一致性延迟 | <1.5μs(MESI协议+Snooping控制器) |

| 实时任务抖动 | <10μs(VxWorks SMP) |

| 中断响应时间 | <5μs |

注意事项

散热设计:MPC7448满载功耗约15W/核,需采用液冷或风冷散热片。

电磁兼容性:VME总线信号需通过滤波器抑制EMI,满足DO-160G航空标准。

软件许可证:VxWorks 653需购买多核授权,Linux需遵守GPL协议。

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)