dsPIC30F2011/2012/3012/3013中文资料

561

561

拍明

拍明

高性能16位数字信号控制器

高性能改进型RISC CPU:

•改进的哈佛架构

•优化的C编译器指令集架构

•灵活的寻址模式

•83条基本指令

•24位宽指令,16位宽数据总线

•最大24 KB的片上闪存程序空间

•最大2 KB的片上数据RAM

•最大1 KB的非易失性数据EEPROM

•16 x 16位工作寄存器阵列

•工作速度最高可达30 MIPS:

-DC至40 MHz外部时钟输入

-4 MHz-10 MHz振荡器输入,带PLL(4倍

频、8倍频和16倍频)

•最多21个中断源:

-每一个中断具有8个用户可选择的中断优先

级

-3个外部中断源

-4个处理器陷阱源

DSP特性:

•双数据取操作

•模寻址和位反转寻址模式

•两个具备可选饱和逻辑的40位宽累加器

•17位x 17位单周期硬件小数/整数乘法器

•所有DSP指令均为单周期指令-乘-累加(MAC)操作

•在一个周期内可将数据左右移位16位

外设特性:

•高灌电流/拉电流I/O引脚:25 mA/25 mA

•3个16位定时器/计数器;可选择将16位定时器配对组成32位定时器模块

•16位输入捕捉功能

•16位比较/PWM输出功能

•3线SPI模块(支持4种帧模式)

•I2C™模块支持多主器件/从模式和7位/10位寻址

•最多两个带有FIFO缓冲区的可寻址UART模块

模拟特性:

•12位模数转换器(ADC)具有以下特性:

-转换速率为200 ksps

-最多10个输入通道

-在休眠和空闲模式下可以进行转换

•可编程低电压检测(Programmable Low-Voltage Detection,PLVD)

•可编程欠压复位

特殊数字信号控制器特性:

•增强型闪存程序存储器:

-对于工业级温度范围,最少擦写次数1万次,典型擦写次数10万次。

•数据EEPROM存储器:

-对于工业级温度范围,最少擦写次数10万次,典型擦写次数100万次。

•软件控制下,可自行再编程

•上电复位(Power-on Reset,POR)、上电延时定时器(Power-up Timer,PWRT)以及振荡器起振定时器(Oscillator Start-up Timer,OST)

•灵活的看门狗定时器(Watchdog Timer,WDT)

带有片上低功耗RC振荡器,能保证可靠的运行

•故障保护时钟监视器操作:

-检测时钟故障并切换到片上低功耗RC振荡器

•可编程代码保护

•在线串行编程(In-Circuit Serial Programming™,ICSP™)功能

•可选择的功耗管理模式:

-休眠、空闲和备用时钟模式

CMOS技术:

•低功耗高速闪存技术

•宽工作电压范围为2.5V至5.5V

•工业级温度范围和扩展级温度范围

•低功耗

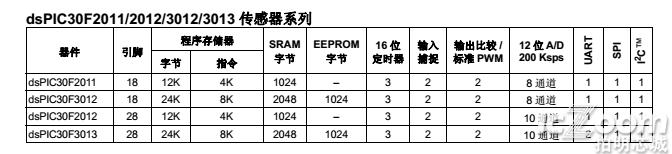

dsPIC30F2011/2012/3012/3013 传感器系列

目录

1.0 器件概述 11

2.0 CPU 架构概述 19

3.0 存储器构成 29

4.0 地址发生器单元 43

5.0 闪存程序存储器 49

6.0 数据 EEPROM 存储器 55

7.0 I/O 端口 59

8.0 中断 65

9.0 Timer1 模块 73

10.0 Timer2/3 模块 77

11.0 输入捕捉模块 83

12.0 输出比较模块 87

13.0 SPI 模块 93

14.0 I2C™ 模块 97

15.0 通用异步收发器 (UART)模块 105

16.0 12 位模数转换器(ADC)模块 113

17.0 系统集成 123

18.0 指令集汇总 137

19.0 开发支持 145

20.0 电气特性 149

21.0 封装信息 187

索引 201

Microchip 网站 207

变更通知客户服务 207

客户支持 207

读者反馈表 208

产品标识体系 209

致 客 户

我们旨在提供最佳文档供客户正确使用 Microchip 产品。 为此,我们将不断改进出版物的内容和质量,使之更好地满足您的要求。出版物的质量将随新文档及更新版本的推出而得到提升。

如果您对本出版物有任何问题和建议,请通过电子邮件联系我公司 TRC 经理,电子邮件地址为 CTRC@microchip.com,或将本数据手册后附的《读者反馈表》传真到 86-21-5407 5066。我们期待您的反馈。

最新数据手册

欲获得本数据手册的最新版本,请查询我公司的网站:

http://www.microchip.com

查看数据手册中任意一页下边角处的文献编号即可确定其版本。文献编号中数字串后的字母是版本号,例如:DS30000A是DS30000的 A 版本。

勘误表

现有器件可能带有一份勘误表,描述了实际运行与数据手册中记载内容之间存在的细微差异以及建议的变通方法。一旦我们了解到器件 / 文档存在某些差异时,就会发布勘误表。勘误表上将注明其所适用的硅片版本和文件版本。

欲了解某一器件是否存在勘误表,请通过以下方式之一查询:

•Microchip 网站:http://www.microchip.com

•当地 Microchip 销售办事处(见最后一页)

在联络销售办事处时,请说明您所使用的器件型号、硅片版本和数据手册版本 (包括文献编号)。

客户通知系统欲及时获知 Microchip 产品的最新信息,请到我公司网站 www.microchip.com 上注册。

1.0器件概述

注: 本数据手册总结了 dsPIC30F 系列器件的功能,但是不应把本手册当作无所不包的参考手册来使用。有关 CPU、外设、寄存器说明和一般器件功能的更多信息,请参见《dsPIC30F 系列参考手册》(DS70046E_CN)。有关器件指令集和编程的更多信息,请参见《16 位 MCU 和 DSC 程

序员参考手册》(DS70157E_CN)。

该数据手册包含 dsPIC30F2011、 dsPIC30F2012、 dsPIC30F3012 和 dsPIC30F3013 数字信号控制器(Digital Signal Controller, DSC)的特定信息。 dsPIC30F 系列器件在高性能 16 位单片机 (MCU)架构中融合了大量数字信号处理器 (Digital Signal Processor, DSP)功能。

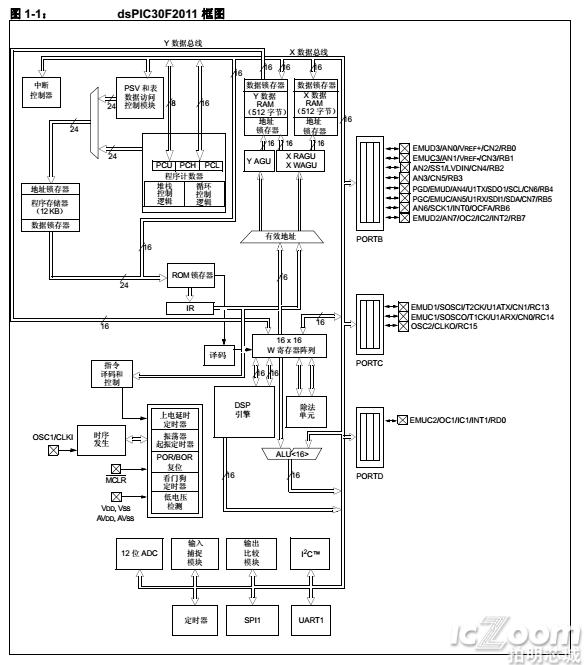

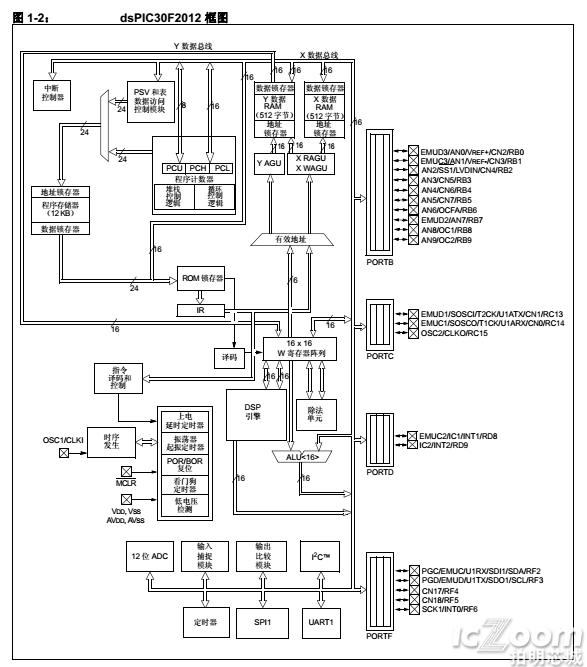

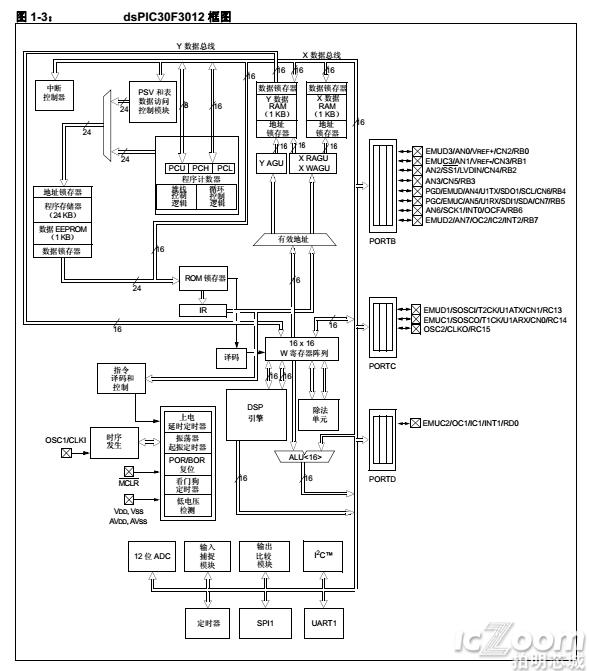

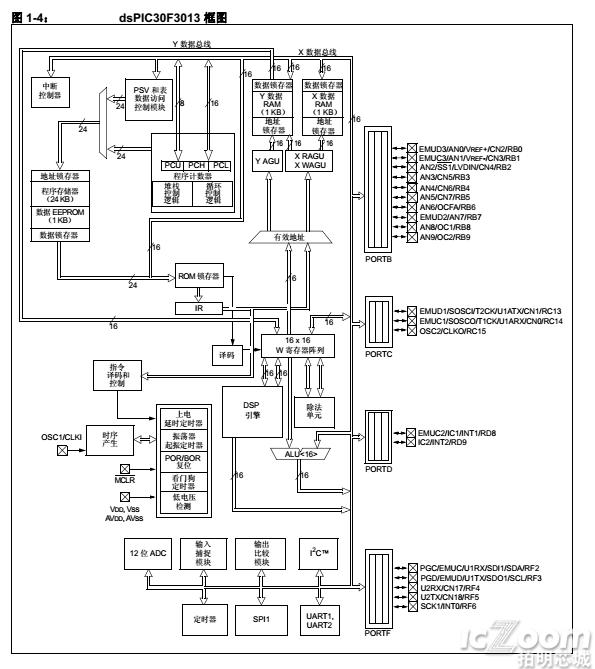

下列框图给出了 dsPIC30F 系列器件的架构:

•图 1-1 说明 dsPIC30F2011

•图 1-2 说明 dsPIC30F2012

•图 1-3 说明 dsPIC30F3012

•图 1-4 说明 dsPIC30F3013

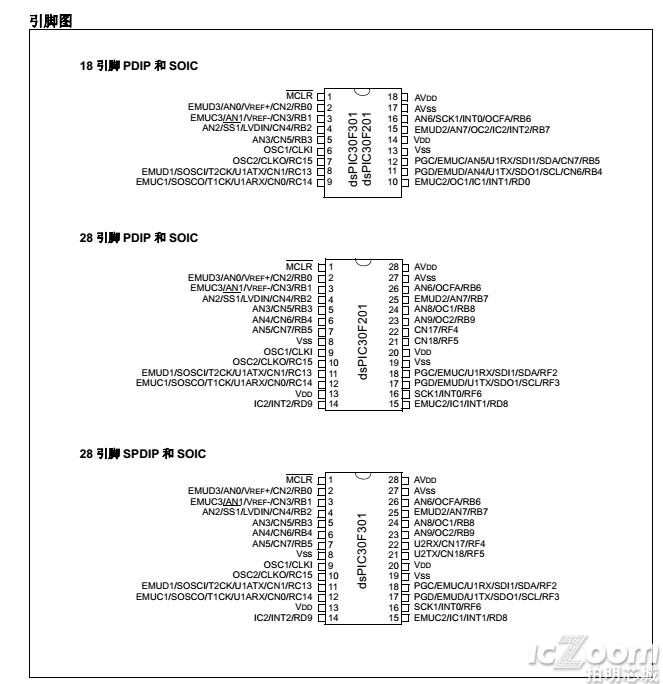

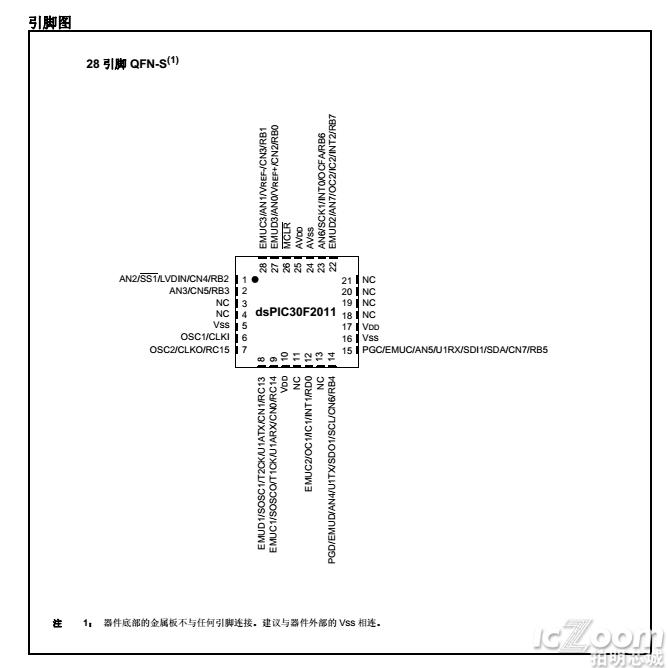

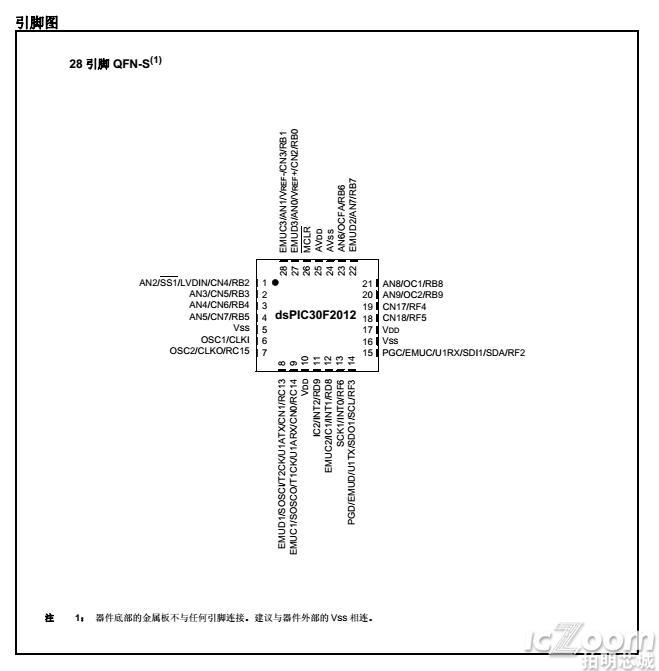

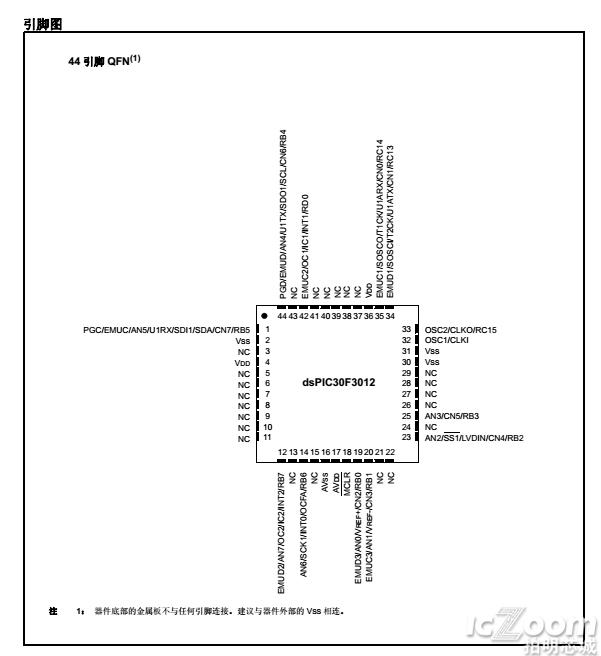

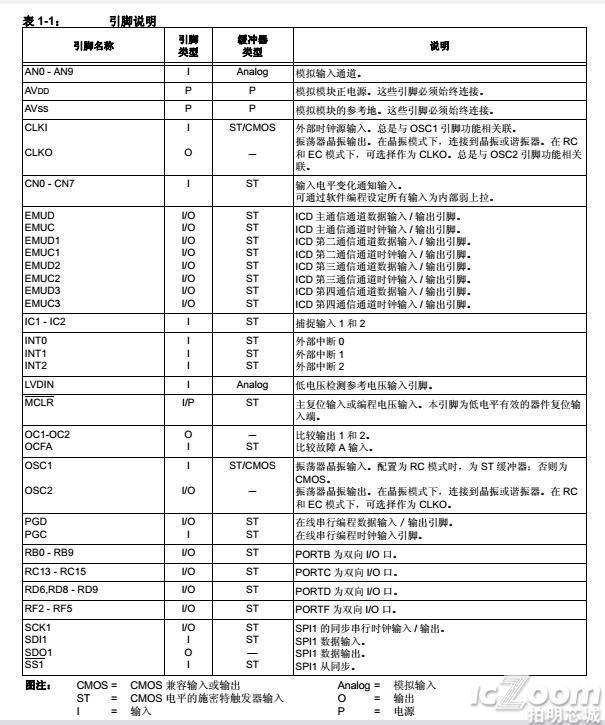

在框图后,表 1-1 给出了引脚功能信息。

表 1-1 对器件的引脚配置和端口引脚的复用功能进行了简要描述。端口引脚可具有多种功能。当发生复用时,外设模块的功能要求可强制改写端口引脚的数据方向。

2.0 CPU 架构概述

注: 本数据手册总结了 dsPIC30F 系列器件的功能,但是不应把本手册当作无所不包的参考手册来使用。有关 CPU、外设、寄存器说明和一般器件功能的更多信息,请参见《dsPIC30F 系列参考手册》(DS70046E_CN)。有关器件指令集和编程的更多信息,请参见《16 位 MCU 和 DSC 程序员参考手册》(DS70157E_CN)。

本章概述了 dsPIC30F 的 CPU 架构,其内核具有 24 位指令字。 程序计数器(PC)为 23 位宽,且最低有效位(Least Significant bit, LSb)总是处于清零状态(见第 3.1 节“程序地址空间”)。 除某些专用指令外,在 正 常 程 序 执 行 期 间,忽 略 最 高 有 效 位 (Most Significant bit,MSb)。 鉴于此,PC 最多可寻址 4M 指

令字的用户程序空间。它使用指令预取机制来帮助维持吞吐量。 使用 DO 和 REPEAT 指令支持无需循环计数管理开销的程序循环结构,这两条指令在任何时候都可被中断。

2.1 内核概述

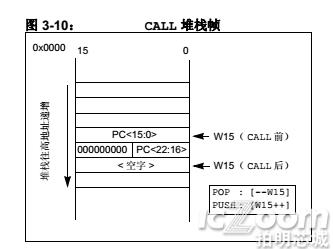

工作寄存器阵列由 16 个 16 位寄存器组成,每个工作寄存器都可以充当数据、地址或地址偏移量寄存器。 工作寄存器(W15)用作中断和调用操作的软件堆栈指针。

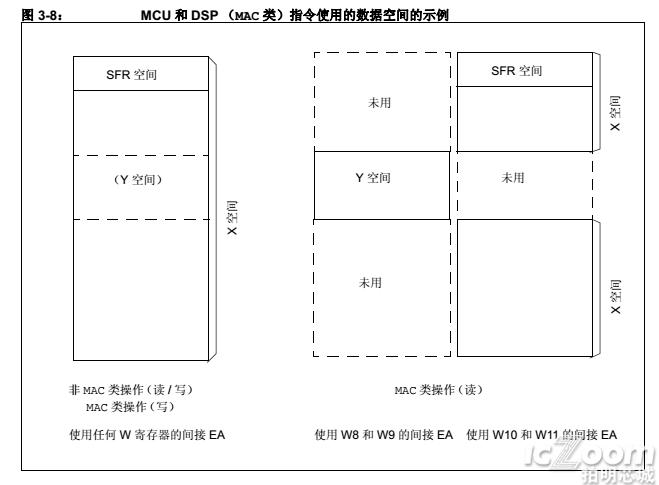

数据空间为 64 KB (32K 字),它被分成两块,分别称为 X 数据存储区和 Y 数据存储区。每个存储区都有各自独立的地址发生单元 (Address Generation Unit,AGU)。 大部分指令只通过 X 存储区 AGU 进行操作,这样对外界而言数据空间就是单独而统一的。乘-累加(MAC)类双源操作数 DSP 指令通过 X 和 Y 的 AGU 进行操作,将数据地址空间分成两个部分 (见第 3.2 节“数据地址空间”)。X 和 Y 数据空间的边界视具体器件而定,不能由用户修改。 每个数据字由 2 个字节组成,大部分指令可以按字或字节对数据进行寻址。

访问程序存储器中的数据的方法有两种:

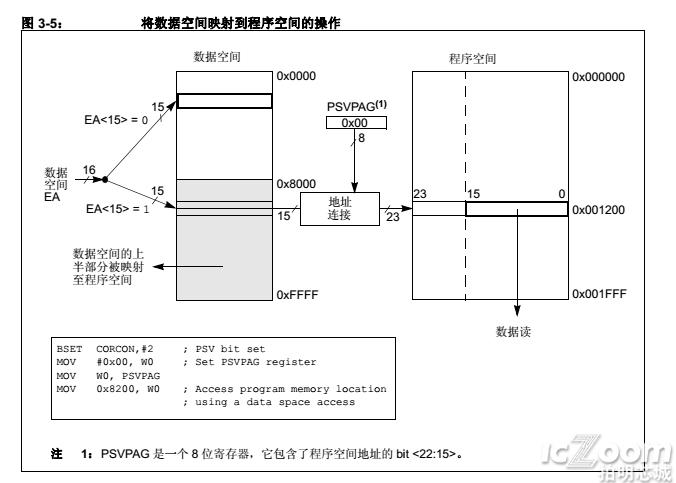

• 数据存储空间的高 32 KB 可以映射到程序空间的下半部分 (用户空间),映射的边界可以是任何 16K 程序字边界,边界由 8 位的程序空间可视性页寄存器 (PSVPAG)定义。这种映射功能让任何指令都能像访问数据空间一样访问程序空间。但访问需要额外占用一个指令周期。且使用此方法仅能访问每个指令字的低 16 位。

• 也可以通过表读 / 表写指令使用工作寄存器对程序空间内大小为 32K 字的页进行线性间接寻址。 可使用表读和表写指令访问一个指令字的所有 24 位。

X 和 Y 地址空间都支持无开销的循环缓冲区(模寻址)。模寻址主要用于减少 DSP 算法的循环开销。

X AGU 还支持对目的有效地址的位反转寻址,从而大幅简化了基 2 FFT 算法对输入或输出数据的重新排序。欲知有关模寻址和位反转寻址的详细信息,请参见第

4.0 节 “地址发生器单元”。

内核支持固有(无操作数)寻址、相对寻址、立即数寻址、存储器直接寻址、寄存器直接和寄存器间接寻址,以及寄存器偏移量和立即数偏移量寻址模式。指令根据其功能要求,与预定义的寻址模式相关。

对于大多数指令,在每个指令周期内,内核能执行一次数据 (或程序数据)存储器读操作、一次工作寄存器(数据)读操作、一次数据存储器写操作和一次程序(指令)存储器读操作。 因此,可以支持 3 操作数的指令,使 C = A + B 操作能在单周期内执行。

内核包含一个 DSP 引擎,从而能够显著增强内核的运算和吞吐能力。DSP 引擎具备一个高速 17 位 x 17 位乘

法器、一个 40 位 ALU、两个 40 位饱和累加器和一个 40 位双向桶形移位寄存器。在单个周期内,至多可将累加器或工作寄存器中的数据右移 15 位或左移 16 位。 DSP 指令可以无缝地与所有其他指令一起操作,其设计可实现最佳的实时性能。 MAC类指令可以同时从存储器中取出两个数据操作数并将两个W寄存器相乘。为了能够同时取两个数据操作数,数据空间对于这些指令拆分为两块,但对所有其他指令保持线性。对于 MAC 类指令,这是通过将某些工作寄存器专用于每个地址空间,以透明而灵活的方式实现的。

内核不支持多级指令流水线,它采用的是单级指令预取机制,该机制在执行指令的前一个周期取要执行的指令并对其部分译码,从而使可用执行时间最长。除了某些特例外,大部分指令都在一个指令周期内执行完毕。

内核具有用于处理陷阱和中断的向量异常处理结构,提供 62 个独立向量。 异常由最多 8 个陷阱 (其中 4 个保留)和 54 个中断组成。 根据用户指定的 1 到 7 之间的优先级 (1 为最低优先级, 7 为最高优先级),以及预定义的 “自然顺序”,决定每个中断的优先级。陷阱的优先级是固定的,其优先级范围是从 8 到 15。

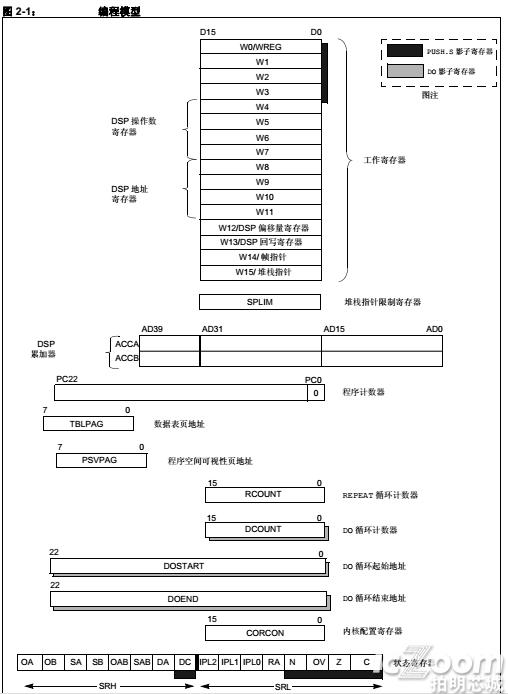

2.2 编程模型

图 2-1 为编程模型,它包括 16 个 16 位工作寄存器(W0至 W15)、 2 个 40 位累加器 (ACCA 和 ACCB)、状态寄存器(SR)、数据表页寄存器(TBLPAG)、程序空间可视性页寄存器(PSVPAG)、 DO 和 REPEAT 寄存器(DOSTART、DOEND、 DCOUNT 和 RCOUNT)

以及程序计数器(PC)。 工作寄存器可充当数据、地址或偏移量寄存器。 所有寄存器均为存储器映射。 W0 用作执行文件寄存器寻址的 W 寄存器。

其中的一些寄存器有与之关联的影子寄存器(见图 2-1)。影子寄存器被用作临时保存寄存器,它能够在事件发生时将其主寄存器中的内容送入其中或将自身内容送回主寄存器。影子寄存器都是不可直接访问的。如下指令适用于寄存器与影子寄存器间的数据传递。

• PUSH.S 和 POP.SW0、 W1、 W2、 W3 和 SR (仅限 DC、 N、OV、 Z 和 C 位)与对应的影子寄存器之间进行数据传递。

• DO 指令循环开始时, DOSTART、 DOEND 和 DCOUNT寄存器的内容压入影子寄存器,在循环结束时其内容从各自的影子寄存器中弹出。当对一个工作寄存器执行字节操作时,仅目的寄存器的低字节 (Least Significant Byte, LSB)会受到影响。但对于存储器映射的工作寄存器来说,可以通过对数据存储空间进行字节宽度的访问来对工作寄存器的低字节和高字节 (Most Significant Byte, MSB)进行操作,这一点是很有益的。

2.2.1 软件堆栈指针 / 帧指针

dsPIC® DSC 器件具有一个软件堆栈。W15 是专用的软件堆栈指针(Stack Pointer ,SP)。它可被异常处理、子程序调用和返回自动修改,并且也能够被任何指令引用 (方法与引用其他工作寄存器相同)。这样就简化了对堆栈指针的读、写和操作 (例如,创建堆栈帧)。注: 为 了 防 止 出 现 不 对 齐 的 堆 栈 访 问, W15<0> 始终保持为零。复位时 W15 被初始化为 0x0800。 在初始化期间,用户可以将 SP 重新编程以指向数据空间内的任何单元。W14 是专用的堆栈帧指针,由 LNK 和 ULNK 指令定义。并且也能够被任何指令引用(方法与引用其他工作寄存器相同)。

2.2.2 状态寄存器

dsPIC DSC 内核具有一个 16 位状态寄存器(SR),它的低字节 (LSB)被称为 SR 低字节(SRL),它的高字节(MSB)被称为 SR 高字节(SRH)。 有关 SR 的组成请参见图 2-1。

SRL 包含了所有的 MCU ALU 运算状态标志位(包括 Z 位),以及 CPU 中断优先级状态位 IPL<2:0> 和循环有效状态位 RA。在异常处理期间,SRL 与 PC 的 MSB 连在一起形成一个完整的字值,然后将该字的值压入堆栈。状态寄存器的高字节包含 DSP 加法器 / 减法器状态位、 DO 循环有效位 (DA)以及半进位 (DC)状态位。

2.2.3 程序计数器

程序计数器为 23 位宽; bit 0 总是为零。因此, PC 可寻址最多 4M 指令字。

2.3除法支持

dsPIC DSC 器件支持 16 位 /16 位有符号小数除法运算、 32 位 /16 位和 16 位 /16 位有符号和无符号整数除法运算。所有除法运算都是单指令周期内的迭代操作。 支持以下指令和数据长度:

1.DIVF — 16/16 有符号小数除法

2.DIV.sd — 32/16 有符号除法

3.DIV.ud — 32/16 无符号除法

4.DIV.s — 16/16 有符号除法

5.DIV.u — 16/16 无符号除法

16/16 除法与 32/16 除法类似(迭代次数相同),区别在于发生第一次迭代时,被除数要执行零扩展或是符号扩展。

必须在一个 REPEAT 循环周期内执行除法指令。任何其他执行方式(例如一系列不连续的除法指令)都无法得到正确的结果,因为指令流取决于 RCOUNT 的值。 除法指令本身无法自动设置 RCOUNT 值,因此必须在 REPEAT 指令中明确且正确给出该值,如表 2- 1 所示(REPEAT 将执行目标指令 {操作数的值+ 1}次)。DIV/ DIVF指令的REPEAT循环计数必须被设置为18次迭代。

因此,一个完整的除法运算需要 19 个指令周期。

注:除法流是可中断的。但用户需要正确地保护现场。

表 2-1: 除法指令

指令 功能

DIVF 有符号小数除法: Wm/Wn → W0; Rem → W1

DIV.sd 有符号除法: (Wm+1:Wm)/Wn → W0; Rem → W1

DIV.s 有符号除法: Wm/Wn → W0; Rem → W1

DIV.ud 无符号除法: (Wm+1:Wm)/Wn → W0; Rem → W1

DIV.u 无符号除法: Wm/Wn → W0; Rem → W1

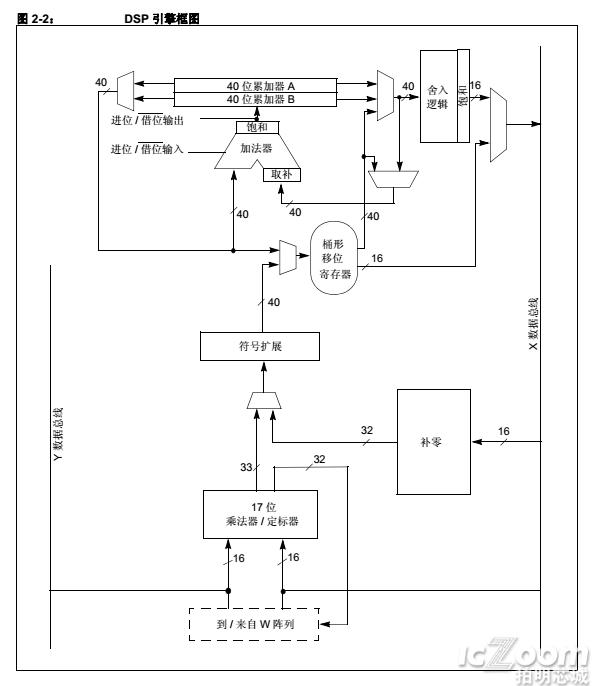

2.4 DSP 引擎

DSP 引擎由一个高速 17 位 x 17 位乘法器、一个桶形移位寄存器和一个 40 位加法器 / 减法器(带有两个目标累加器以及舍入和饱和逻辑)组成。

DSP 引擎能够执行固有的“累加器—累加器”操作,而无需额外数据。 这些指令为 ADD、 SUB 和 NEG。

dsPIC30F 采用单周期指令流架构,因此 DSP 引擎操作

和MCU指令流不能同时进行。但某些MCU ALU和DSP引擎资源可被同一条指令同时使用(如 ED 和 EDAC)。(有关 DSP 指令见表 2-2)。

通过 CPU 内核配置寄存器(CORCON)的不同位可以选择 DSP 引擎的几种功能,如下所示:

1. 小数或整数 DSP 乘法 (IF)。

2. 有符号或无符号 DSP 乘法 (US)。

3. 常规或收敛舍入 (RND)。

4. ACCA 自动饱和使能 / 禁止 (SATA)。

5. ACCB 自动饱和使能 / 禁止 (SATB)。

6. 用于写数据存储器的自动饱和使能/禁止(SATDW)。

7. 累加器饱和模式选择 (ACCSAT)。

注: 请参见表 3-3 了解 CORCON 的组成。

图 2-1 给出了 DSP 引擎的框图。

2.4.1 乘法器

17位 x 17位的乘法器可以进行有符号或无符号的运算,其输出经过定标器进行换算后可支持 1.31 小数(Q31或 32 位整数结果。无符号操作数经过零扩展后,送入乘法器输入值的第 17 位。有符号操作数经过符号扩展,送入乘法器输入值的第 17 位。17 位 x 17 位乘法器 / 定标器的输出是 33 位值,它将被符号扩展为 40 位。 整型数据的固有表示形式为有符号的二进制补码值,其中, MSb 定义为符号位。一般来说,N 位二进制补码整数的范围为 -2N-1 到 2N-1 – 1。对于 16 位整数,数据范围是 -32768 (0x8000) 至 32767 (0x7FFF),包括 0 在内。对于 32 位整数,数据范围是 -2,147,483,648 (0x8000 0000) 至 2,147,483,645 (0x7FFF FFFF)。

当乘法器配置为小数乘法时,数据表示为二进制补码小数,其中 MSb 定义为符号位,小数点暗含在符号位之后 (QX 格式)。暗含小数点的 N 位二进制补码小数的范围是 -1.0 至(1 – 21-N)。对于 16 位小数, Q15 数据范围是 -1.0 (0x8000)至 0.999969482(0x7FFF),包括 0 在内,其精度为 3.01518x10-5。在小数方式下,16x16 乘法运算将产生 1.31 乘积,其精度为 4.65661 x10-10。同一个乘法器还用来支持 MCU 乘法指令,包括整数的 16 位有符号、无符号和混和符号乘法。MUL 指令可以使用字节或字长度的操作数。字节操作数将产生 16 位结果,而字操作数将产生 32 位结果,结果存放在 W 寄存器阵列的指定寄存器中。

2.4.2 数据累加器和加法器 / 减法器

数据累加器具有一个带有自动符号扩展逻辑的 40 位加法器 / 减法器。它可以选择两个累加器 (A 或 B)之一作为它累加前的源和累加后的目标。对于 ADD 和 LAC 指令,可选择通过桶形移位器在累加之前对将被累加或装入的数据进行换算。

2.4.2.1 加法器 / 减法器、溢出和饱和

加法器 / 减法器为一个 40 位的加法器,一侧输入可以选择为零,而另一侧的输入可以是数据的原码或补码。对于加法, 进位 / 借位输入是高有效的,另一侧输入是数据的原码(没有求补的);对于减法,进位 / 借位输入是低有效的,另一侧输入是数据的补码。由状态寄存器中的 SA/SB 和 OA/OB 提供加法器 / 减法器的溢出状态:

• 从 bit 39 溢出:这是一种灾难性的溢出,因为它破坏了累加器的符号位。

• 溢出到警戒位 bit 32 至 bit 39:这是一种可恢复的溢出。 这些警戒位不完全相同时,该位置 1。加法器有一个额外的饱和模块,如果选用该模块将控制累加器的数据饱和。 饱和模块使用加法器的结果、上一段所述的溢出状态位以及模式控制位 SATA/(CORCON<7:6>)和 ACCSAT(CORCON<4>)来决定何时以及在何值达到饱和。在状态寄存器中有 6 个支持饱和及溢出的位, 它们是:

• OA:ACCA 溢出至警戒位

• OB: ACCB 溢出至警戒位

• SA:ACCA 已饱和(bit 31 溢出并饱和)或ACCA 溢出至警戒位并饱和(bit 39 溢出并饱和)

• SB:ACCB 已饱和(bit 31 溢出并饱和)或ACCB 溢出至警戒位并饱和(bit 39 溢出并饱和)

• OAB:OA 和 OB 的逻辑或 (OR)

• SAB:SA 和 SB 的逻辑或 (OR)每次数据通过加法器 / 减法器,就会修改 OA 位和 OB位。 置 1 时,它们表明最近的运算已经溢出到累加器警戒位 (bit 32 到 bit 39)。 如果 OA 和 OB 位置 1 而且INTCON1 寄存器中相应的溢出陷阱允许位(OVATE 和OVBTE)也置 1 的话,还可以选择用 OA 和 OB 位产生算术警告陷阱 (见第 8.0 节 “中断”)。 这使得用户能够立即采取措施,例如校正系统增益。

每次数据通过加法器 / 减法器,就会修改 SA 和 SB 位,但它们只能由用户清零。 置 1 时,它们表明累加器已经溢出其最大范围 (32 位饱和是 bit 31,而 40 位饱和是bit 39),将发生饱和(如果饱和使能的话)。 如果没有使能饱和,SA 和 SB 置 1 默认为 bit 39 溢出,即表明发生灾难性溢出。 如果 INTCON1 寄存器中的 COVTE 位置 1,当饱和被禁止时,SA 和 SB 位将产生算术警告陷阱。

可选择将状态寄存器中的溢出和饱和状态位分别视作 OA 和 OB 的逻辑或 (OAB 位)以及 SA 和 SB 的逻辑或(SAB 位)。 这样,只需要检查状态寄存器中的一个位,编程人员就能够判断出是否有累加器溢出;检查状态寄存器中另一个位就能判断出是否有累加器饱和。对于通常需要使用两个累加器的复数运算而言,这很有用。器件支持三种饱和及溢出模式:

1. Bit 39 溢出和饱和:当发生 bit 39 溢出和饱和时,饱和逻辑将最大的正数 9.31 (0x7FFFFFFFFF)或最小的负数 -9.31值(0x8000000000)装入目标累加器。SA 或 SB位被置 1 且保持置 1 状态,直至被用户清零。 这称为 “超饱和” ,为错误数据或不可预期的算法问题(例如,增益计算)提供了保护机制。

2. Bit 31 溢出和饱和:当发生 bit 31 溢出和饱和时,饱和逻辑将最大的正数 1.31 (0x007FFFFFFF)或最小的负数 -1.31 (0x0080000000)装入目标累加器。SA 或 SB 位被置 1 且保持置 1 状态,直至被用户清零。 当此饱和模式生效时,不使用警戒位,因此 OA、 OB或 OAB 位永远不会置 1。

3. Bit 39 灾难性溢出:加法器的 bit 39 溢出会将 SA 或 SB 位置 1 并保持该状态直至被用户清零。不执行饱和操作,允许累加器溢出 (破坏累加器的符号位)。 如果INTCON1 寄存器中的 COVTE 位置 1,则灾难性溢出可能引发陷阱异常。

2.4.2.2 累加器 “ 回写”MAC 类指令(MPY、 MPY.N、 ED 和 EDAC 除外)可以选择将累加器高位字 (bit 16 至 bit 31)的舍入形式写入数据存储空间,前提是当前指令不对该累加器进行操作。 通过 X 总线将数据写入组合的 X 和 Y 地址空间来执行此回写操作。 支持下列寻址模式:

1. W13,寄存器直接寻址:非目标累加器的舍入内容以 1.15 小数形式写入W13。

2. [W13] + = 2,带后递增的寄存器间接寻址:非目标累加器的舍入内容以 1.15 小数形式写入 W13 指向的地址。 W13 的值递增 2 (对于字写操作)。

2.4.2.3 舍入逻辑舍入逻辑为一个组合的模块,在累加器写(存储)过程中可以执行常规的(有偏)或收敛的(无偏)舍入功能。 由 CORCON 寄存器的 RND 位的状态决定舍入模

式。 它会产生一个 16 位的 1.15 数据值,该值被送入到数据空间写饱和逻辑。 如果指令没有明确指定舍入,那么将会存储一个截取的 1.15 数据值而只丢弃低位字(lsw)。

常规舍入取累加器 bit 15 的值,对其进行零扩展并将扩展值加到 ACCxH 字(累加器的 bit 16 至 bit 31) 。 如果 ACCxL 字(累加器的 bit 0 至 bit 15)的值在 0x8000 到 0xFFFF (含 0x8000)之间, ACCxH 的值递增 1。如果 ACCxL 字的值在 0x0000 到 0x7FFF 之间,ACCxH的值不变。 此算法的结果经过一系列随机舍入操作,值将稍稍偏大 (正偏)。收敛(或无偏)舍入操作与常规舍入操作相同,但 ACCxL 等于 0x8000 时例外。 在此种情况下,检查 ACCxH 的最低位(累加器的 bit 16)。 如果该位为 1, ACCxH 的值增 1。 如果该位为 0, ACCxH 的值不变。假设 bit 16 本身就是一个随机数,那么此机制将消除任何可能累加的舍入偏差。

SAC和 SAC.R指令通过 X总线将目标累加器内容的截取值(SAC)或舍入值(SAC.R)存储到数据存储空间。(受数据饱和的影响,见第 2.4.2.4 节 “数据空间写饱和”)。 注意对于 MAC 类指令,累加器回写操作以相同的方式工作,通过 X 总线访问组合的 MCU (X 和 Y)数据空间。 对于此类指令,总是对数据进行舍入。

2.4.2.4 数据空间写饱和

除加法器 / 减法器会饱和外,写数据空间也会饱和但不影响源累加器的内容。数据空间写饱和逻辑模块接受一个来自舍入逻辑模块的 16 位 1.15 小数值作为其输入,还接受来自源 (累加器)和 16 位舍入加法器的溢出状态。这些经过组合,用来选择恰当的 1.15 小数值作为输出,写入至数据存储空间中。如果 CORCON 寄存器的 SATDW 位置 1,则检测数据(舍入和截取后的值)是否溢出并作相应调整。 针对大于 0x007FFF 的输入数据,写入存储器的数据被强制为最大的1.15值形式的正数0x7FFF。针对小于0xFF8000的输入数据,写入存储器的数据被强制为最大的 1.15 值形式的负数 0x8000。源累加器的最高位(bit 39)用来决定被检测的操作数的符号。如果 CORCON 寄存器中的 SATDW 位没有置 1,则输入数据都将通过,在任何情况下都不会被修改。

2.4.3 桶形移位器

桶形移位寄存器在单个周期内可将数据逻辑或算术右移或左移最多 16 位。源操作数可为两个 DSP 累加器之一或 X 总线(以支持对寄存器或存储器中的数据进行多位移位)。移位寄存器需要一个有符号二进制值来确定移位操作的方向和幅度(位的数量)。 正数将操作数右移。 负数将操作数左移。 0 值不改变操作数。桶形移位寄存器是 40 位宽的,于是,它为 DSP 移位操作提供了 40 位的结果,而为 MCU 移位操作提供 16 位的结果。来自 X 总线的数据在桶形移位寄存器中的存放方式是:右移则数据存放在 bit 16 至 bit 31,左移则存放在 bit 0 至 bit 15。

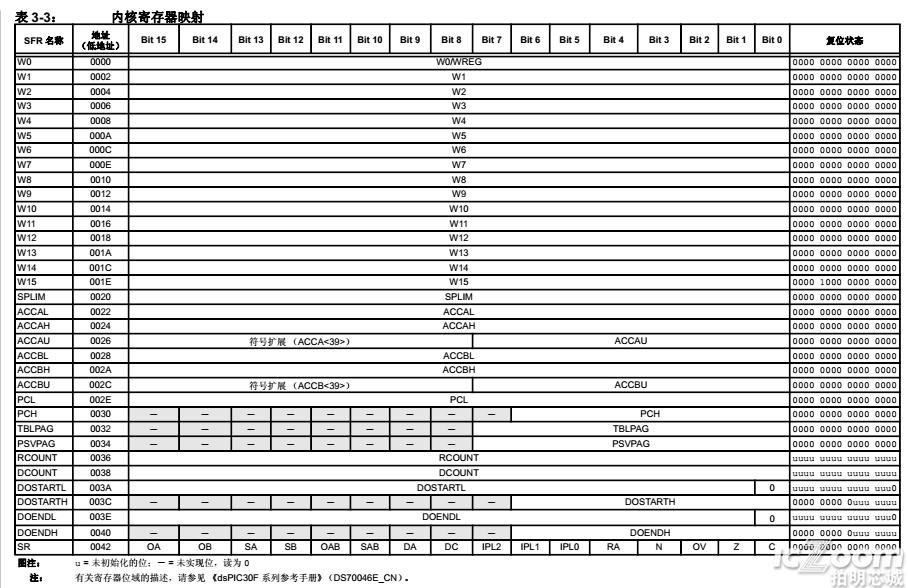

3.0存储器构成

注: 本数据手册总结了 dsPIC30F 系列器件的功能,但是不应把本手册当作无所不包的参考手册来使用。 有关 CPU、外设、寄存器说明和一般器件功能的更多信息,请参见 《dsPIC30F 系列参考手册》(DS70046E_CN) 。 有关器件指令集和编程的更多信息,请参见 《16 位 MCU 和 DSC 程序员参考手册》(DS70157E_CN)。

3.1程序地址空间

程序地址空间为 4M 指令字。dsPI30F2011/2012/3012/ 3013 器件的程序存储空间映射如图 3-1 所示。

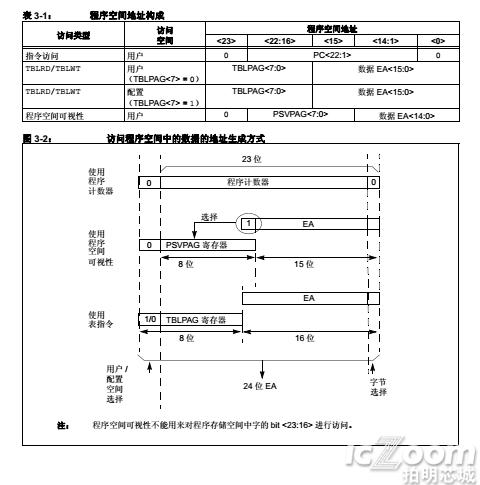

当程序空间按表 3-1 中的定义映射到数据空间时,可由来自 23 位 PC、表指令有效地址 (Effective Address,EA)或数据空间 EA 的 24 位值寻址。注意在访问连续的程序字时,程序空间地址应该增 2 以与数据空间寻址相一致。用户只能访问程序存储空间的低 4M 指令字(地址范围为 0x000000 至 0x7FFFFE);使用 TBLRD/TBLWT 指令时情况有所不同,这两条指令使用 TBLPAG<7> 来确定访问用户空间还是配置空间。 在表 3-1 (程序空间地址构成)中,bit 23 为 1 允许访问器件 ID、用户 ID 和配置位。 否则, bit 23 总是处于清零状态。

3.1.1使用表指令访问程序存储器中的数据

由于此类器件的架构对24位宽的程序存储器取指。因此指令始终是对齐的。由于采用的是改进的哈佛架构,因此也可以在程序空间中存储数据。访问程序空间的方法有2种:通过特殊表指令,或通过将16K字大小的程序空间页重映射到数据空间的上半部分(见第3.1.2节“使用程序空间可视性访问程序存储器中的数据”)。TBLRDL和TBLWTL指令提供了无需通过数据空间,直接读写程序空间任何地址的低位字(lsw)的方法,TBLRDH和TBLWTH指令是可以把一个程序空间字的最高8位作为数据存取的惟一方法。

要访问两个连续的24位程序字,PC的递增量为2。这使得程序存储器地址能够被直接映射到数据空间地址中。于是,程序存储器可以被看作是两个16位字宽的地址空间,它们并排放置且具有相同的地址范围。TBLRDL和TBLWTL访问包含数据低位字的空间,TBLRDH和TBLWTH访问包含数据最高字节的空间。

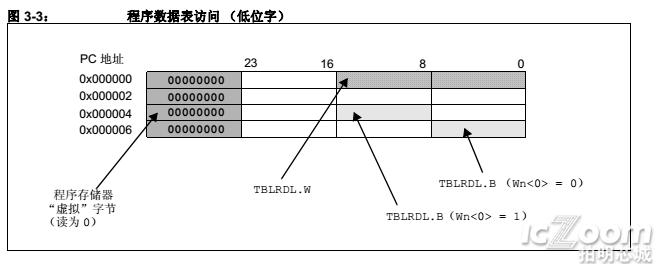

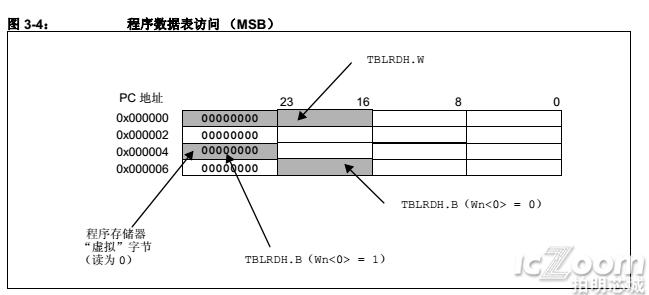

图3-2给出了表操作和数据空间访问(PSV=1)时EA的构成方式。在该图中,P<23:0>指程序空间字,而D<15:0>指数据空间字。提供了一组表指令,可使用它们来在程序空间和数据空间之间传送字节或字大小的数据(见图3-3和图3-4)。

1.TBLRDL:对低位字执行表读操作字:读程序地址的低位字;P<15:0>映射到D<15:0>。

字节:读程序地址的某个较低的字节;当字节选择位=0时,P<7:0>映射到目标字节;当字节选择位=1时,P<15:8>映射到目标字节。

2.TBLWTL:对低位字执行表写操作(有关闪存编程的详细信息见第5.0节“闪存程序存储器”)

3.TBLRDH:对高位字执行表读操作字:读程序地址的高位字;P<23:16>映射到D<7:0>;D<15:8>将始终为零(=0)。

字节:读程序地址的某个较高的字节;当字节选择位=0时,P<23:16>映射到目标字节;当字节选择位=1时,目标字节将始终为零(=0)。

4.TBLWTH:对高位字执行表写操作(有关闪存编程的详细信息见第5.0节“闪存程序存储器”)

3.1.2 使用程序空间可视性访问程序存储器中的数据可选择将数据空间的高 32 KB 映射到任何 16K 字程序空间页。这提供了对存储在 X 数据空间的常量数据的透明访问,而无需使用特殊指令(即 TBLRDL/H 和 TBLWTL/H 指令)。如果数据空间 EA 的最高位置 1,且通过将内核控制寄存器(CORCON)中的 PSV 位置 1 使能程序空间可视性,就可以通过数据空间访问程序空间。第2.4节“DSP引擎”中对 CORCON 的功能进行了讨论。访问此区域的数据会增加一个额外的指令周期,因为需要进行两次程序存储空间取操作。

注意,可寻址数据空间的上半部分始终位于 X 数据空间内。 因此,当 DSP 操作使用程序空间映射来访问这个存储区域时,Y 数据空间通常应该存放 DSP 操作的状态(变量)数据,而 X 数据空间通常应该存放系数(常量)数据。尽管大于等于 0x8000 的每个数据空间地址直接映射到对应的程序存储器地址(见图 3-5),但只使用 24 位程序字的低 16 位来存储数据。 应对高 8 位进行编程强制使得对其的访问为非法以维持器件的可靠性。有关指令编码的细节,请参见 《16 位 MCU 和 DSC 程序员参考手册》(DS70157E_CN)。注意,每访问一个程序存储字, PC 就会递增 2,数据空间地址的低 15 位直接被映射到相应程序空间地址的低 15 位。其余位由程序空间可视性页寄存器(PSVPAG<7:0>)提供,如图 3-5 所示。

注: 在表读 / 写操作时暂时禁止 PSV 访问。对于在 REPEAT 循环外执行的使用 PSV 的指令:

• 以下指令除规定的执行时间外还需一个额外的指令周期:

- 带数据操作数预取操作的 MAC 类指令

- MOV 指令

- MOV.D 指令

• 所有其他指令除规定的执行时间外还需两个额外的指令周期。对于在 REPEAT 循环内执行的使用 PSV 的指令:

• 以下指令除规定的执行时间外还需两个额外的指令周期:

- 在第一次迭代时执行的指令

- 在最后一次迭代时执行的指令

- 在由于中断而退出循环前执行的指令

- 中断被处理后,在重新进入循环时执行的指令

• 对于在 REPEAT 循环的任何其他迭代中使用 PSV 访问数据的指令,其执行时间为一个周期。

3.2 数据地址空间

内核具有两个数据空间。可将这两个数据空间视为两个独立的空间 (对于某些 DSP 指令)或是一个统一的线性寻址空间(对于 MCU 指令)。 使用两个地址发生单元(AGU)和相互独立的数据路径对这两个数据空间进行访问。

3.2.1 数据存储空间

映射数据存储空间被分为两大块,它们是 X 数据空间和 Y 数据空间。 该架构的关键之处在于 Y 空间是 X 空间的子集,它完全包含在 X 空间内。 要提供一种表面看似线性的寻址空间, X 空间和 Y 空间需要具有连续的地址。执行 MAC 类指令以外的任何指令时,X 空间由 64 KB 数据地址空间 (包括了全部的 Y 空间地址)组成。 执行MAC类指令时,X块由不包括Y地址块(只用于数据读操作)的 64 KB 数据地址空间组成。 也就是说,所有其他指令将整个数据存储空间视作一个组合的地址空间。MAC 类指令把 Y 地址空间从数据空间中分离出来,并使用来自 W10 和 W11 的 EA 对 Y 空间寻址。使用 W8 和W9 对剩余的 X 数据空间寻址。只有通过 MAC 类指令才能同时访问这两个地址空间。

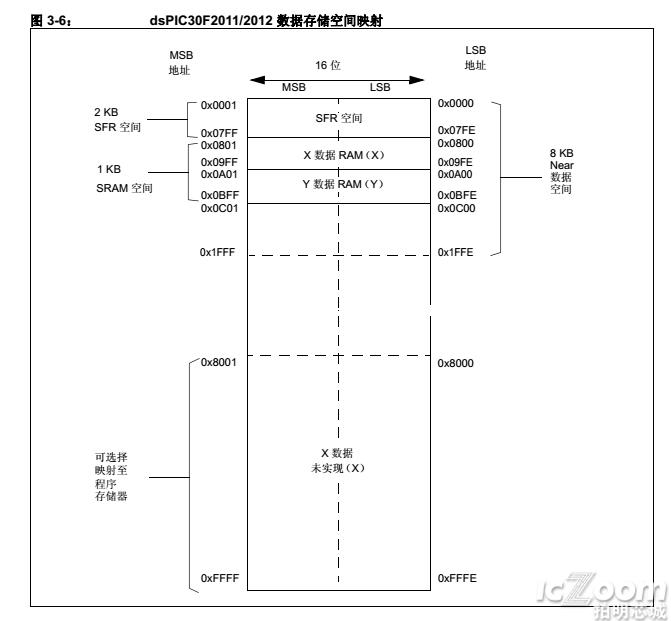

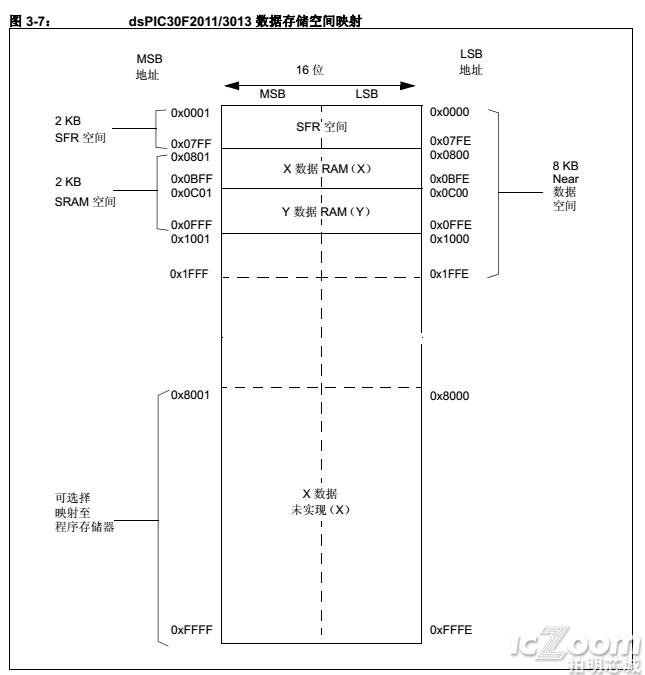

dsPI30F2011/2012 的数据存储空间映射如图 3-6 所示。

dsPI30F2012/2013 的数据存储空间映射如图 3-7 所示。

3.2.2 数据空间

X 数据空间可被所有指令使用且支持所有寻址模式。 其读写数据总线是相互独立的。 X 读数据总线是所有将数据空间视为一个组合的 X 和 Y 地址空间的指令的数据返回路径。 它也是双操作数读指令(MAC 类)的 X 地址空间数据路径。 X 写数据总线是所有指令对数据空间执行写操作的惟一路径。

X 数据空间还支持所有指令的模寻址,但是会受到寻址模式的限制。只有写 X 数据空间的操作才支持位反转寻址方式。

MAC 类指令(CLR、ED、EDAC、MAC、MOVSAC、MPY、 MPY.N 和 MSC)配合使用 Y 数据空间与 X 数据空间以提供两条可以同时读取数据的路径。不能通过Y总线执行任何写操作。此类指令专门指定 W10 和 W11 始终作为寻址 Y 数据空间的 W 寄存器指针,独立于 X 数据空间;而指定 W8 和 W9 作为寻址 X 数据空间的 W 寄存器指针。注意,在累加器回写操作期间,数据地址空间被认为是一个组合的 X 和 Y 数据空间,因此写操作通过 X 总线进行。从而可以对整个地址空间中的任何地址单元执行写操作。

Y 数据空间仅用于与 MAC 类指令相关的数据预取操作。它也支持对自动循环缓冲区的模寻址。 当然,所有其他指令可通过将 Y 数据地址空间视作组合线性空间的一部分,通过 X 数据总线对其进行访问。

图 3-7 给出了 X 和 Y 数据空间之间的边界定义,用户不能通过编程更改 X 和 Y 的数据空间边界。如果 EA 指向已为其分配的数据空间之外的数据或是指向物理存储器之外的存储单元,则将返回全零的字或字节。 例如,虽然所有使用任何寻址模式的非 MAC 类指令都能访问 Y 地址空间,但如果一条 MAC 类指令试图使用 W8 或 W9 (X 空间指针)从 Y 地址空间取数据,将返回 0x0000。

所有有效地址均为16位宽,指向数据空间中的字节。因此,数据空间的地址范围为 64 KB 或 32K 字。

3.2.3 数据空间宽度

内核数据宽度为 16 位。所有内部寄存器都是以 16 位宽字构成的。 数据存储空间以字节可寻址的 16 位宽的块构成。

3.2.4 数据对齐

为了保持与 PIC® MCU 器件的向后兼容以及提高数据存储空间的使用效率, dsPIC30F 指令集既支持字操作,也支持字节操作。 在数据存储器和寄存器中,数据是按字对齐的,但所有数据空间有效地址都被解析为字节。使用有效地址的最低位(LSb)决定要选择哪个字节,读数据字节的操作将读取包含此字节的整个字。选中的字节将被放在 X 数据总线的 LSB 中(不可能出现来自Y数据路径的字节访问,因为MAC类指令只能取整字)。也就是说,数据存储器和寄存器是由两个共享(字)地址译码,而写入线相互独立的字节宽度的并行实体构成的。数据字节写操作仅写入存储阵列或寄存器中与字节地址匹配的那一侧。

这种字节访问操作可使所有的有效地址计算(包括那些由 DSP 操作产生的有效地址,它们只能是字长度的数据)在内部进行换算,以适应字对齐的存储空间。例如,内核将识别执行后修改寄存器间接寻址模式 [Ws++] 的结果,对于字节操作产生的值是 Ws + 1,而对于字操作产生的值是 Ws + 2。所有字访问必须按偶地址对齐。不支持取不对齐的字数据的操作,因此在混合使用字节和字的操作或移植 8 位 MCU 代码时应该小心。 任何尝试进行非对齐读或写的操作都将产生地址错误陷阱。 如果在读操作时产生错误,正在执行的指令将完成;如果在写操作时产生错误,指令仍将执行,但不会进行写入。 无论上述 2 种情况的哪一种,都将产生陷阱,从而允许系统与 / 或用户检查地址错误发生之前的机器状态。

所有载入 W 寄存器的字节都将载入 W 寄存器的 LSB, W 寄存器的 MSB 不变。提供了一条符号扩展 (SE)指令,允许用户把 8 位的有符号数据转换为 16 位有符号值。或者,对于 16 位无符号数据,用户可以清零任何 W 寄存器的 MSB,方法是在相应的地址处执行一条零扩展 (ZE)指令。尽管大多数指令能够对字或字节大小的数据进行操作,但应该注意的是,一些指令,包括 DSP 指令,只对字大小的数据进行操作。

3.2.5 NEAR 数据空间

X 地址存储空间中,在 0x0000 和 0x1FFF 之间保留了一个 8 KB 的 near 数据空间;在所有的存储器直接寻址指令中,可以通过一个 13 位的绝对地址字段来直接访问这个数据空间。其余的 X 地址空间和全部的 Y 地址空间都是可间接寻址的。此外,使用 MOV 指令可以寻址整个 X 数据空间,这支持通过 16 位地址字段进行存储器直接寻址。

3.2.6 软件堆栈

dsPIC DSC 器件具有一个软件堆栈。 W15 被用作堆栈指针。堆栈指针总是指向堆栈顶部第一个可供使用的字,从低地址到高地址方向增长。堆栈指针在弹出堆栈之前递减,而在压入堆栈后递增,如图 3-10 所示。注意,对于任何 CALL 指令时的 PC 压栈,在压入堆栈之前, PC 的MSB要进行零扩展,从而确保了MSB始终是清零的。注: 在异常处理期间,在将 PC 压入堆栈之前,要先将 PC 的 MSB 与 SRL 寄存器组合在一起。

堆栈指针限制寄存器(SPLIM)与堆栈指针相关联。复位时 SPLIM 不被初始化。 与堆栈指针的情况一样,因为所有的堆栈操作必须是字对齐的,SPLIM<0> 被强制为 0。 每当使用 W15 作为源或目标指针生成有效地址(EA)时,生成的地址要与 SPLIM 中的值做比较。 如果堆栈指针 (W15)与 SPLIM 寄存器的内容相等,则执行压栈操作,此时不会产生堆栈错误陷阱。 但在随后的压栈操作中会产生堆栈错误陷阱。这样的话,当堆栈增长超过 RAM 中地址 0x2000 时,如果要想产生堆栈错误陷阱,用值 0x1FFE 来初始化 SPLIM 即可。类似地,当堆栈指针地址小于 0x0800 时,就会产生堆栈指针下溢(堆栈错误)陷阱,这避免了堆栈进入特殊功能寄存器 (SFR)空间。对 SPLIM 寄存器执行写操作之后,不要立即使用 W15 对该寄存器执行间接读操作。

4.0 地址发生器单元

注: 本数据手册总结了 dsPIC30F 系列器件的功能,但是不应把本手册当作无所不包的参考手册来

使用。有关 CPU、外设、寄存器说明和一般器件功能的更多信息,请参阅《dsPIC30F系列参考手册》(DS70046E_CN)。有关器件指令集和编程的更多信息,请参阅《16 位 MCU 和 DSC 程序员参考手册》(DS70157E_CN)。dsPIC DSC 内核包含两个独立的地址发生器单元: X AGU 和 Y AGU。Y AGU 仅支持 DSP MAC 类指令的字长度数据读取。 dsPIC DSC AGU 支持如下三种数据寻址类型 :

• 线性寻址

• 模 (循环)寻址

• 位反转寻址线性和模数据寻址模式可应用于数据空间或程序空间。位反转寻址只能用于数据空间地址。

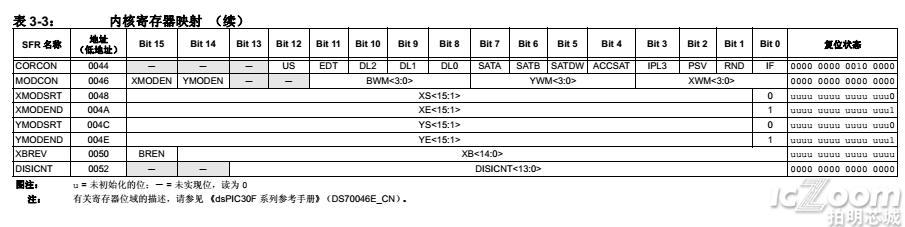

4.1 指令寻址模式

寻址模式经过优化可以支持各指令的具体功能,基本的寻址模式在表 4-1 中给出。MAC 类指令中提供的寻址模式,与其他指令类型中的寻址模式略有不同。

4.1.1 文件寄存器指令

大多数文件寄存器指令使用一个 13 位地址字段(f)来直接寻址数据存储器中的前 8192 字节 (near 数据空间)。大多数文件寄存器指令使用工作寄存器 W0,W0在这些指令中表示为 WREG。目的寄存器通常是同一个文件寄存器或者 WREG(MUL 指令除外),把结果写入寄存器或寄存器对。使用 MOV 指令能够获得更大的灵活性,在文件寄存器操作期间可以访问整个数据空间。

4.1.2 MCU 指令

三操作数 MCU 指令的形式是:操作数 3 = 操作数 1< 函数 > 操作数 2其中,操作数 1 始终是工作寄存器(即,寻址模式只能是寄存器直接寻址),称为 Wb。操作数 2 可以是一个 W 寄存器,取自数据存储器或一个 5 位立即数。结果位置可以是 W 寄存器或地址单元。MCU 指令支持下列寻址模式:

• 寄存器直接寻址

• 寄存器间接寻址

• 执行后修改的寄存器间接寻址

• 执行前修改的寄存器间接寻址

• 5 位或 10 位立即数寻址

注:并非所有的指令都支持上面给出的全部寻址模式。各条指令可能支持这些寻址模式的某些模式,指令不同支持的寻址模式可能不同。

4.1.3 传送指令和累加器类指令

与其他指令相比,传送指令和 DSP 累加器类指令提供了更为灵活的寻址模式。除了大多数 MCU 指令支持的寻址模式以外,传送和累加器类指令还支持带寄存器偏移量的寄存器间接寻址模式,这也叫做寄存器变址寻址模式。

注: 对于 MOV 指令,指令中指定的寻址模式对于源寄存器和目的寄存器 EA,可以是不同的。然而,4 位 Wb(寄存器偏移量)字段为源寄存器和目的寄存器所共用 (但通常只由源寄存器或目的寄存器之一使用)。概括地说,传送指令和累加器指令支持下列寻址模式:

• 寄存器直接寻址

• 寄存器间接寻址

• 执行后修改的寄存器间接寻址

• 执行前修改的寄存器间接寻址

• 寄存器偏移量的寄存器间接寻址 (变址寻址)

• 立即数偏移量的寄存器间接寻址

• 8 位立即数寻址

• 16 位立即数寻址

注:并非所有的指令都支持上面给出的全部寻址模式。各条指令可能支持这些寻址模式的某些模式,指令不同支持的寻址模式可能不同。

4.1.4 MAC 类指令

双源操作数 DSP 指令(CLR、ED、EDAC、MAC、MPY、MPY.N、MOVSAC 和 MSC)也叫做 MAC 类指令,它们使用一组简化的寻址模式,允许用户通过寄存器间接寻址表有效地对数据指针进行操作。双源操作数预取寄存器必须是集合 {W8, W9, W10,W11} 的成员。对于数据读取操作,W8 和 W9 始终用于X RAGU, 而 W10 和 W11 始终用于 Y AGU。从而,产生的有效地址(无论是在修改之前还是之后),对于 W8 和 W9 必须是 X 数据空间中的有效地址,对于 W10 和 W11 则必须是 Y 数据空间中的有效地址。注: 带寄存器偏移量的寄存器间接寻址,仅可用于 W9 (在 X 空间中)和 W11 (在 Y 空间中)。

概括地说, MAC 类指令支持下列寻址模式:

• 寄存器间接寻址

• 执行后修改 (修改量为 2)的寄存器间接寻址

• 执行后修改 (修改量为 4)的寄存器间接寻址

• 执行后修改 (修改量为 6)的寄存器间接寻址

• 寄存器偏移量的寄存器间接寻址 (变址寻址)

4.1.5 其他指令

除了上述的各种寻址模式之外,一些指令使用各种长度的立即数常量。例如, BRA (转移)指令使用 16 位有符号立即数来直接指定转移的目标,而 DISI 指令使用一个 14 位无符号立即数字段。在一些指令中,比如 ADD Acc,操作数的来源或运算结果已经暗含在操作码中。某些操作,比如 NOP,没有任何操作数。

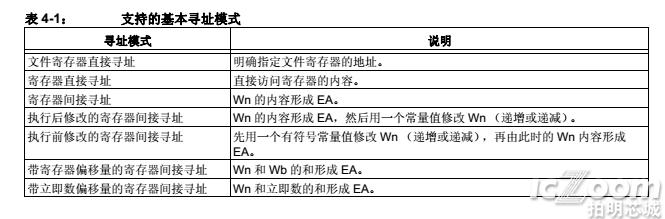

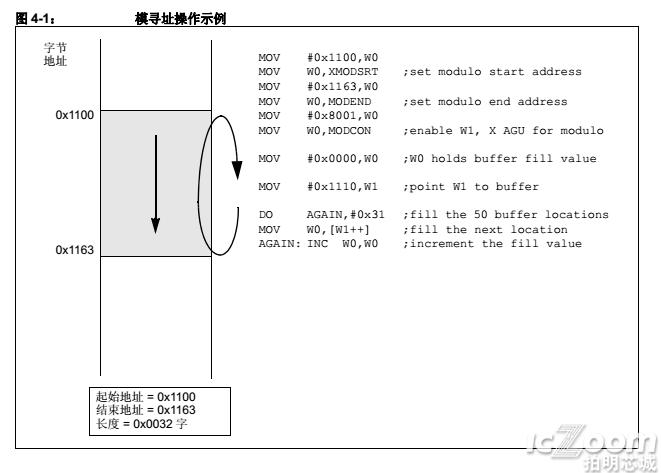

4.2 模寻址

模寻址模式,是一种使用硬件来自动支持循环数据缓冲区的方法。目的是在执行紧密循环代码时 (这在许多 DSP 算法中很典型),不需要用软件来执行数据地址边界检查。可以在数据空间或程序空间中进行模寻址(因为这两种空间的数据指针机制本质上是相同的)。每个 X (也提供指向程序空间的指针)和 Y 数据空间中都可支持一个循环缓冲区。模寻址可以对任何 W 寄存器指针进行操作。然而,最好不要将 W14 或 W15 用于模寻址,因为这两个寄存器分别用作堆栈帧指针和堆栈指针。总的来说,任何特定的循环缓冲区只能配置为单向工作,因为根据缓冲区的方向,对缓冲区起始地址(对于递增缓冲区)或结束地址(对于递减缓冲区)有某些限制。使用限制的惟一例外是那些长度为 2 的幂的缓冲区。这些缓冲区满足起始和结束地址判据,它们可以双向工作(即,在低地址边界和高地址边界上都将进行地址边界检查)。

4.2.1 起始地址和结束地址

模寻址机制要求指定起始地址和结束地址,并将它们载入 16 位 模 缓 冲 区 地 址 寄 存 器 中:XMODSRT、XMODEND、YMODSRT 和 YMODEND(见表 3-3)。

注:Y 空间模寻址的 EA 计算使用字长度的数据(每个 EA 的 LSb 始终清零)。循环缓冲区的长度没有直接指定,由相应的起始地址和结束地址之差决定其长度。循环缓冲区最大长度为 32K 字 (64 KB)。

4.2.2 W 地址寄存器选择

模寻址和位反转寻址控制寄存器 MODCON<15:0> 中包含使能标志以及指定 W 地址寄存器的 W 寄存器字段。XWM 和 YWM 字段选择对哪些寄存器进行模寻址。如果 XWM = 15,则禁止 X RAGU 和 X WAGU 模寻址。类似地,如果 YWM = 15,则禁止 Y AGU 模寻址。要对其进行模寻址的X 地址空间指针W 寄存器(XWM)位于 MODCON<3:0> 中(见表 3-3)。当 XWM 被设置为除15之外的任何值且XMODEN位(MODCON<15>)

置 1 时, X 数据空间的模寻址被使能。

要对其进行模寻址的Y 地址空间指针W 寄存器(YWM)位于 MODCON<7:4> 中。当 YWM 被设置为除 15 之外的任何值且 YMODEN 位 (MODCON<14>)置 1 时,Y 数据空间的模寻址被使能。

4.2.3 模寻址的应用

模寻址可以应用于与任何 W 寄存器相关的有效地址(EA)计算中。重要的是要意识到,地址边界检查功能,不仅会检查地址是否正好在地址边界上,而且会检查地址是否小于或大于上限 (对于递增缓冲区)、是否低于下限 (对于递减缓冲区)。因此,地址变化可能会越过边界,但仍然可以正确调整。

注:只有在使用执行前修改或执行后修改寻址模式来计算有效地址时,模修正有效地址才被写回寄存器。如果使用了地址偏移量(例如,[W7 + W2]),会进行模地址修正,但寄存器的内容保持不变。

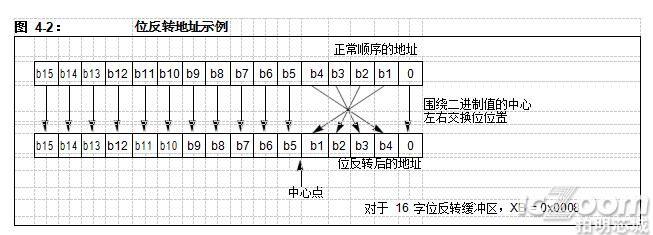

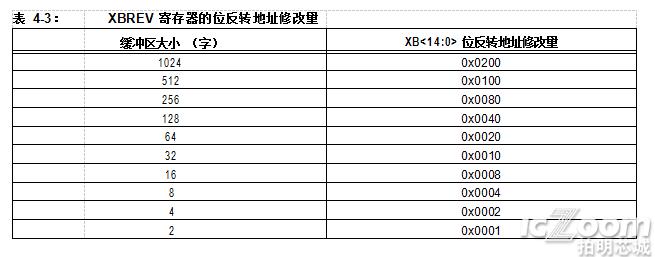

4.3 位反转寻址

位反转寻址用来简化基 2 FFT 算法的数据重新排序。位反转寻址为 X WAGU 所支持,仅限于数据写入。地址修改量,可以是常数或寄存器的内容,可视为将其位顺序反转。源地址和目的地址仍然是正常的顺序。于是,惟一需要反转的操作数就是地址修改量。

4.3.1 位反转寻址的实现

当发生以下情况时,使能位反转寻址:

• MODCON 寄存器中 BWM (W 寄存器选择)的值,是除 15 以外的任何值(不能使用位反转寻址访问堆栈),且

• XBREV 寄存器中的 BREN 位置 1,且

• 使用的寻址模式是预递增或后递增的寄存器间接寻址模式。

如果位反转缓冲区的长度是 M = 2N 字节,则数据缓冲区起始地址的最后 “N”位必须为零。XB<14:0> 是位反转地址修改量或 “中心点”(pivot point),通常是一个常数。对于 FFT 计算,其值等于 FFT 数据缓冲区长度的一半。注: 所有位反转 EA 的计算都使用字长度数据(每个 EA 的 LSb 始终为零)。为了产生兼容(字节)地址,要相应地调整 XB 的值。使能位反转寻址时,仅对预递增或后递增的寄存器间接寻址、且仅对字长度数据写入,才会进行位反转寻址。而对于任何其他寻址模式或字节长度数据,不会进行位反转寻址, 而是生成正常的地址。在进行位反转寻址时, W 地址指针将始终加上地址修改量 (XB),与寄存器间接寻址模式相关的偏移量将被忽略。此外,由于要求是字数据, EA 的 LSb 被忽略(且始终被清零)。注: 不应同时使能模寻址和位反转寻址。如果用户试图这么做的话,对于 X WAGU,位反转寻址将优先, X WAGU 模寻址将被禁止。而,在 X RAGU 中,模寻址继续起作用。如果通过置 1 BREN 位(XBREV<15>)使能了位反转寻址,那么,在写 XBREV 寄存器之后,不应马上进行要使用被指定为位反转指针的 W 寄存器的间接读操作。

5.0 闪存程序存储器

注: 本数据手册总结了 dsPIC30F 系列器件的功能,但是不应把本手册当作无所不包的参考手册来使用。有关 CPU、外设、寄存器说明和一般器件功能的更多信息,请参见 《dsPIC30F 系列参考手册》(DS70046E_CN)。有关器件指令集和编程的更多信息,请参见《16 位 MCU 和 DSC 程序员参考手册》(DS70157E_CN)。

dsPIC30F 系列器件包含用于执行用户代码的内部闪存程序存储器。用户可以使用以下两种方法对闪存程序存储器编程:

1. 运行时自编程 (RTSP)

2. 在线串行编程 (ICSP™)

5.1 在线串行编程 (ICSP)

可以在最终应用电路中对 dsPIC30F 器件进行串行编程。 只需要 5 根线即可完成这一操作,其中编程时钟线和编程数据线(名称分别为 PGC 和 PGD)各一根,其余 3 根分别是电源线(VDD)、接地线(VSS)和主复位线 (MCLR)。 这允许用户使用未编程器件生产电路板,而仅在产品交付前才对数字信号控制器进行编程,从而可以将最新版本的固件或者定制固件烧写到器件中。

5.2 运行时自编程 (RTSP)

运行时自编程(RTSP)使用 TBLRD(表读)和 TBLWT (表写)指令实现。使用 RTSP,用户可以一次擦除 32 个指令字(96 字节)的程序存储单元,一次可写入 32 个指令字(96 字节)的程序存储数据。

5.3 表指令操作综述

TBLRDL 和 TBLWTL 指令用来读或写程序存储器的bit<15:0>。TBLRDL 和 TBLWTL 可以以字或字节模式访问程序存储器。

TBLRDH 和 TBLWTH 指令用来读或写程序存储器的bit<23:16>。 TBLRDH 和 TBLWTH 可以以字或字节模式

访问程序存储器。

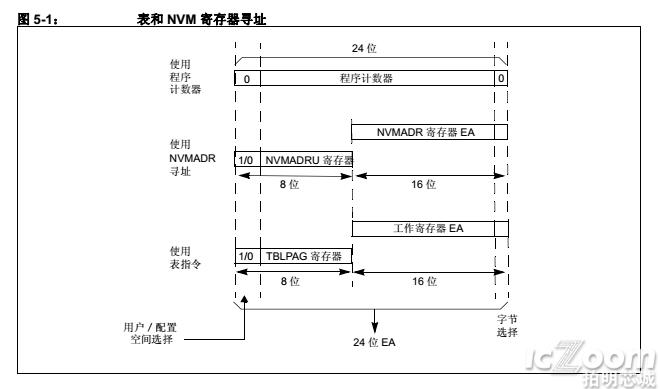

使用 TBLPAG 寄存器的 bit<7:0> 和来自表指令中指定的 W 寄存器的有效地址(EA),形成 24 位的程序存储器地址,如图 5-1 所示。

5.4 RTSP 操作

dsPIC30F 闪存程序存储器组织成行和板(panel)。每行由 32 个指令字 (96 字节)组成。每个板由 128 行(4K x 24 个指令字)组成。RTSP 允许用户每次擦除一行(32 个指令字)、每次编程 4 条指令。RTSP 可以用来对多个程序存储器板进行编程,但在每个板的边界处必须更改表指针。

程序存储器的每个板都包含写锁存器,它能够保存32个指令字的编程数据。在实际编程操作前,等待写入的数据必须先装入板的写锁存器。要写入板的数据按顺序装载到写锁存器中:指令 0,指令 1,依此类推。 装载的指令字必须始终来自 32 个指令字的地址边界。RTSP 编程的基本步骤是先建立一个表指针,然后执行一系列 TBLWT 指令,装载写锁存器。通过把 NVMCON寄存器中的特定位置 1,进行编程。装载 32 条指令需要 32 条 TBLWTL 和 4 条 TBLWTH 指令。如果需要对多个板进行编程,应该为下一组要写入的多个写锁存器修改表指针。由于只需要写表锁存器,所以所有表写操作都是单字写入 (2 个指令周期)。编程每一行需要一个编程周期。在整个 VDD 范围内,正常操作期间,闪存程序存储器是可读、可写且可擦除的。

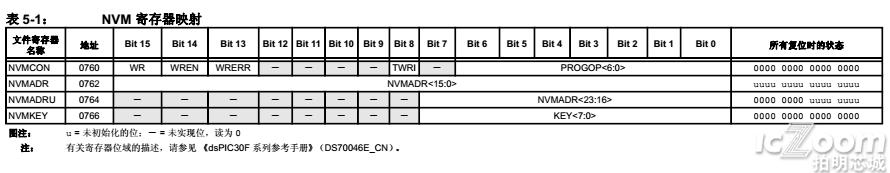

5.5 控制寄存器

四个特殊功能寄存器用来读、写闪存程序存储器,它们是:

• NVMCON

• NVMADR

• NVMADRU

• NVMKEY

5.5.1 NVMCON 寄存器

NVMCON 寄存器控制要擦除的存储块、要编程的存储器类型以及编程周期的启动。

5.5.2 NVMADR 寄存器

NVMADR 寄存器用来存放有效地址的两个低字节。它捕捉已执行的上一条表指令的 EA<15:0>,选择要写的行。

5.5.3 NVMADRU 寄存器

NVMADRU 寄存器用来存放有效地址的高字节。它捕捉已执行的上一条表指令的 EA<23:16>。

5.5.4 NVMKEY 寄存器

NVMKEY 是只写寄存器,用于写保护。要启动编程或擦除过程,用户必须把 0x55 和 0xAA 连续写入 NVMKEY寄存器。更多细节,请参见第 5.6 节 “编程操作”。

注: 用户也可直接写 NVMADR 和 NVMADRU寄存器,以指定擦除或编程的程序存储器地址。

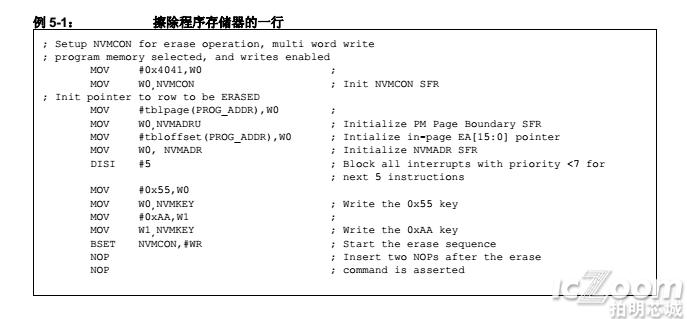

5.6 编程操作

在 RTSP 模式下,对内部闪存进行编程或擦除需要完整的编程过程。编程操作持续时间的标称值为 2 ms,编程操作结束之前,处理器将暂停(等待) 。将 WR 位(NVMCON<15>)置 1 开始编程操作,操作结束后将自动清零 WR 位。

5.6.1 闪存程序存储器的编程算法

用户一次可擦除或编程闪存程序存储器的一行。一般过程如下:

1. 读一行闪存程序存储器(32 个指令字),把读出的数据作为数据 “镜像”保存到数据 RAM 中。

2. 用期望的新数据更新数据镜像。

3. 擦除闪存程序存储器行。

a) 设置 NVMCON 寄存器以允许对闪存程序存储器进行多字擦除,并将 WREN 位置 1。

b) 把要擦除的行地址写入寄存器 NVMADRU/

NVMDR。

c) 把 0x55 写入 NVMKEY。

d) 把 0xAA 写入 NVMKEY。

e) 将 WR 位置 1。这将开始擦除周期。

f) 在擦除周期中 CPU 将暂停。

g) 当擦除周期结束时, WR 位会被清零。

4. 从数据 RAM“镜像”中把 32 个指令字的数据写入闪存程序存储器写锁存器。

5. 将 32 个指令字写入闪存程序存储器。

a) 设置 NVMCON 寄存器以允许对闪存程序存储器进行多字编程,并将 WREN 位置 1。

b) 把 0x55 写入 NVMKEY。

c) 把 0xAA 写入 NVMKEY。

d) 将 WR 位置 1。这将开始编程周期。

e) 在编程周期中 CPU 将暂停。

f ) 当编程周期结束时, WR 位会被硬件清零。

6. 根据需要,重复步骤 1 到 5,对所需的闪存程序存储器进行编程。

5.6.2 擦除程序存储器的一行

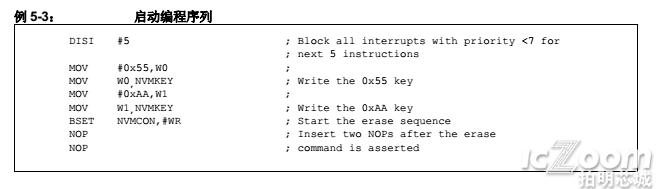

例 5-1 所示的代码序列可以用来擦除程序存储器的一行(32 个指令字)。

5.6.3装载写锁存器

例 5-2 所示的指令序列可以用来装载 96 字节的写锁存器。装载由表指针选择的写锁存器需要 32 条 TBLWTL 指令和 32 条 TBLWTH 指令。

5.6.4启动编程序列

出于保护的目的,必须使用 NVMKEY 的写启动序列,以便允许进行任何擦除或编程操作。在执行编程命令后,用户必须等待一段时间 (编程时间),直至编程完成。 启动编程序列后紧跟的两条指令应该为 NOP,如例 5-3 所示。

6.0 数据 EEPROM 存储器

注: 本数据手册总结了 dsPIC30F 系列器件的功能,但是不应把本手册当作无所不包的参考手册来

使用。有关 CPU、外设、寄存器说明和一般器件功能的更多信息,请参见《dsPIC30F 系列参考手册》(DS70046E_CN)。有关器件指令集和编程的更多信息,请参见《16 位 MCU 和 DSC 程序员参考手册》(DS70157E_CN)。在整个 VDD 范围内的正常操作期间,数据 EEPROM 存储器是可读且可写的。数据 EEPROM 存储器直接映射到程序存储器地址空间。用来读写闪存程序存储器的四个特殊功能寄存器,也用来访问数据 EEPROM 存储器。如在第 5.5 节 “控制寄

存器”中所述,这些寄存器是:

• NVMCON

• NVMADR

• NVMADRU

• NVMKEY

EEPROM 数据存储器允许读写单个字和 16 字长的块。针对数据存储器时, NVMADR 与 NVMADRU 寄存器配合使用,用来寻址要访问的 EEPROM 存储单元。

TBLRDL 和 TBLWTL 指令用来读写数据 EEPROM。 dsPIC30F 器件有最多 8 KB (4 K 字)的数据EEPROM,地址范围从 0x7FF000 到 0x7FFFFE。字写操作之前,应该先擦除相应的存储单元。写操作完成通常需要 2 ms,不过它将随电压和温度的变化而变化。对数据 EEPROM 进行编程或擦除操作,不会停止指令流。在启动另一次数据 EEPROM 写 / 擦除操作之前,用户需要等待一段适当的时间。在编程或擦除操作进行过程中,尝试读数据 EEPROM 将返回不确定的数据。控制位 WR 启动写操作,这与闪存程序存储器写类似。可通过软件置 1 WR 位,但不能对其清零。写操作完成时,硬件将清零 WR 位。 不能用软件清零 WR 位,这样避免了意外或提早结束写操作。WREN 位置 1 时将允许进行写操作。上电时,WREN 位清零。当写操作被正常工作期间的 MCLR 复位或 WDT 超时复位所中断时,WRERR 位置 1。在这样的情形下,复位后,用户可以检查 WRERR 位,重写存储单元。地址寄存器 NVMADR 保持不变。

注: 在写操作完成时, IFS0 寄存器中的中断标志位 NVMIF 将置 1。NVMIF 位必须用软件清零。

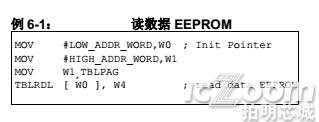

6.1 读数据 EEPROM

TBLRD 指令读取位于当前程序字地址的字。下面的示例使用 W0 作为指向数据 EEPROM 的指针。结果存放在寄存器 W4 中,如例 6-1 所示。

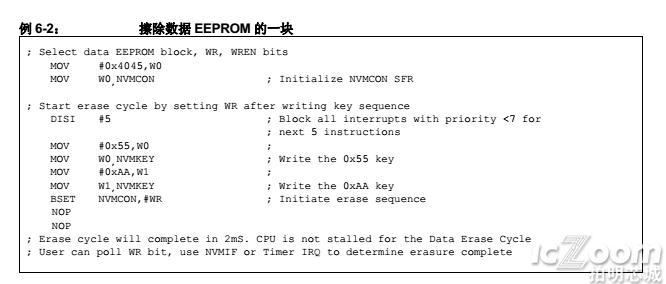

6.2 擦除数据 EEPROM

6.2.1 擦除数据 EEPROM 的一块为了擦除数据 EEPROM 的一块,首先 NVMADRU 和NVMADR 寄存器必须指向要擦除的存储块。将NVMCON 配置为擦除数据 EEPROM 块,并置 1 NVMCON寄存器中的WR位和WREN位。置1 WR 位,启动擦除操作,如例 6-2 所示。

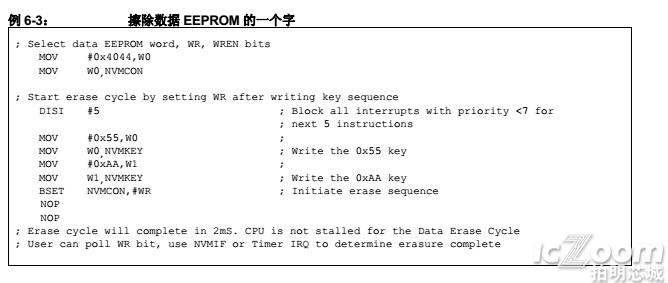

6.2.2擦除数据 EEPROM 的一个字NVMADRU 和 NVMADR 寄存器必须指向要擦除的存储块。在 NVMCON 寄存器中,选择擦除数据 EEPROM 的一个字,置 1 WR 位和 WREN 位。置 1 WR 位,启动擦除操作,如例 6-3 所示。

6.3 写数据 EEPROM

要写 EEPROM 数据存储单元,必须按照下列顺序进行:

1. 擦除数据 EEPROM 的字。

a) 在 NVMCON 寄存器中,选择字擦除数据EEPROM,并置 1 WREN 位。

b) 把要擦除的字的地址写入 NVMADR。

c) 允许 NVM 中断(可选)。

d) 把 0x55 写入 NVMKEY。

e) 把 0xAA 写入 NVMKEY。

f) 置 1 WR 位。这将开始擦除周期。

g) 查询 NVMIF 位或等待 NVMIF 中断。

h) 当擦除周期结束时 WR 位会被清零。

2. 把数据字写入数据 EEPROM 的写锁存器中。

3. 把 1 个数据字编程到数据 EEPROM 中。

a) 在 NVMCON 寄存器中,选择字编程数据EEPROM,并置 1 WREN 位。

b) 允许 NVM 写完成中断(可选)。

c) 把 0x55 写入 NVMKEY。

d) 把 0xAA 写入 NVMKEY。

e) 置 1 WR 位。这将开始编程周期。

f) 查询 NVMIF 位,或者等待 NVM 中断。

g) 当写周期结束时 WR 位会被清零。

对于每个字,如果上述序列(把 0x55 写入 NVMKEY,把 0xAA 写入 NVMCON,然后置 1 WR 位)没有严格遵守的话,写操作不会启动。 强烈建议在这段代码执行期间,禁止中断。此外,必须置 1 NVMCON 中的 WREN 位来使能写操作。这样的机制,防止由于不可预料的代码执行而意外地写数据 EEPROM。除非在更新 EEPROM 时,否则 WREN 位应该始终保持清零。硬件不能清零 WREN 位。在写过程启动之后,清零 WREN 位将不会影响当前的写周期。禁止把 WR 位置 1,除非 WREN 位已置 1。必须在前一条指令中置 1 WREN 位。不能在同一条指令中置 1 WR 和 WREN 位。写周期结束时,硬件清零 WR 位,非易失性存储器写完成中断标志位 (NVMIF)置 1。用户可以允许这个中断,或者查询这个标志位。NVMIF 必须由软件清零。

6.3.1 写数据 EEPROM 的一个字一旦用户擦除了要编程的字,则表写指令用来写写锁存器,如例 6-4 所示。

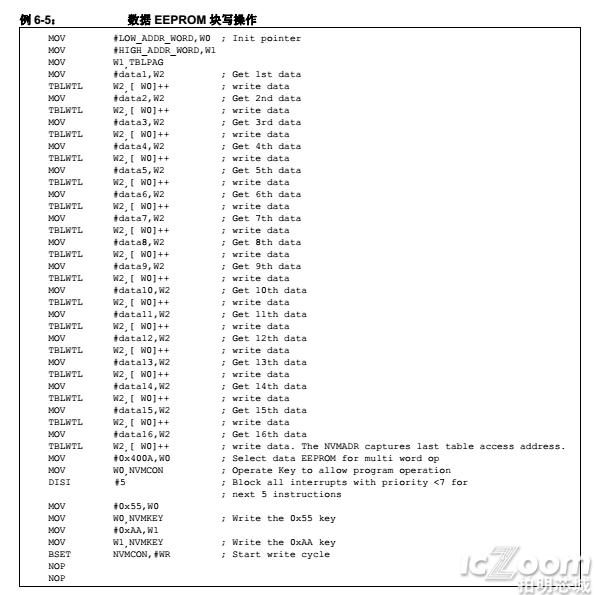

6.3.2 写数据 EEPROM 的一个存储块要写入数据 EEPROM 的一个存储块,应首先写入所有 16 个锁存器,然后设置 NVMCON 寄存器并对存储块进行编程。

6.4写校验

根据不同的应用,良好的编程习惯可能要求把已写入存储器中的值对照原始值进行校验。如果在应用中进行了过多的写操作,可能接近规范中的上限值时,就应该进行写校验。

6.5防止误写入

某些情况下,并不打算写数据 EEPROM 存储器。器件内置了各种机制来防止误写入 EEPROM。上电时,WREN位清零;而且,上电延时定时器禁止 EEPROM 写操作。写启动序列与 WREN 位一起,有助于防止欠压、电源故障或软件异常期间的意外写入

7.0 I/O 端口

注:本数据手册总结了 dsPIC30 系列器件的功能,但是不应将其当作无所不包的参考手册使用。 有关CPU、外设、寄存器说明和通用器件功能的更多信息,请参见 《dsPIC30F 系列参考手册》(DS70046E_CN)。所有的器件引脚(除 VDD、VSS、MCLR 和 OSC1/CLKI以外)均由外设和并行 I/O 端口所共用。所有 I/O 输入端口都为施密特触发器输入,以便增强抗干扰性。

7.1 并行 I/O (PIO)端口

如果外设使能,并且外设正在使用相关引脚时,该引脚将不再作为通用 I/O 引脚使用。这时,可以读该 I/O 引脚,但对应并行端口引脚位的输出驱动器将被禁止。如果外设使能,但外设不在使用某引脚,则该引脚可以被端口驱动。

所有端口引脚都有三个寄存器,这些寄存器与端口引脚的工作直接相关。数据方向寄存器(TRISx)决定引脚是输入引脚还是输出引脚。如果数据方向位为 1,则为输入引脚。复位以后,所有端口引脚被定义为输入。读锁存器(LATx),读到的是锁存的值;写锁存器,写入锁存器 (LATx)。但读取端口 (PORTx)时,读到的是端口引脚的值;而写入端口引脚时,写入到锁存器(LATx)。任何位及其关联的数据和控制寄存器,如果对于特定器件而言是无效的话,则将被禁止。这意味着相应的 LATx 和 TRISx 寄存器以及该端口引脚将读为 0。当一个引脚与另一个外设或定义为仅输入的功能复用时,由于没有其他竞争的输出源,它将被视为专用端口。通常,与某个外设共用一个引脚的并行 I/O (PIO)端口总是服从于该外设。外设的输出缓冲器数据和控制信号提供给一对多路开关。多路开关选择外设还是相关的端口将拥有 I/O 引脚的输出数据和控制信号的所有权。

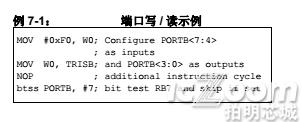

图 7-1 图示了端口与其他外设的复用关系,以及与外设连接的相关 I/O 引脚单元。

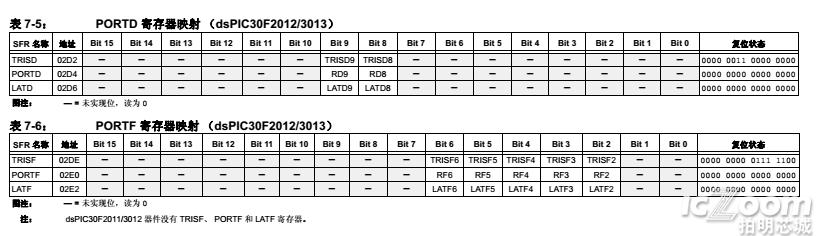

共用端口(PORTB、PORTC、PORTD 和 PORTF)的寄存器格式如表 7-1 至表 7-6 所示。

注: 不同器件实际使用的位有所不同。

7.2配置模拟端口引脚

ADPCFG 和 TRIS 寄存器用于控制 A/D 端口引脚的操作。若希望端口引脚为模拟输入引脚,则必须将相应的 TRIS 位置 1 (输入)。如果将 TRIS 位清零(输出),则将转换该引脚的数字输出电平 (VOH 或 VOL)。读取端口寄存器时,所有配置为模拟输入通道的引脚均读为 0 (低电平)。配置为数字输入的引脚,将不对模拟输入信号进行转换。对任何定义为数字输入的引脚(包括 ANx 引脚)施加模拟电平,可能导致输入缓冲器的电流消耗超出器件规范中规定的值。

7.2.1I/O 端口写 / 读时序

在改变端口方向或对端口执行写操作,与对同一端口执行读操作之间需要间隔一个指令周期。通常在两者之间插入一条 NOP 指令。

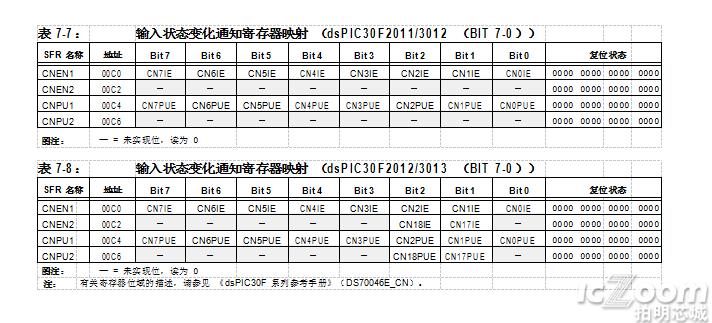

7.3 输入状态变化通知模块

I/O 端口的输入状态变化通知功能允许 dsPIC30F 器件在选定输入引脚的状态变化时,向处理器发出中断请求。当禁止时钟时,该特性还可在休眠模式下检测到输入状态改变。 最多可以选择(允许) 10 个外部信号(CN0 至 CN7、 CN17 和 CN18)在输入状态发生变化时产生中断请求。

8.0 中断

注:本数据手册总结了 dsPIC30 系列器件的功能,但是不应将其当作无所不包的参考手册使用。有关

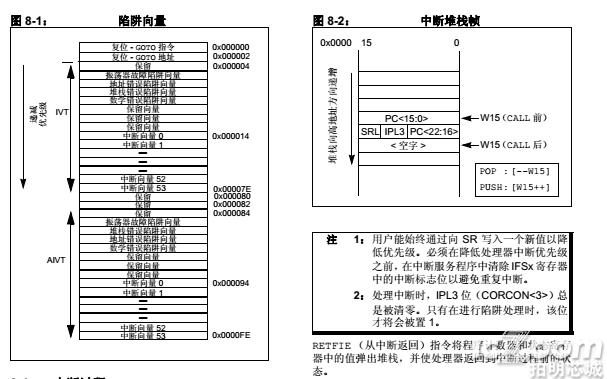

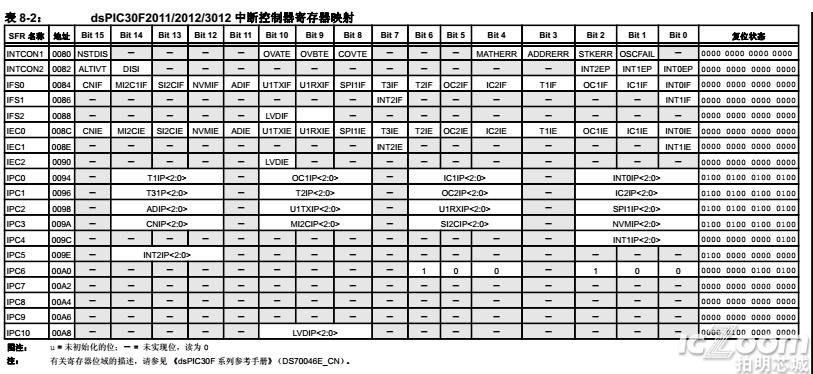

CPU、外设、寄存器说明和通用器件功能的更多信息,请参见 《dsPIC30F 系列参考手册》(DS70046E_CN)。欲知有关指令集和编程的更多详细信息,请参见 《16 位 MCU 和 DSC 程序员参考手册》(DS70157E_CN)。dsPIC30F 传感器系列具有最多 21 个中断源和 4 个处理器异常 (陷阱),所有中断和异常的处理必须依据优先级机制进行仲裁。CPU 负责读取中断向量表(IVT)并将包含在中断向量中的地址传输给程序计数器。中断向量通过程序计数器输入端的 24 位宽的多路开关,从程序数据总线传输到程序计数器。

中断向量表(IVT)和备用中断向量表(AIVT)位于程序存储器起始地址附近 (0x000004)。 IVT 和 AIVT 如

图 8-1 所示。

中断控制器负责在中断和处理器异常传送到处理器内核前,对它们进行预处理。 使用集中化的特殊功能寄存器Special Function Register,SFR)允许、控制外设中断和陷阱,并对它们进行优先级分配。

• IFS0<15:0>、 IFS1<15:0> 和 IFS2<15:0>这三个寄存器包含所有中断请求标志位。各中断请求标志由相应的外设或外部信号置 1,标志的清零则通过软件完成。

• IEC0<15:0>、 IEC1<15:0> 和 IEC2<15:0>这三个寄存器包含所有中断允许控制位。这些控制位用于单独允许外设或外部信号的中断。

• IPC0<15:0> 至 IPC10<7:0>与这 41 个中断相应的用户可分配优先级集中保存在这 11 个寄存器中。

• IPL<3:0>

当前 CPU 优先级显示地储存在 IPL 位中。 IPL<3>位于 CORCON 寄存器中,而 IPL<2:0> 位于处理器内核的状态寄存器 (SR)中。

• INTCON1<15:0> 和 INTCON2<15:0>

全局中断控制功能由这两个寄存器提供。 INTCON1 包含处理器异常的控制和状态标志位。 INTCON2 寄存器控制外部中断请求信号的行为和备用中断向量表的使用。

注: 发生中断时,无论相应的中断允许位的状态如何,中断标志位将置 1。用户软件应确保在允许一个中断前清零相应的中断标志位。

用户可通过 IPCx 寄存器,为所有中断源分配 7 个优先级中的一个,优先级从 1 到 7。 每个中断源都与一个中断向量相关,如表 8-1 所示。 优先级 7 和 1 分别表示最高和最低的可屏蔽优先级。

注:为中断源分配的优先级为 0,等效于禁止该

中断。

若 NSTDIS 位(INTCON1<15>)置 1,则禁止中断嵌套。这样可使在处理中断时,禁止处理新的中断,即使新中断的优先级高于正在处理的中断优先级。

注: 一旦NSTDIS位置1,IPL位就变为只读位。

某些中断具有控制边沿或电平触发中断、电平变化中断等功能的专用控制位。对这些功能的控制仍然由产生中断的外设模块完成。对于某些指令,在其执行期间如果 DISI 位(INTCON2<14>)保持置 1 的话,那么可以用 DISI 指令来禁止优先级为 6 或更低的中断的处理。处理中断时, PC 中载入存放在程序存储器中相应中断向量存储单元中的地址。IVT 中有 63 个不同的向量(见表 8-1)。 这些向量存放在程序存储器的 0x000004 至 0x0000FE 存储单元(见表 8-1)。 这些存储单元包含

24 位地址,以保持鲁棒性,如果在正常执行期间 PC 试图取这些字中的任意一个,就会发生地址错误陷阱。 这样便可防止由于以下情况而执行随机数据:PC 意外地递减到向量空间、意外地将数据空间地址映射到向量空间或 PC 在到达已实现的程序存储空间的末尾后重新回到 0x000000。 执行 GOTO 指令跳转到此向量空间也会产生地址错误陷阱。

8.1中断优先级

对于各中断源,用户可分配中断优先级位 (IP<2:0>)位于 IPCx 寄存器中每个半字节的最低 3 位。 每个半字节的 bit 3 未使用,读为 0。这些位定义了用户分配给某特定中断的优先级。

注: 用户可分配优先级范围为 0(最低优先级)至 7 (最高优先级)。

自然顺序优先级由中断在向量表中的位置决定,只是在同时有多个中断——它们都具有相同的用户分配优先级——等待处理时,自然顺序优先级才会影响到中断操作。

表 8-1 列出了 dsPIC30F2011/2012/3012/3013 器件的中断编号和中断源,以及关联的向量编号。

注1: 自然顺序优先级机制以 0 为最高优先级,

以53 为最低优先级。

2: 自然顺序优先级编号与 INT 编号相同。

用户可为各中断分配七个优先级中的一个,这意味着用户可为一个具有较低自然顺序优先级的中断分配一个非常高的总优先级。 例如,可将低压检测 (Low-Voltage Detect, PLVD )的优先级分配为 7。将 INT0 (外部中断 0)的优先级分配为 1,这样,它的有效优先级将非常低。

注 1: 仅 dsPIC30F3013 具有 UART2 以及U2RX 和 U2TX 中断。 这些存储单元在 dsPIC30F2011/2012/3012 中为保留的存储单元。

8.2 复位过程

由于复位过程中不涉及到中断控制器,所以器件复位并不是真的异常。在响应强制清零 PC 的复位时,处理器将初始化其寄存器。然后,处理器从存储单元 0x000000 处开始执行程序。一条 GOTO 指令存放在第一个程序存储单元中,紧跟着的是 GOTO 指令的地址目标。处理器执行 GOTO,跳转到指定地址,然后开始指定目标(起始)地址处的操作。

8.2.1 复位源

除外部复位和上电复位(POR)外,还有 6 个错误条件会引起器件复位。

• 看门狗定时器超时:看门狗定时器已超时,表明处理器不再执行正确的代码流。

• 未初始化的 W 寄存器陷阱:试图把未初始化的 W 寄存器用作地址指针而导致复位。

• 非法指令陷阱:试图执行任何未使用的操作码而引起非法指令陷阱。 注意,如果由于指令流更改而使非法指令在执行前被从指令流水线中舍弃,则取此非法指令不会引起非法指令陷阱。

• 欠压复位 (BOR):检测到可能导致器件故障的电源电压短暂降低。

• 陷阱锁定:多个并发的陷阱条件将导致复位。

8.3 陷阱

可以将陷阱看作不可屏蔽中断,表明出现软件或硬件错误,它遵从如图 8-1 所示的预定义的优先级。 陷阱旨在为用户提供一种方法,改正在调试和在应用中工作时的错误操作。

注:如果用户不想在陷阱错误条件事件时采取校正措施,那么必须在这些陷阱向量中装入缺省陷阱处理程序的地址,缺省陷阱处理程序包含 RESET 指令。否则,如果调用了包含非法地址的陷阱向量,将产生地址错误陷阱。

注意,很多陷阱条件只有在发生的时候才能检测到。 因此,在陷阱异常处理之前允许有问题的指令完成执行。如果用户选择从错误中恢复,则可能需要校正导致陷阱的错误操作的结果。

陷阱有 8 个固定优先级:优先级 8 级至优先级 15 级,意味着处理陷阱时, IPL3 始终置 1。

如果用户当前不在执行陷阱,而将 IPL<3:0> 位设置为 0111 (优先级 7),这样将禁止所有中断,但仍然能处理陷阱。

8.3.1 陷阱源

下列陷阱的优先级依次递增。然而,由于所有陷阱都可以嵌套,因此优先级的作用很小。

数学错误陷阱:

在以下四种情况下,执行数学错误陷阱:

1. 如果试图进行以零作除数的除法运算,除法运算将在周期边界处中止,并产生陷阱。

2. 如果使能的话,当对累加器 A 或 B 进行的算术运算导致了 bit 31 溢出,并且没有使用累加器警戒位时,将产生数学错误陷阱。

3. 如果使能的话,当对累加器 A 或 B 进行的算术运算导致了 bit 39 灾难性溢出,并且所有饱和被禁止时,将产生数学错误陷阱。

4. 如果在移位指令中指定的移位位数大于允许的最大移位位数,将产生陷阱。

地址错误陷阱:

当发生以下情况时,将产生此陷阱:

1. 试图访问未对齐的数据字。

2. 试图从未实现的数据存储单元取数据。

3. 试图访问未实现的程序存储单元。

4. 试图从向量空间取指令。

注: 在 MAC 类指令中,数据空间分割为 X 和 Y 数据空间,未实现的 X 空间包括所有的 Y 空间,未实现的 Y空间包括所有的 X空间。

5. 执行 BRA #literal 指令或 GOTO #literal指令,其中 literal 是未实现的程序存储器地址。

6. 修改 PC 使其指向未实现的程序存储器地址后,执行指令。通过将值装入堆栈并执行 RETURN 指令可以修改 PC。

堆栈错误陷阱:

当发生以下情况时,产生此陷阱:

• 堆栈指针中载入了一个大于写入到 SPLIM 寄存器的 (用户可编程)极限值(堆栈溢出)的值。

• 堆栈指针中载入一个小于 0x0800 的值 (简单堆栈下溢)。

振荡器故障陷阱:

如果外部振荡器出现故障,器件使用备用的内部 RC 振荡器工作,就会产生振荡器故障陷阱。

8.3.2 硬陷阱和软陷阱

在同一周期内可能会产生多个陷阱(例如,把不对齐的字写入堆栈中的溢出地址)。 此时,图 8-2 所示的固定优先级就会起作用;为了完全纠正错误,这可能需要用户检查是否有其他等待处理的陷阱。软陷阱包括优先级 8 到 11 的异常。算术错误陷阱(优先级 11)就属于这一类陷阱。硬陷阱包括优先级 12 至 15 的异常。地址错误(优先级12)、堆栈错误(优先级 13)和振荡器错误(优先级14)陷阱就属于这一类。每个硬陷阱产生时,在执行任何代码之前,必须先对它进行响应。在优先级较高的陷阱正在等待处理、被响应或正在处理过程中时,如果产生了较低优先级的陷阱,就会产生硬陷阱冲突。器件在硬陷阱冲突时自动复位。 发生复位时, TRAPR 状态位(RCON<15>)置 1,因此可用软件检测该条件

8.4 中断过程

在每个指令周期的开始, IFSx 寄存器都会采样全部的中断事件标志。IFSx 寄存器中标志位等于 1,表明有等待处理的中断请求(IRQ)。如果中断允许(IECx)寄存器中相应的位置 1, IRQ 将会导致中断产生。 在 IRQ 采样后余下的指令周期中,将评估所有待处理中断请求的优先级。如果有待处理的 IRQ,它的优先级比 IPL 位中的当前处理器优先级高,则处理器将被中断。随后,处理器将当前程序计数器的值和处理器状态寄存器(SRL)的低字节压入堆栈,如图 8-2 所示。 状态寄存器的低字节包含中断周期开始前的处理器优先级。处理器随后将此中断的优先级载入状态寄存器。完成中断服务程序(ISR)前,此操作禁止所有的低优先级中断。

8.5 备用向量表

在程序存储器中,中断向量表(IVT)之后紧跟备用中断向量表 (AIVT),如图 8-1 所示。 INTCON2 寄存器中的 ALTIVT 位控制对备用向量表的访问。如果 ALTIVT位置 1,所有中断和异常处理将使用备用向量,而不是默认的向量。备用向量与默认向量的组织方式是相同的。 AIVT 提供了一种在应用和支持环境之间切换的方法,从而支持仿真和调试功能,而不需要对中断向量进行再编程。这个特性也支持运行时在不同应用之间切换,以便评估各种软件算法。如果不需要 AIVT,则分配给 AIVT 的程序存储器可用于其他用途。AIVT不是受保护的区域,用户可对其自由编程。

• 快速现场保护

使用影子寄存器可保存现场。 为 SR 中的 DC、N、OV、Z 和 C 位及寄存器 W0 至 W3 提供了影子寄存器。影子寄存器深度仅为一级。 仅可使用 PUSH.S 和 POP.S 指令访问影子寄存器。当处理器转移到中断向量开始处理中断时,可以使用PUSH.S 指令,把上述寄存器的当前值保存到它们对应的影子寄存器中去。如果某个优先级的 ISR 使用 PUSH.S 和 POP.S 指令进行快速现场保护,那么优先级更高的 ISR 就不应再使用这两条指令。如果优先级较高的 ISR 使用了快速现场保护,那么在优先级较低的中断处理期间,用户必须保存关键寄存器。

• 外部中断请求

中断控制器支持三个外部中断请求信号:INT0-INT2。这些输入是边沿敏感的;它们需要从低至高或从高至低的跳变来产生中断请求。 INTCON2 寄存器具有 3 个位(INT0EP-INT2EP),用于选择边沿检测电路的极性。

• 从休眠和空闲模式唤醒

如果产生中断时处理器处于休眠或空闲模式,则可使用中断控制器将处理器从休眠或空闲模式唤醒。如果中断控制器收到已允许的中断请求,且中断请求优先级足够高的话,则标准中断请求将提交给处理器。 同时,处理器会从休眠或空闲模式唤醒,并开始执行处理中断请求所需的 ISR。

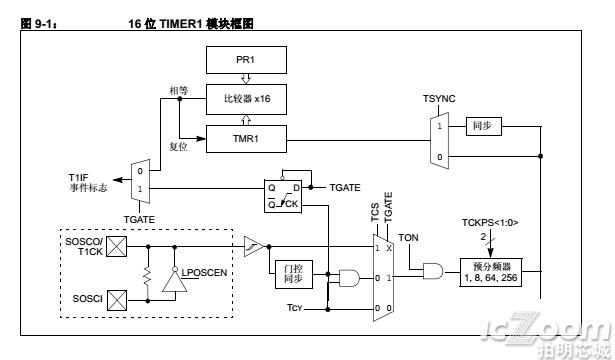

9.0TIMER1 模块

注: 本数据手册总结了 dsPIC30F 系列器件的功能,但是不应把本手册当作无所不包的参考手册来使用。有关CPU、外设、寄存器说明和一般器件功能的更多信息,请参阅《dsPIC30F 系列参考手册》(DS70046E_CN)。本章介绍了 16 位通用 Timer1 模块以及相关的工作模式。图 9-1 给出了 16 位 Timer1 模块的简化框图。 下面各小节将详细说明定时器的工作模式,包括其设置、控制寄存器以及相应的框图。Timer1 模块是一个 16 位的定时器,可作为实时时钟的时间计数器,或作为自由运行的时段定时器 / 计数器。16 位定时器有下列模式:

• 16 位定时器

• 16 位同步计数器

• 16 位异步计数器

而且,支持下列操作特征:

• 定时器门控操作

• 可选的预分频比设置

• CPU 空闲和休眠模式下的定时器操作

• 在 16 位周期寄存器匹配时或外部门控信号的下降沿产生中断通过设定 16 位 SFRT1CON 中的相应位来决定这些工作模式。图 9-1 所示为 16 位 Timer1 模块的框图。16 位定时器模式:在 16 位定时器模式下,定时器在每个指令周期递增,直到与预先装入周期寄存器 PR1 中的值匹配,然后复位至 0,继续计数。CPU 进入空闲模式时,定时器将停止递增,除非 TSIDL位 (T1CON<13>) = 0。 如果 TSIDL = 1,则定时器模块逻辑将在 CPU 空闲模式结束后继续递增。16 位同步计数器模式:在 16 位同步计数器模式下,定时器将在外部时钟信号的上升沿递增,外部时钟信号与内部时钟同步。定时器计数,直到等于 PR1 中预先装入的值,然后复位至 0,继续计数。CPU 进入空闲模式时,定时器将停止递增,除非对应的TSIDL 位 = 0。 如果 TSIDL = 1,则定时器模块逻辑将在 CPU 空闲模式结束后继续递增。16 位异步计数器模式: 在 16 位异步计数器模式下,定时器将在外部时钟信号的上升沿递增。 定时器计数,直到等于PR1中预先装入的值,然后复位至0,继续计数。当定时器配置为异步工作模式时,且 CPU 进入空闲模式的话,如果 TSIDL = 1,则定时器将停止递增。

• 定时器门控操作

16 位定时器可以置为门控时间累加模式。该模式使得当门控输入信号(T1CK 引脚)为高电平时,内部 TCY 能够递增相应的定时器。要使能该模式,必须置 1 控制位TGATE(T1CON<6>)。必须使能定时器(TON = 1),且将定时器时钟源设置为内部时钟源 (TCS = 0)。CPU 进入空闲模式时,定时器将停止递增,除非TSIDL = 0。 如果 TSIDL = 1,则定时器将在 CPU 空闲模式终止后继续递增。

• 定时器预分频器 16 位定时器的输入时钟 (Fosc/4 或外部时钟) ,有1:1、1:8、1:64 或 1:256 的预分频比供选择;通过控制位 TCKPS<1:0> (T1CON<5:4>)来选择预分频比。当发生以下任一事件时,预分频器的计数器将清零:

• 对 TMR1 寄存器进行写操作

• 对 T1CON 寄存器进行写操作

• 器件复位,如 POR 和 BOR但是,如果定时器被禁止 (TON = 0),由于预分频器的时钟停止了工作,定时器预分频器将不会复位。写 T1CON 寄存器时, TMR1 寄存器不会被清零。当写 TMR1 寄存器时, TMR1 将被清零。

• 休眠模式下的定时器操作在 CPU 休眠模式期间,定时器将继续工作,如果:

• 定时器模块被使能 (TON = 1),且

• 定时器时钟源选用外部时钟 (TCS = 1),且

• TSYNC 位 (T1CON<2>)为逻辑 0,这将外部时钟源定义为异步的。如果所有这三个条件都得到满足,定时器将继续计数,直到等于周期寄存器中的值,然后复位至 0x0000。当定时器与周期寄存器之间匹配时,如果相应的定时器中断允许位置 1 的话,将产生中断。

• 定时器中断 16 位定时器具有在周期匹配时产生中断的能力。 当定时器计数与周期寄存器相匹配时, T1IF 位将置 1,如果允许中断的话将产生中断。T1IF 位必须用软件清零。 定时器中断标志T1IF位于中断控制器的 IFS0 控制寄存器中。

当使能了门控时间累加模式时,还将在门控信号的下降沿 (累加周期的末尾)产生中断。通过相应的定时器中断允许位T1IE来允许定时器中断。定时器中断允许位位于中断控制器的 IEC0 控制寄存器中。

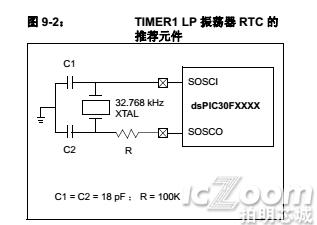

9.5实时时钟

当 Timer1 工作在实时时钟(RTC)模式下时,提供了当天时间和事件时间标记的能力。RTC的主要工作特性如下:

• 使用 32kHz LP 振荡器工作

• 8 位预分频器

• 低功耗

• 实时时钟中断工作模式由 T1CON 寄存器中相应位的设置决定。

• RTC 振荡器操作

当 TON = 1、 TCS = 1 且 TGATE = 0 时,定时器在32 kHz LP 振荡器输出信号的上升沿递增,一直递增到周期寄存器中指定的值,然后复位至 0。为确保正确工作, TSYNC 位必须置为逻辑 0 (异步模式)。使能 LPOSCEN 位 (OSCCON<1>)将禁止正常的定时器和计数器模式,而使能定时器溢出唤醒事件。当 CPU 进入休眠模式时,如果 32 kHz 外部晶体振荡器处于工作状态且控制位没有改变的话,则 RTC 将继续工作。 要使 RTC 在空闲模式下继续工作, TSIDL 位应当清零。

• RTC 中断

当中断事件发生时,相应的中断标志 T1IF 将置 1,如果允许中断的话就将产生中断。 T1IF 位必须用软件清零。相应的定时器中断标志 T1IF 位于中断控制器的 IFS0 状态寄存器中。通过相应的定时器中断允许位 T1IE 来允许中断。 定时器中断允许位位于中断控制器的 IEC0 控制寄存器中。

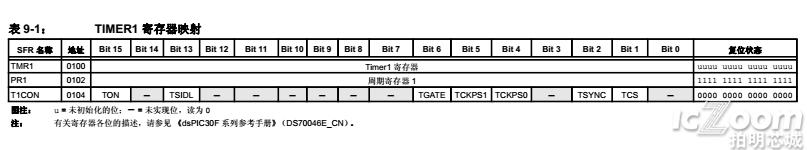

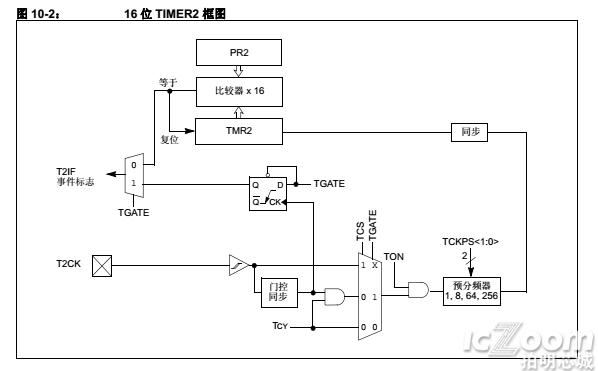

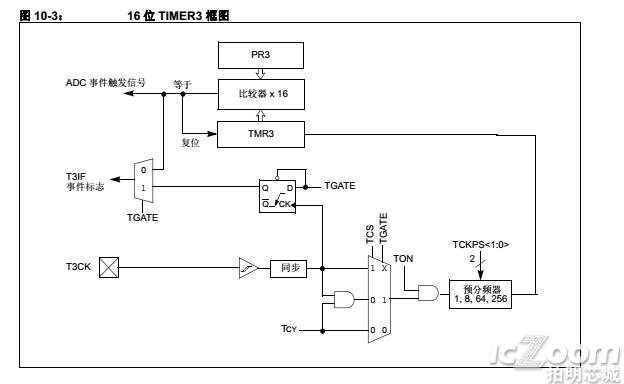

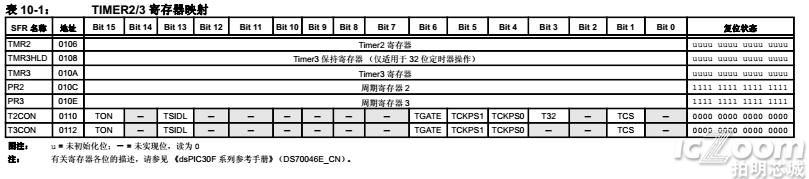

• TIMER2/3 模块

注: 本数据手册总结了 dsPIC30F 系列器件的功能,

但是不应把本手册当作无所不包的参考手册来使用。 有关 CPU、外设、寄存器说明和一般器件功能的更多信息,请参阅《dsPIC30F 系列参考手册》(DS70046E_CN)。本章介绍了 32 位通用定时器模块 (Timer2/3)以及相关的工作模式。图 10-1 给出了 32 位 Timer2/3 模块的简化框图。图 10-2 和图 10-3 分别为将 Timer2/3 配置成的两个独立 16 位定时器 Timer2 和 Timer3 的框图。Timer2/3 模块是 32 位定时器 (可配置为两个 16 位定时器),具有可选择的工作模式。 这些定时器为其他外设模块所使用,例如:

• 输入捕捉

• 输出比较 / 简单的 PWM对于定时器的工作模式,下面的各小节将详细说明其设置和控制寄存器以及相应的框图。32 位定时器有下列模式:

• 两个独立的 16 位定时器(Timer2 和 Timer3),支持所有 16 位工作模式(异步计数器模式除外)

• 一个 32 位定时器

• 一个 32 位同步计数器

此外,支持如下工作特性:

• ADC 事件触发信号

• 定时器门控操作

• 可选的预分频比设置

• 空闲和休眠模式下的定时器工作

• 在 32 位周期寄存器匹配时产生中断通过设定 16 位 T2CON 和 T3CON SFR 中的相应位来决定这些工作模式。对于 32 位定时器 / 计数器操作,Timer2 是 32 位定时器的低位字,而 Timer3 是高位字。

注: 对于 32 位定时器操作, T3CON 控制位将被忽略。 设置和控制只使用 T2CON 控制位 。对于 32 位定时器模块,使用的是Timer2 时钟和门控输入,但是,中断产生由 Timer3 中断标志位(T3IF)反映,且中断通过Timer3中断允许位(T3IE)来允许。16 位定时器模式: 在 16 位模式下, Timer2 和 Timer3可以配置为两个独立的 16 位定时器。 每个定时器均可设置为 16 位定时器模式或 16 位同步计数器模式。这两种工作模式的详细信息,请参见第 9.0 节 “Timer1 模块”。Timer2 和 Timer3 之间唯一的功能差异是,Timer2 提供了时钟预分频器输出同步。这对于高频外部时钟输入很有用。

32 位定时器模式: 在 32 位定时器模式下,定时器在每个指令周期递增,一直递增到与预先装入组合 32 位周期寄存器 PR3/PR2 中的值匹配,然后复位至 0,继续计数。对于 Timer2/Timer3 对的同步 32 位读操作,读低位字(TMR2 寄存器)将导致高位字被读取并锁存到一个 16 位保持寄存器 (称作 TMR3HLD)。对于同步 32 位写操作,必须首先写入保持寄存器(TMR3HLD)。如果后续操作是写 TMR2 寄存器的话,则 TMR3HLD 的内容将传送并锁存到 32 位定时器(TMR3)的 MSB 中。

32 位同步计数器模式; 在 32 位同步计数器模式下,定时器将在外部时钟信号的上升沿递增,外部时钟信号与内部时钟同步。 定时器计数,一直递增到与预先装入组合 32 位周期寄存器 PR3/PR2 中的值匹配,然后复位至0,继续计数。当定时器配置为同步计数器模式时,且 CPU 进入空闲模式的话,定时器将停止递增,除非 TSIDL 位(T2CON<13>) = 0。 如果 TSIDL = 1,定时器模块逻辑将在 CPU 空闲模式结束时继续递增 。

• 定时器门控操作

32 位定时器可以置为门控时间累加模式。 该模式使得当门控输入信号 (T2CK 引脚)为高电平时,内部 TCY能够递增相应的定时器。 要使能该模式,必须置 1 控制位 TGATE (T2CON<6>)。 在此模式下, Timer2 是发起时钟源。 对于 Timer3, TGATE 设定被忽略。 必须使能定时器 (TON = 1),且定时器时钟源设置为内部时钟源 (TCS = 0)。外部信号的下降沿终止计数操作,但不会复位定时器。要从零开始计数,用户必须复位定时器。

• ADC 事件触发信号

当 32 位定时器(TMR3/TMR2)与 32 位组合周期寄存器(PR3/PR2)匹配时,或当 16 位定时器 TMR3 和 16位周期寄存器 PR3 匹配时,Timer3 将生成 ADC 特殊事件触发信号。

• 定时器预分频器

定时器的输入时钟 (FOSC/4 或外部时钟),有 1:1、1:8、 1:64 或 1:256 的预分频比选择;通过控制位TCKPS<1:0> (T2CON<5:4> 和 T3CON<5:4>)来选择预分频比。 对于 32 定时器操作,发起时钟源是Timer2。在此模式下不能进行Timer3的预分频器操作。当发生以下情况中的任何一种时,预分频器计数器清零:

• 写 TMR2/TMR3 寄存器

• 对 T2CON/T3CON 寄存器进行写操作

• 器件复位,如 POR 和 BOR

但是,如果定时器被禁止 (TON = 0),由于预分频器的时钟停止了工作, Timer2 预分频器将不会被复位。当写 T2CON/T3CON 时, TMR2/TMR3 不会被清零。

• 休眠模式下的定时器操作

在 CPU 休眠模式期间,由于禁止了内部时钟,所以定时器不工作。

• 定时器中断

32 位定时器模块具有在周期匹配时,或者在外部门控信号下降沿产生中断的能力。 当 32 位定时器计数与相应的 32 位周期寄存器相匹配时,或者检测到外部“门控”信号的下降沿时, T3IF 位(IFS0<7>)将置 1,如果允许中断的话则将产生中断。在此模式下,T3IF 中断标志用作中断源。 T3IF 位必须在软件中清零。通过相应的定时器中断允许位 T3IE (IEC0<7>)来允许中断。

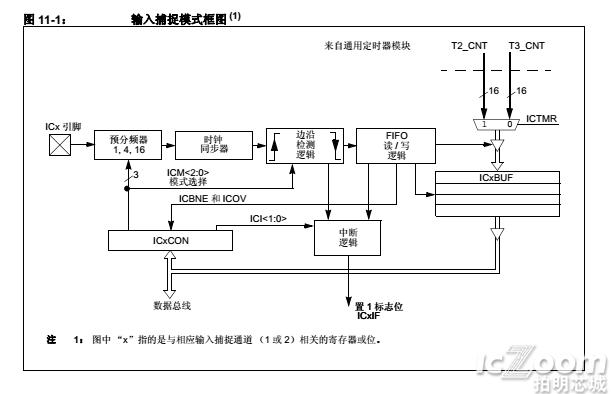

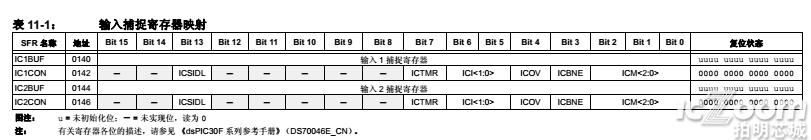

11.0 输入捕捉模块

注: 本数据手册总结了 dsPIC30F 系列器件的功能,但是不应把本手册当作无所不包的参考手册来使用。有关 CPU、外设、寄存器说明和一般器件功能的更多信息,请参阅《dsPIC30F系列参考手册》(DS70046E_CN)。本章对输入捕捉模块和相关的工作模式进行了介绍。此模块提供的工作特性可用于需要进行频率(周期)和脉冲测量的应用场合。图 11-1 给出了输入捕捉模块的框图。输入捕捉功能可用于以下模式:

• 频率 / 周期 / 脉冲测量

• 其他外部中断源输入捕捉模块的关键工作特性是:

• 简单捕捉事件模式

• Timer2 和 Timer3 模式选择

• 输入捕捉事件发生时产生中断通过在 IC1CON 和 IC2CON 寄存器中设置相应的位,选择上述工作模式。 dsPIC30F2011/2012/3012/3013 器件具有两个捕捉通道。

11.1简单捕捉事件模式dsPIC30F 产品系列中的简单捕捉事件有:

• 在每个下降沿进行捕捉

• 在每个上升沿进行捕捉

• 在每第 4 个上升沿进行捕捉

• 在每第 16 个上升沿进行捕捉

• 在每个上升沿和下降沿进行捕捉通过设置适当的位 ICM<2:0> (ICxCON<2:0>),选择上述简单输入捕捉模式。

11.1.1捕捉预分频器

有四种输入捕捉预分频器设置,它们由 ICM<2:0>(ICxCON<2:0>)位指定。每当捕捉通道关闭时,预分频器计数器将清零。另外,任何复位都将清零预分频器计数器。

• 捕捉缓冲器操作

每个捕捉通道都有一个关联的 FIFO 缓冲器,该缓冲器宽 16 位,深度为四字。有两个状态标志,提供 FIFO 缓冲器的状态:

• ICBNE——输入捕捉缓冲器非空

• ICOV——输入捕捉溢出

ICBNE 将在第一个输入捕捉事件发生时被置 1,并且一直保持置 1 状态,直到所有的捕捉事件都已从 FIFO 中读出。每次从 FIFO 中读出一个字,余下的字将在缓冲器中前进一个位置。当 FIFO 已满 (FIFO 中有四个捕捉事件)时,如果在读 FIFO 之前发生第五个捕捉事件,则将产生溢出,且 ICOV 位将被设置成逻辑 1。第五个捕捉事件将丢失,不会存入 FIFO。而且在从缓冲器读出全部四个事件之前不会再捕捉任何事件如果 FIFO 已空,且还没有收到新的捕捉事件,这时读 FIFO 将产生不确定的结果。

• TIMER2 和 TIMER3 选择模式

输入捕捉模块有最多 8 个输入捕捉通道。每个通道均可选择两个定时器 (Timer2 和 Timer3)之一作为时基。通过特殊功能寄存器位 ICTMR (ICxCON<7>),来对定时器资源进行选择。对于输入捕捉模块,Timer3 是默认的可用定时器资源。

• 霍尔传感器模式

当输入捕捉模块设置为在每个边沿 (上升沿和下降沿, ICM<2:0> = 001)进行捕捉时,输入捕捉逻辑将执行下列操作:

• 输入捕捉中断标志在每个边沿 (上升沿和下降沿)置 1。

• 由于每次捕捉都产生中断,捕捉时产生中断模式设置位 ICI<1:0> 被忽略。

• 在这个模式下,不产生捕捉溢出。

• 休眠和空闲模式下的输入捕捉工作

当器件在 CPU 空闲或休眠模式下时,输入捕捉事件将使器件唤醒,如果允许中断,还将产生中断。如果 ICM<2:0> = 111 且中断允许位置 1,那么当捕捉事件发生时,输入捕捉模块将使 CPU 从休眠或空闲模式中唤醒,这与使能的时钟无关。如果处理中断的条件已经得到满足的话,上述唤醒还将产生中断。唤醒特性可以用来增加额外的外部引脚中断。

• CPU 休眠模式下的输入捕捉

CPU 休眠模式允许输入捕捉模块以功能受到限制的方式工作。在 CPU 休眠模式下, ICI<1:0> 位不适用,输入捕捉模块只能用作外部中断源。当器件处于休眠模式下时,为了使用输入捕捉模块,必须把捕捉模块设置成仅在上升沿产生中断(ICM<2:0> = 111)。在此模式下, 4:1 或 16:1 的预分频比设置不适用。

• CPU 空闲模式下的输入捕捉

CPU 空闲模式允许输入捕捉模块以全功能的方式工作。在 CPU 空闲模式下,由 ICI<1:0> 位选择的中断模式是适用的,由控制位 ICM<2:0> 定义的 4:1 和 16:1 捕捉预分频比设置同样也适用。这个模式要求使能所选择的定时器。此外, ICSIDL 位必须置为逻辑 0。在 CPU 空闲模式下,如果输入捕捉模块定义为 ICM<2:0> = 111,则输入捕捉引脚仅用作外部中断引脚。

• 输入捕捉中断

输入捕捉通道具有根据选定的捕捉事件数来产生中断的能力。由控制位 ICI<1:0>

(ICxCON<6:5>)来设置选定的捕捉事件数。每个通道都有一个中断标志位(ICxIF)。各捕捉通道中断标志位于相应的 IFSx

寄存器中。通过相应捕捉通道中断允许位(ICxIE)来允许中断;捕捉通道中断允许位位于相应的 IEC 控制寄存器中。

责任编辑:Davia

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)