Cadence发布通过产品流片的第三代并行仿真平台Xcelium™

213

213

拍明

拍明

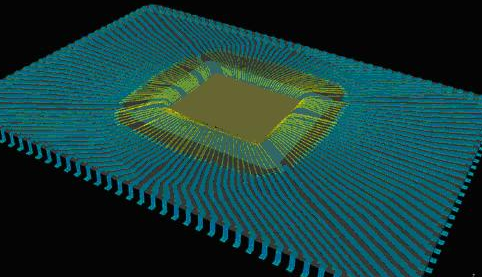

楷登电子(美国 Cadence 公司)今日发布业界首款已通过产品流片的第三代并行仿真平台Xcelium™ 。基于多核并行运算技术,Xcelium™ 可以显著缩短片上系统(SoC)面市时间。较Cadence上一代仿真平台,Xcelium™ 单核版本性能平均可提高2倍,多核版本性能平均可提高5倍以上。Cadence® Xcelium仿真平台已经在移动、图像、服务器、消费电子、物联网(IoT)和汽车等多个领域的早期用户中得到了成功应用,并通过产品流片验证。

“不论是ARM还是我们的合作伙伴,交付产品以达到客户预期的能力,不可避免的需要快速和严格的验证环节,”ARM公司技术服务产品部总经理Hobson Bullman说,“Xcelium并行仿真平台对于基于ARM的SoC设计,在门级仿真获得4倍的性能提升,在RTL仿真获得5倍的性能提升。基于这些结果,我们期待Xcelium可以帮助我们更快和更可靠的交付最复杂SOC,”

“针对智能汽车和工业物联网应用中复杂的28nm FD-SOI SoC和ASIC设计,快速和可扩展的仿真是满足严苛开发周期的关键!” 意法半导体公司CPU团队经理Francois Oswald说到,“我们使用Cadence Xcelium并行仿真平台,在串行模式DFT仿真中得到8倍的速度提升,所以数字和混合信号SoC验证团队选择Xcelium作为标准的仿真解决方案。”

Xcelium仿真平台具备以下优势,可以大幅加速系统开发:

· 多核仿真,优化运行时间,加快项目进度:第三代Xcelium仿真平台源于收购Rocketick公司带来的技术,是业内唯一正式发布的基于产品流片的并行仿真平台。利用Xcelium可显著缩短执行时间,在寄存器传输级(RTL)仿真可平均提速3倍,门级仿真可提高5倍,DFT仿真可提高 10倍,节约项目时间达数周至数月。

· 应用广泛:Xcelium仿真平台支持多种最新设计风格和IEEE标准,使工程师无需重新编码即可提升性能。

· 使用方便:Xcelium仿真平台的编译流程将设计与验证测试环境代码分配至最优引擎,并自动选取最优CPU内核数目,提高执行速度。

· 采用多项专利技术提高生产力(申请中):优化整个SoC验证时间的新技术包括:为达到快速验证收敛的SystemVerilog Testbench覆盖率和多核并行编译。

“在设计开发高质量新产品时,验证通常是最耗费成本和时间的环节,”Cadence公司高级副总裁兼数字签核事业部和系统验证事业部总经理Anirudh Devgan博士表示。“Xcelium仿真平台、JasperGold® Apps、Palladium® Z1企业级仿真平台和Protium™ S1 FPGA原型验证平台共同构成了市场上最强大的验证产品套件,帮助工程师加快设计创新的步伐。”

全新Xcelium仿真平台是Cadence验证套件家族的新成员,继承Cadence的创新传统,并全面符合Cadence系统设计实现(SDE)战略,该战略的宗旨是帮助系统和半导体设计公司有效的开发更完整、更具竞争力的终端产品。该验证套件(Cadence Verification Suite)包含最先进的核心引擎技术,采用多种验证架构技术及解决方案,帮助客户优化设计质量,提高生产力,满足不同应用和垂直领域的验证需求。

Cadence同时发布Protium S1 FPGA原型验证平台——Cadence验证产品家族的新成员,原型验证时间缩短最高达50%。

Cadence

铿腾电子科技有限公司(Cadence Design Systems, Inc; NASDAQ:CDNS)是一个专门从事电子设计自动化(EDA)的软件公司,由SDA Systems和ECAD两家公司于1988年兼并而成。是全球最大的电子设计技术(Electronic Design Technologies)、程序方案服务和设计服务供应商。其解决方案旨在提升和监控半导体、计算机系统、网络工程和电信设备、消费电子产品以及其它各类型电子产品的设计。产品涵盖了电子设计的整个流程,包括系统级设计,功能验证,IC综合及布局布线,模拟、混合信号及射频IC设计,全定制集成电路设计,IC物理验证,PCB设计和硬件仿真建模等。 其总部位于美国加州圣何塞(San Jose),在全球各地设有销售办事处、设计及研发中心。2016年,Cadence被《财富》杂志评为“全球年度最适宜工作的100家公司”。

主要产品

Cadence公司的电子设计自动化(Electronic Design Automation)产品涵盖了电子设计的整个流程,包括系统级设计,功能验证,IC综合及布局布线,模拟、混合信号及射频IC设计,全定制集成电路设计,IC物理验证,PCB设计和硬件仿真建模等。同时,Cadence公司还提供设计方法学服务,帮助客户优化其设计流程;提供设计外包服务,协助客户进入新的市场领域。自1991年以来,该公司已连续在国际EDA市场中销售业绩稳居第一。全球知名半导体与电子系统公司均将Cadence软件作为其全球设计的标准。Cadence公司其总部位于美国加州圣何塞(San Jose),在全球各地设有销售办事处、设计及研发中心,现拥有员工约4800名,2003年收入约11亿美元。

【相关新闻】Cadence发布验证运算平台

为了让半导体与系统制造厂商加快产品上市速度,益华电脑(Cadence Design Systems)发表Palladium XP II 验证运算平台,作为强化系统开发套装不可或缺的一环,大幅加速软硬体验证。

Palladium XP II 平台建立在屡获奖项肯定的 Palladium XP 仿真技术基础之上,提升验证效能达50%,并扩展容量达23亿逻辑闸。由于更低的功耗与更高的闸道密度,现在客户能够以更小的面积承载更大的资料量。Cadence益华电脑也扩大支援8种全新行动与消费性通讯协定,加速模拟。

有鉴于及早、快速且精准的软硬体验证需求不断地增高,Cadence以Palladium为核心,扩大系统开发套装的功能,新增包括:专利申请中的混合式技术,结合Cadence Virtual System Platform (虚拟系统平台)与Palladium XP系列,提高嵌入式OS验证速度达60倍,以及软硬体验证效能达10倍;

先进系统虚拟化环境的嵌入式测试程式,让使用者能够在投入试产之前验证周边驱动程式,加速晶片系统级的开发与验证。

GSEDA首席分析师Gary Smith表示:「2012年Transaction Based Acceleration最新版市场报告中显示,Cadence益华电脑蝉连市场领导厂商。全新升级的Palladium XP II平台硬体功能以及更先进的使用模式,让Cadence益华电脑能够克服使用者所面对、从系统到验证逐渐攀升的严苛挑战。」

NVIDIA工程协理Narendra Konda表示:「由于Cadence益华电脑Palladium虚拟系统平台混合式解决方案,我们在电路仿真(in-circuit emulation)时能够享受Palladium平台带来高达60倍的OS启动速度,并在OS上执行量产与测试软体时达10倍的效能提升,且能够与精准的硬体设计互动。这种新的使用模式大幅缩短了NVIDIA的系统软体验证时间,并确保更顺畅的晶片开发与验证。」

博通 (Broadcom)行动平台解决方案IC工程协理Vahid Ordoubadian表示:「我们运用Palladium XP II平台与其嵌入式测试程式(embedded test bench)的使用模式,发掘关键问题并在投入试产之前加以解决,以连接到SoC周边装置的模型作为整个可合成的嵌入式测试平台之一环。因此,我们能够更快速地验证新的SoC架构,而且能够以不到一天的时间来执行初始测试。」

Zenverge工程副总裁Kent Goodin表示:「我们提供量产级软体的能力搭配本公司SoC,就是我们达成产品上市目标的关键。Palladium XP II平台让我们的软体团队在IC光罩产出和原型制作之前,能够先开发量产的程式码。这就让Zenverge能够提早至少6个月的时间尽快配合客户行动,这是以前尚未采用Palladium XP II 平台的模拟解决方案进行协同开发时所办不到的。

责任编辑:Davia

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)