EUV技术的首款7+纳米芯片明年量产, 晶圆代工龙头台积电将成全球首家

524

524

拍明

拍明

原标题:EUV技术的首款7+纳米芯片明年量产,台积电将成全球首家

晶圆代工龙头台积电采用极紫外光(EUV)微影技术的首款7+纳米芯片已经完成设计定案,支援最多4层EUV光罩。

台积电同时也在加速5纳米制程推进,预计明年4月可开始进行风险试产,支援的EUV光罩层将上看14层,5纳米可望如期在2020年上半年进入量产。

相关人士认为,台积电在晶圆先进制程持续推进,推出可整合多种异质芯片的先进封装技术,最大的竞争对手韩国三星短期内恐难与之抗衡。

由此来看,苹果明后两年将推出的7+纳米A13及5纳米A14应用处理器,可能将继续由台积电拿下独家代工订单。

随着台积电7纳米持续提升产能且良率逐步改善,台积电首款采用EUV技术的7+纳米制程已完成研发并进入试产,与7纳米相较拥有更低功耗表现及更高集积密度。

EUV工艺的7nm+(代号N7+)工艺,晶体管密度再提升20%,功耗降低10%,不过性能没有变化。

第三季初顺利完成客户首款芯片的设计定案,预计年底前会有更多客户芯片完成设计定案,明年第二季后将可顺利进入量产,届时台积电将成为全球首家采用EUV技术量产的晶圆代工厂。

另外台积电新12英寸晶圆厂Fab 18,第一期工程希望抢在年底前完工,明年开始进入装机,第二期工程也已开始动工兴建。

关于台积电5纳米的研发进度,预计明年上半年可获得客户首款芯片的设计定案,明年4月可望进入风险试产。以进度来看,2020年上半年将进入量产阶段。

与初代7nm工艺相比,台积电的5nm工艺大概能再降低20%的能耗,晶体管密度再提高1.8倍,至于性能,预计性能提升15%,如果使用新设备的话可能会提升25%。

为了搭配先进制程微缩及异质芯片整合趋势,台积电除了整合10纳米逻辑芯片及DRAM的整合扇出层叠封装(InFO-PoP),以及整合12纳米系统单芯片及8层HBM2存储器的CoWoS封装等均进入量产,也推出了整合多颗单芯片的整合扇出暨基板封装(InFO-oS)、整合扇出存储器基板封装(InFO-MS)、整合扇出天线封装(InFO-AIP)等新技术,满足未来在人工智能及高效能运算、5G通讯等不同市场需求。

面对三星及格芯在22纳米全耗尽型绝缘层上覆硅(FD-SOI)制程上持续获得订单,台积电优化28纳米推出的22纳米超低功耗(ULP)制程已经进入试产阶段。

目前已有超过40个客户产品完成设计定案,明年将顺利进入量产,超低漏电(ULL)制程预期明年上半年获得客户芯片设计定案。

另外根据国际电子商情之前的报道,台积电已经公布了3nm制程工艺计划,台南园区的3nm晶圆工厂已经通过了环评初审,台积电计划投资6000亿新台币(约为194亿美元),2020年开始建厂,2021年完成设备安装,预计最快2022年底到2023年初投产,3nm厂完成后预计雇用员工达四千人。

不过3nm技术可以说已经接近半导体工艺的物理极限,而其目前也处于实验室阶段,台积电资深处长庄子寿坦言:“3nm制程技术难度高,是很大挑战。”

【相关信息】

EUV微影技术仍待克服重重障碍 2020年将用于关键步骤

极紫外光(EUV)微影技术持续取得重大进展。在日前于美国加州圣荷西举行的国际光电工程学会(SPIE)年度会议上,英特尔(Intel)与三星(Samsung)的专家表示,EUV正缓步进展中,但短时间内仍存在相当的障碍,这让任何一家公司都难以公开承诺何时才能开始使用这项技术。

另外,比利时微电子研究中心(Imec) 宣布使用EUV制造5nm制程技术的技巧,将有助于当今所的浸入式扫描仪。一般预期,EUV将在2020年左右被采用于几个关键步骤中,从而免于使当今193nm浸入式步进器所需的四次曝光。

KLA-Tencor首席技术专家Ben Tsai在SPIE先进微影(SPIE Advanced Lithography)大会的主题演讲中提到:「我认为沉入式微影技术将成为主力,而EUV则将用于选择层。」

三星指出,该公司积极推动在去年10月宣布的计划,将EUV用于7nm制程节点,但该公司尚未透露如何以及何时实现。英特尔则重申过去几年来的指导原则——「EUV十分适用于在7nm节点使用EUV极其理想,但得等到一切准备就绪后才会导入。」

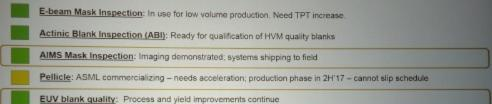

在现有的8个核心EUV计划中,有6项计划已经准备好或即将就绪。英特尔EUV计划负责人Britt Turkot指出,用于覆盖EUV晶圆的防尘薄膜仍在开发中,而用于检测EUV光罩的新工具也还验证中。

在8项核心的EUV计划中有6项已经准备就绪了(来源:Intel)

三星在年度会议中提到一款适用于7nm的EUV光罩检测工具,该公司自2012年起即已开始投入该技术的研发了。Turkot表示,缺少来自第三方的工具,并不能阻止EUV投入使用,但可能降低良率以及增加成本。

三星EUV计划负责人Seong-Sue Kim表示,去年底生产其首款EUV光罩,仅存在几处瑕疪,正适用于修复。「这是一项惊人的成就,在我开始工作时,如果少了EUV,这几乎不可能实现。」

带领英特尔整体光罩运作的Frank Abboud表示,英特尔自1992年以来致力于开发EUV光罩。英特尔的EUV工具他认为光罩并不会是EUV的把关项目,并展示英特尔在2014年为光罩设计的全新多光束工具。

英特尔在去年为晶圆厂出货其首款产品质量的EUV光罩。Turkot指出,英特尔的EUV光罩试产线已经开发出用于14、10和7nm等多种无缺陷的EUV网线了。

发展道路漫长曲折

英特尔和三星的半导体专家都认为,EUV光源功率已经朝向250W目标迈出了重大步伐。然而,EUV制造商ASML在去年年底报告的210W实验室展示以及现有最佳系统的130W之间仍存在差距。

EUV光源所需的液滴产生器和收集器寿命不断在延长中,而且也变得更可预测。 Turkot指出,另一家EUV光源供货商——日本Gigaphoton开发的产品展现了「令人鼓舞的结果」。

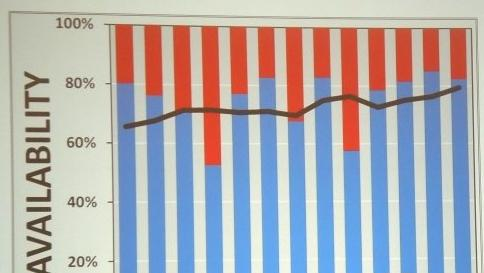

她说,整个EUV的运转时间正不断改善中,但还不够快。在去年年底时,最新的3350B系统可作业的时间超过了75%,比去年的结果提高了约5%。

英特尔认为,EUV系统的可用性持续提高,但进展速度还不够快(来源:Intel)

Turkot乐观表示,用于避免EUV晶圆缺陷的防尘薄膜正续改善、新的试产薄膜与量产薄膜也开发中。Kim则指出,新的防尘薄膜材料必须能够承受250W的生产扫描仪。

光阻剂材料即将达到7nm的性能目标,但还要更高的灵敏度。Kim说,这些化学品并不至于成为使用EUV的限制,但如果该技术进展仍无法克服线宽边缘的粗糙度和边缘布局等问题,未来将会限制EUV的发展。

「一旦工具启动以及运转,我们就会看到光罩出现越来越多的缺陷,」Turkot说,「我们可能不明白原因,但在多个工具中都会出现这样的问题,」包括最新的3350B。

好消息是业界目前正使用了14套EUV系统,其中6套是3350B,Turkot说。该设备持续扩展的数据组合有助于更快速地辨识图样,从而可能加快进展的脚步。

她将二十多年的EUV开发计划描述为一条漫长而曲折的道路。「目的地就在弯道附近…我们必须注意目前所在位置以及看清前方道路。」

Imec描述一种EUV途径,可用于创造5nm逻辑节点、42nm 金属-1层间距以及32nm M2。它象征着采用来自研究机构的EUV技术首次完整实现的制程节点,并将有助于开拓此技术。

Imec说,单次EUV阻挡步骤可以完成自对准四极图案化(SAQP)设计,同时还能仅使用浸入式步进机降低20%的成本。该公司并描述将EUV用于单一图案化的步骤,有助于削减了SAQP与三重阻障层。然而,这种替代技术可能带来成本与复杂度增加的问题。

编译:Susan Hong

(参考原文:EUV Progress, Hurdles Cited,by Rick Merritt)

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)