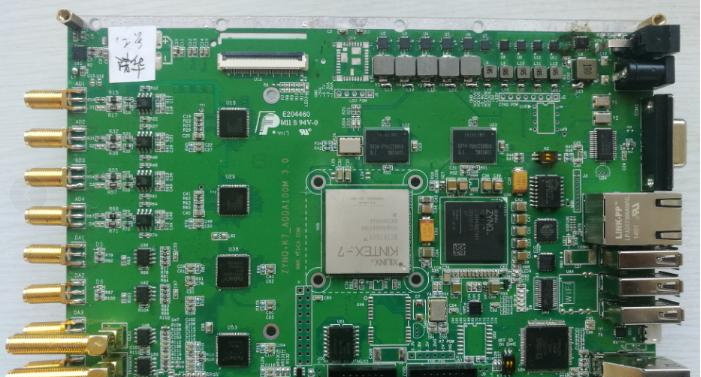

模块板卡: ZynQ FPGA(xc7z020)ARM嵌入式网络采集卡(交付形式:PCBA)

652

652

拍明

拍明

原标题:ZynQ FPGA_ARM嵌入式网络采集卡

应用领域:工业电子

方案类型:模块板卡

方案概述

应用领域:工业控制、医疗健康

应用场景:各类高精度、高可靠性的工业控制、健康医疗和智能楼宇数据采集应用

交付形式:PCBA

性能参数:

l FPGA+ARM架构+高速同步四路100MSPS AD采集+高速四路500MSPS DAC信号输出为一套系统。该系统可同时进行高速AD采集和高速DAC输出,arm为双核1G主频,FPGA为Xilinx xc7z020,DDR3内存1G

l 高速双路AD为14位,输入耦合DC,同步采样速率最高为100MSPS,3db带宽大于150M,信号输入范围正负1V或正负5V(焊接选择)

l 高速双路DAC为16位,更新速率为500MSPS

l 采集板网卡为千兆网口,采样速率可通过上位机dll库和arm下位机设置,可进行立即触发、软件触发、通道触发、外触发采集(上升沿触发、下降沿触发)

l 板卡带同步sma时钟接口,可多块板卡同步采集,通过网络交换机进行数据传输

l 整套板卡可工作在Win7-32位,Win7-64位,Windows-xp,Win8下使用,供电电压5V DC或12V DC,正常工作功率不大于6 W

l 上位机和arm下位机可实时获取各通道AD采集值和控制DAC输出值并获取输出值,用于数据分析

l 开放arm下位机qt应用源码和上位机dll动态库c++源码及网口通讯协议,提供arm下位机qt和上位机c++测试程序,测试板卡上述功能,并提供源码

l 板卡带VGA接口、USB接口,可外接鼠标操作下位机,可外接显示屏

l 多路模拟信号高速采集使用,可自主发生信号

方案图片:

【xc7z020】

Zynq-7000 SoC First Generation Architecture

The Zynq®-7000 family is based on the Xilinx SoC architecture. These products integrate a feature-rich dual-core or single-core ARM®

Cortex™-A9 based processing system (PS) and 28 nm Xilinx programmable logic (PL) in a single device. The ARM Cortex-A9 CPUs are

the heart of the PS and also include on-chip memory, external memory interfaces, and a rich set of peripheral connectivity interfaces.

Processing System (PS)

ARM Cortex-A9 Based

Application Processor Unit (APU)

• 2.5 DMIPS/MHz per CPU

• CPU frequency: Up to 1 GHz

• Coherent multiprocessor support

• ARMv7-A architecture

• TrustZone® security

• Thumb®-2 instruction set

• Jazelle® RCT execution Environment Architecture

• NEON™ media-processing engine

• Single and double precision Vector Floating Point Unit (VFPU)

• CoreSight™ and Program Trace Macrocell (PTM)

• Timer and Interrupts

• Three watchdog timers

• One global timer

• Two triple-timer counters

Caches

• 32 KB Level 1 4-way set-associative instruction and data caches

(independent for each CPU)

• 512 KB 8-way set-associative Level 2 cache

(shared between the CPUs)

• Byte-parity support

On-Chip Memory

• On-chip boot ROM

• 256 KB on-chip RAM (OCM)

• Byte-parity support

External Memory Interfaces

• Multiprotocol dynamic memory controller

• 16-bit or 32-bit interfaces to DDR3, DDR3L, DDR2, or LPDDR2

memories

• ECC support in 16-bit mode

• 1GB of address space using single rank of 8-, 16-, or 32-bit-wide

memories

• Static memory interfaces

• 8-bit SRAM data bus with up to 64 MB support

• Parallel NOR flash support

• ONFI1.0 NAND flash support (1-bit ECC)

• 1-bit SPI, 2-bit SPI, 4-bit SPI (quad-SPI), or two quad-SPI (8-bit)

serial NOR flash

8-Channel DMA Controller

• Memory-to-memory, memory-to-peripheral, peripheral-to-memory,

and scatter-gather transaction support

I/O Peripherals and Interfaces

• Two 10/100/1000 tri-speed Ethernet MAC peripherals with

IEEE Std 802.3 and IEEE Std 1588 revision 2.0 support

• Scatter-gather DMA capability

• Recognition of 1588 rev. 2 PTP frames

• GMII, RGMII, and SGMII interfaces

• Two USB 2.0 OTG peripherals, each supporting up to 12 Endpoints

• USB 2.0 compliant device IP core

• Supports on-the-go, high-speed, full-speed, and low-speed

modes

• Intel EHCI compliant USB host

• 8-bit ULPI external PHY interface

• Two full CAN 2.0B compliant CAN bus interfaces

• CAN 2.0-A and CAN 2.0-B and ISO 118981-1 standard

compliant

• External PHY interface

• Two SD/SDIO 2.0/MMC3.31 compliant controllers

• Two full-duplex SPI ports with three peripheral chip selects

• Two high-speed UARTs (up to 1 Mb/s)

• Two master and slave I2C interfaces

• GPIO with four 32-bit banks, of which up to 54 bits can be used with

the PS I/O (one bank of 32b and one bank of 22b) and up to 64 bits

(up to two banks of 32b) connected to the Programmable Logic

• Up to 54 flexible multiplexed I/O (MIO) for peripheral pin assignments

Interconnect

• High-bandwidth connectivity within PS and between PS and PL

• ARM AMBA® AXI based

• QoS support on critical masters for latency and bandwidth control

技术文档:

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)