基于STM32F103RBT6的语音导览系统的设计方案

496

496

拍明

拍明

景点语音导览主要有以下几种方式:一种是通过全球定位系统(GPS)的用户终端接收工作卫星的导航信息,从而解算出车辆的经纬度信息,进而计算出实时坐标,将其与景点坐标相比较,当车辆驶入景点一定距离范围内时,不用人工干预,系统自动播报景点语音信息;另一种是对车轮轴的转角脉冲进行计数,将计数值和预置值对比,即可确定播放时刻,达到准确播放景点语音信息的目的;第三种方案是利用无线射频识别技术,在每一个景点范围内设置一个具有唯一ID的射频发射器,采用间歇工作方式发射信号,当旅游列车即将到达景点时,车载系统接收到射频发射器信号并解码出景点的ID号,由系统控制自动播放对应编号的景点语音信息。由于景点自然环境的复杂性,第一种方式难以满足系统要求;第二种方式简单可靠,但旅游轨道车辆运行方向存在不确定性,其相对位置往返变化,系统的自动化程度较低且复杂度较高。

本文首先介绍了系统总体结构,然后,给出了系统各主要功能模块的具体设计,并重点研究了基于ARM3核的STM32F103RBT6芯片与语音芯片ISD4004之间的SPI通信控制和实现技术,给出了系统设计实现结果。

最后,给出了有一定工程应用参考价值的结论。

1系统总体设计

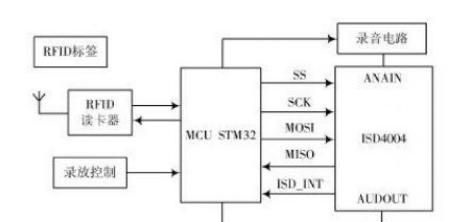

本系统结构原理设计如图1所示。本设计利用旅游列车轨道固定的特点,在轨道沿线景点预先安装固定ID的RFID,综合考虑到作用距离、数据通信方式、可靠性、使用寿命和维护成本,选用产品433 MHz有源标签GAO C124061.其存储ID字长32 b.由于在野外自然环境中,出现碰撞的可能性极低,所以,RFID阅读器只需要正确可靠地获得RFID的ID值,与固定景点所对应,用以触发中断,开始播放该景点的语音信息。

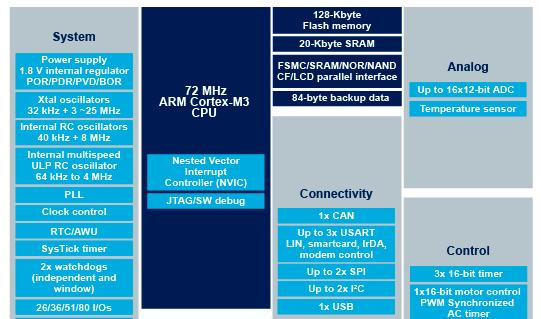

图1中,MCU采用STM32F103RBT6芯片,该芯片是基于ARM Cortex-M3内核高性能、低成本、低功耗的嵌入式应用MCU.本设计选择这款的原因是看重其性价比:128 KB FLASH、20 KB SRAM、2个SPI、3个串口、1个USB、1个CAN、2个12位的ADC、RTC、51个可用I/O脚等一系列性能特征,能完全满足本系统性能要求。总结下来,STM32具有价格低、功能强、使用简单、开发方便等几个很有利的优势。ISD4004为语音录放存储芯片,根据外部控制和外围电路辅助,可随机对其进行语音录入和语音播放。系统MCU通过RFID阅读器获得旅游列车沿途RFID的固定ID,根据ID号所对应的预设语音数据存储位置的起始地址信息,通过对ISD4004内置的SPI端口进行控制,实现景点语音选段自动播放。

图1系统结构原理框图

2主要模块电路设计

2.1 ISD4004控制电路设计

ISD4004系列语音芯片工作电压为+3 V,单片录放时间8~16 min,音质好。芯片采用CMOS技术,内含时钟、抗混叠滤波器、平滑滤波器、音频放大器、自动静噪及高密度多电平非易失性存储器阵列。芯片设计是基于所有操作必须由微控制器控制,操作命令可通过串行通信接口(SPI)送入。芯片采用多电平直接模拟量存储技术,每个采样值直接存储在片内非易失性存储器中,因此能够非常真实、自然地再现语音、音乐、音调和效果声,避免了一般固体录音电路因量化和压缩造成的量化噪声和金属声。芯片ISD4004内部结构和主要引脚功能如图2所示。

图2 ISD4004内部结构

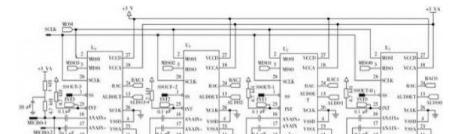

ISD4004内部器件控制单元设置非常便于其与STM32序列芯片的SPI进行通信设置。增设STM32多个I/O口来作为对应语音芯片的片选端,即可实现多片ISD4004扩展。STM32与多片ISD4004的接口电路如图3所示。

图3多片ISD4004与STM32的连接

STM32和ISD4004通过SPI模块进行通信,两者MOSI、MISO脚对应相互连接,实现STM32和ISD4004之间数据串行传输(MSB位在前)。通信总是由主设备STM32发起。STM32通过MOSI脚把数据发送给ISD4004,ISD4004通过MISO引脚回传数据给STM32.

全双工通信的数据输出和数据输入是用同一个时钟信号同步的;时钟信号由主设备STM32通过SCK脚提供。

扩展为多片语音芯片后,语音信息的存储空间大大增加,便于扩充景点的语音信息量。

2.2语音录放控制电路设计

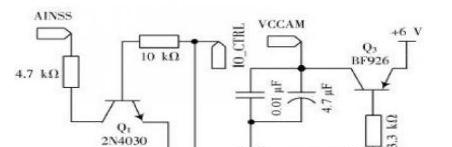

语音录放控制电路如图4所示。通过MCU的I/O控制端来控制串联调整管Q3或开关管Q1,实现系统放音或者录音。I/O端输出高电平时实现录音,输出低电平时实现放音。

图4语音录放控制电路

2.3 RFID读卡器接口电路

RFID读卡器模块使用了Philips的高集成ISO14443A读卡芯片MFRC500.RFID读卡器是一个相对独立的功能模块,其输出可通过中断状态信息和串口与外部连接。因此,系统利用STM32F103RBT6的SPI2接口实现与RFID读卡器接口之间的数据通信,从而自动获得景点位置信息,以控制选择对应景点导览语音的播放。读卡器中断状态直接与STM32F103的PD口I/O引脚连接;SPI2接口电路形式同图3类似。

3主要功能软件设计

3.1软件初始化

3.1.1外设时钟的使能

本设计中涉及的外设时钟可以通过APB2外设时钟使能寄存器来使能。当外设时钟没有启用时,软件无法读出外设寄存器的值,返回的数值始终为0.设计中用到的PA口、PB口、PD口的时钟分别通过APB2ENR寄存器的第2、3、5位来设置,SPI1的时钟通过APB2ENR的第12位来设置。

3.1.2 I/O口的初始化

本设计涉及的I/O口包括:用于控制片选扩展的PA.3、PB.0口,需设置成开端输出模式;用于实现按键控制的PA.15(录音键)、PA.0(强制停止键)等需设置为上拉输入模式;用于实现SPI通信的PA.5、PA.6、PA.7口,它们分别对应SPI1的SCK、MISO、MOSI口,应由软件设置这三个口为复用I/O口即第二功能;用于检测放音结束时语音芯片INT端低电平输出的PA.8和PD.2设置为上拉输入模式。

3.1.3外部中断的初始化

外部中断初始化中主要完成的工作是设置I/O口与中断线的对应关系、开启与该I/O口对应的线上中断/事件以及设置中断的触发条件、配置中断分组并使能中断。本设计中,将强制停止键连接到的PA.0口对应的中断触发条件设置为上升沿触发,对应的中断优先级最高;其余按键连接的I/O口对应的中断触发条件都设置为下降沿触发。把所有的中断都分配到第二组,把所有按键的次优先级设置成一样,而抢占优先级不同。其中,几个放音键连接的I/O口对应的中断共用一个中断服务程序,也就是多个中断线上的中断共用一个中断服务函数,在该中断服务程序里先对进入中断的信号进行区分(通过中断输入I/O口上的电平判断),再分别处理。

3.1.4 SPI模块的初始化

本设计中,通过对CR1寄存器的设置,将SPI1模块设置成全双工模式、软件NSS管理、主机模式、8 b MSB数据格式,并且把SPI1的波特率设置成了最低(281.25 kHz,为系统时钟的256分频),其中最重要的是SPI模块输出串行同步时钟极性和相位的配置,SPI主模块和与之通信的外设备时钟相位和极性应该一致。最后,发送0xff启动传输。

根据ISD4004不同相位下的SPI总线传输时序和SPI操作时序关系,要想实现STM32和ISD4004之间的SPI通信,须将其控制位CPHA和CPOL都设置为1.

3.2 SPI控制功能软件实现

3.2.1 SPI1读写字节函数

在读数据时,接收到的数据被存放在一个内部的接收缓冲器中;在写数据时,在被发送之前,数据将首先被存放在一个内部的发送缓冲器中。对SPI_DR寄存器的读操作,将返回接收缓冲器的内容;写入SPI_DR寄存器的数据将被写入发送缓冲器中。

SPI_SR是16位状态寄存器,它的最低位为RXNE,该位为0则接收缓冲为空,为1则接收缓冲非空;SPI_SR的次低位为TXE,该位为0说明发送缓冲非空,为1则发送缓冲为空。不断地查询发送/接收缓冲区是否为空,进而实现数据的有序发送和接收。

3.2.2发送指令函数

首先,语音芯片ISD4004有如下操作规则:

(1)串行外设接口,SPI协议设定微控制器的SPI移位寄存器在SCLK下降沿动作,在时钟上升沿锁存MOSI引脚数据,在下降沿将数据送至MISO引脚。

(2)上电顺序,器件延时TPUD(8 kHz采样时,约为25 ms)后才能开始操作。因此,用户发完上电指令后,必须等待TPUD,才能发出下一条操作指令。

例如,

从00处放音,应遵循如下时序:

①发POWER UP命令;

②等待TPUD(上电延时);

③发地址值为00的SET PLAY命令;

④发PLAY命令。

器件会从00地址开始放音,当出现EOM时,立即中断,停止放音。

如果从00处录音,则按以下时序:

①发POWER UP指令;

②等待TPUD(上电延时);

③发POWER UP命令;

④等待2倍TPUD;

⑤发地址值为00的SET REC命令;

⑥发REC命令。

器件便从00地址开始录音,一直到出现OVF(存储器末尾)时,录音停止。

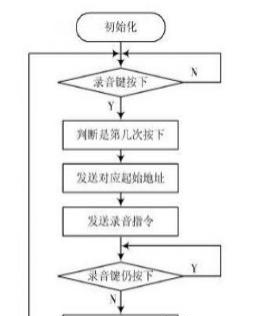

3.3中断服务程序

录音中断服务程序流程如图5所示。它实现的功能是在一次长按录音键时,将一个景点的语音信息录入ISD4004中以预先设定的起始地址存储空间中,松开录音键后,本景点语音内容录音停止。每个景点的导览语音存储的位置,以其起始地址为标示。起始地址的安排根据每段语音的长度决定。每个景点语音录音时需保持录音按键锁下不松开,直至本段景点语音录音结束。

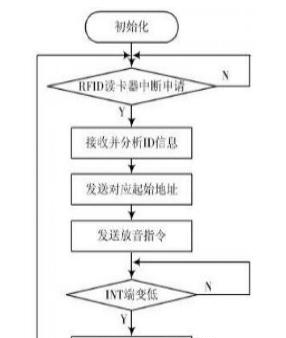

景点语音播放中断服务程序流程如图6所示。系统在获得RFID读卡器的中断申请之后,根据读卡器接口协议,MCU经SPI2接口接收到读卡器传来的数据信息,分析出RFID所含的ID信息内容,并根据ID所对应的景点位置,即原设置的景点语音首地址,将此首地址发送到ISD4004芯片组,并发送放音命令,即可实现对应景点事先录制好的导览语音自动播放。开始播放语音信息期间,ISD4004的I-N-T-端连接到了STM32的I/O口上,不断查询它的状态。当这段语音信息放完时,语音芯片ISD4004的I-N-T-端会置低,由此发送停止播放指令,则实现播音结束,并等待下一个RFID信息的输入和读卡器中断申请。

图5录音流程

图6放音流程图

4系统调试测试结果

4.1录放音模块调试

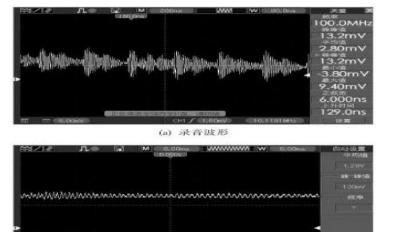

对于录音模块功能的测试,采用如下的办法:对着麦克风进行放音,用示波器观察语音芯片的输入引脚是否有信号。在语音芯片输入引脚检测到信号,如图7(a)所示。

在成功录入语音后,发送放音指令在语音芯片输出引脚得到如图7(b)所示波形。

图7录放音调试试验波形

4.2 SPI模块调试

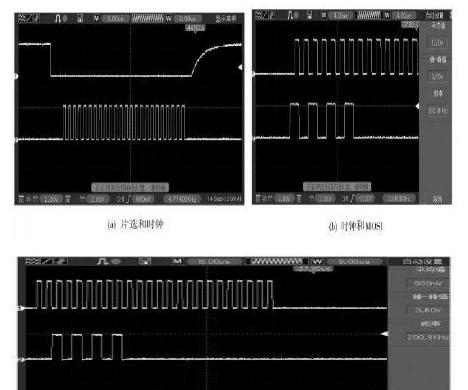

在录音电路正确后,发送放音指令,在芯片对应SPI1模块功能的引脚端,可以在示波器上看到正确的时序,如图8所示。

图8(a)是片选和时钟信号输出;图8(b)和(c)分别是不停地发送0×55,在STM32 SPI1的数据发送端MOSI和数据接收端MISO得到的波形,与实际相符。

片选mosi

图8 SPI1接口调试试验时序波形

5结论

本文提出的系统结构简单、实用可靠,特别适用于山区自然景点的有轨旅游列车项目等,因而该系统具有很好的实用价值。可用于复杂环境下的语音导览系统实现结构,详细介绍了系统主要功能模块的实现技术和调试实验结果。

STM32F103RB

Mainstream Performance line, ARM Cortex-M3 MCU with 128 Kbytes Flash, 72 MHz CPU, motor control, USB and CAN

The STM32F103xx medium-density performance line family incorporates the high-performance ARM®Cortex®-M3 32-bit RISC core operating at a 72 MHz frequency, high-speed embedded memories (Flash memory up to 128 Kbytes and SRAM up to 20 Kbytes), and an extensive range of enhanced I/Os and peripherals connected to two APB buses. All devices offer two 12-bit ADCs, three general purpose 16-bit timers plus one PWM timer, as well as standard and advanced communication interfaces: up to two I2Cs and SPIs, three USARTs, an USB and a CAN.

The devices operate from a 2.0 to 3.6 V power supply. They are available in both the –40 to +85 °C temperature range and the –40 to +105 °C extended temperature range. A comprehensive set of power-saving mode allows the design of low-power applications.

The STM32F103xx medium-density performance line family includes devices in six different package types: from 36 pins to 100 pins. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family.

These features make the STM32F103xx medium-density performance line microcontroller family suitable for a wide range of applications such as motor drives, application control, medical and handheld equipment, PC and gaming peripherals, GPS platforms, industrial applications, PLCs, inverters, printers, scanners, alarm systems, video intercoms, and HVACs.

Key Features

ARM® 32-bit Cortex® -M3 CPU Core

72 MHz maximum frequency,1.25 DMIPS/MHz (Dhrystone 2.1) performance at 0 wait state memory access

Single-cycle multiplication and hardware division

Memories

64 or 128 Kbytes of Flash memory

20 Kbytes of SRAM

Clock, reset and supply management

2.0 to 3.6 V application supply and I/Os

POR, PDR, and programmable voltage detector (PVD)

4-to-16 MHz crystal oscillator

Internal 8 MHz factory-trimmed RC

Internal 40 kHz RC

PLL for CPU clock

32 kHz oscillator for RTC with calibration

Low-power

Sleep, Stop and Standby modes

VBAT supply for RTC and backup registers

2 x 12-bit, 1 μs A/D converters (up to 16 channels)

Conversion range: 0 to 3.6 V

Dual-sample and hold capability

Temperature sensor

DMA

7-channel DMA controller

Peripherals supported: timers, ADC, SPIs, I2 Cs and USARTs

Up to 80 fast I/O ports

26/37/51/80 I/Os, all mappable on 16 external interrupt vectors and almost all 5 V-tolerant

Debug mode

Serial wire debug (SWD) & JTAG interfaces

7 timers

Three 16-bit timers, each with up to 4 IC/OC/PWM or pulse counter and quadrature (incremental) encoder input

16-bit, motor control PWM timer with dead-time generation and emergency stop

2 watchdog timers (Independent and Window)

SysTick timer 24-bit downcounter

Up to 9 communication interfaces

Up to 2 x I2 C interfaces (SMBus/PMBus)

Up to 3 USARTs (ISO 7816 interface, LIN, IrDA capability, modem control)

Up to 2 SPIs (18 Mbit/s)

CAN interface (2.0B Active)

USB 2.0 full-speed interface

CRC calculation unit, 96-bit unique ID

Packages are ECOPACK®

电路原理图

责任编辑:Davia

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)