基于Si5384/Si5386E/OG1409CAN主控器件的分布式基站设备时钟解决件方案

332

332

拍明

拍明

概述

分布式基站系统将传统基站的基带单元(BBU)和射频拉远单元(RRU)分离,相对于传统一体化基站,分布式基站配置灵活、建设方便、维护更便捷。时钟系统是分布式基站的重要组成部分,通常分布式基站对时钟链路的要求主要在两个方面,即对GPS/BITs的接收时钟进行本地同步处理和对数据链路恢复的时钟进行消抖处理。

优势

· Silicon Labs网络时钟发生器/同步器Si5384是一款结合了业界最小封装(8*8 LGA)和最低功耗(最大1.6W)的网络同步时钟发生器,具有极其灵活的频率合成特性和业界最低的抖动性能指标(RMS jitter 为150fs),能有效提高去抖时钟的相噪特性,降低通信误码率,提高系统通信稳定性。

【Si5384】

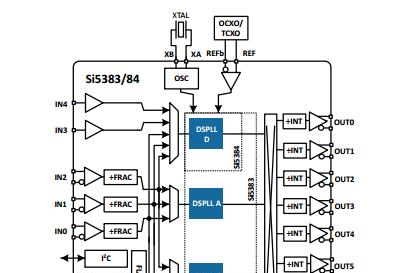

Si5383/84 Rev D Data Sheet

Network Synchronizer Clocks Supporting 1 PPS to 750 MHz Inputs

The Si5383/84 combines the industry’s smallest footprint and lowest power network synchronizer clock with unmatched frequency synthesis flexibility and ultra-low jitter. The Si5383/84 is ideally suited for wireless backhaul, IP radio, small and macro cell wireless communications systems, and data center switches requiring both traditional and packet based network synchronization.

The three independent DSPLLs are individually configurable as a SyncE PLL, IEEE 1588 DCO, or a general-purpose PLL for processor/FPGA clocking. The Si5383/84 can also be used in legacy SETS systems needing Stratum 3/3E compliance. In addition, locking to a 1 PPS input frequency is available on DSPLL D. The DCO mode provides precise timing adjustment to 1 part per trillion (ppt). The unique design of the Si5383/84 allows the device to accept a TCXO/OCXO reference with a wide frequency range, and the reference clock jitter does not degrade the output performance. The Si5383/84 is configurable via a serial interface and programming the Si5383/84 is easy with ClockBuilder Pro software. Factory pre-programmed devices are also available.

Applications

• Synchronous Ethernet (SyncE) ITU-T G.8262 EEC Option 1 & 2

• Telecom Grand Master Clock (T-GM) as defined by ITU-T G.8273.1

• Telecom Boundary Clock and Slave Clock (T-BC, T-TSC) as defined by ITU-T G.8273.2

• IEEE 1588 (PTP) slave clock synchronization

• Stratum 3/3E, G.812, G.813, GR-1244, GR-253 network synchronization

• 1 Hz/1 PPS Clock Multiplier

KEY FEATURES

• One or three independent DSPLLs in a single monolithic IC supporting flexible SyncE/IEEE 1588 and SETS architectures

• Input frequency range:

• External crystal: 25-54 MHz

• REF clock: 5-250 MHz

• Diff clock: 8 kHz - 750 MHz

• LVCMOS clock: 1 PPS, 8 kHz - 250 MHz

• Output frequency range:

• Differential: 1 PPS, 100 Hz - 718.5 MHz

• LVCMOS: 1 PPS, 100 Hz - 250 MHz

• Ultra-low jitter of less than 150 fs

· Silicon Labs无线专用时钟发生器Si5386E时钟是一款结合了业界最小封装(9*9 LGA)和集成低相噪DSPLL的时钟发生器,以紧凑的单芯片设计取代了分立时钟IC、VCXO和环路滤波器件。相对于依赖多个PLL和分立振荡器的解决方案,简化了原理图、PCB设计,提供了更优良的可靠性。

【Si5386E】

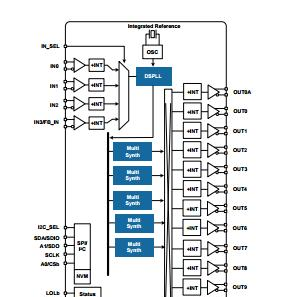

Si5386 Rev E Data Sheet

12-channel, Any Frequency, Wireless Jitter Attenuating Clock

The Si5386 is a high performance, integer and fractional clock generator for wireless applications which demand the highest level of integration and phase noise performance. Based on Silicon Laboratories’ 4th generation DSPLL technology, the Si5386 combines frequency synthesis and jitter attenuation in a highly integrated digital solution that eliminates the need for external VCXO and loop filter components. A fixedfrequency crystal that provides frequency stability for free-run and holdover modes is integrated within the package saving valuable PCB space. This all-digital solution provides superior performance that is highly immune to external board disturbances such as power supply noise.

Modern C-RAN remote radio heads and fixed wireless systems require a diverse set of clocks such as ADC/DAC, RF LOs, eCPRI/CPRI, and Ethernet clocks. The Si5386 architecture is designed to deliver high-performance JESD204B DCLK and SYSREF clock pairs and flexible any-rate clocks for non-LTE clocks such as Ethernet and system reference clocks all from a single IC.

Applications:

• Cloud Radio Access Network RRHs

• Small cells

• Fixed wireless

• Wireless base stations

• Active antenna systems

• Distributed antenna systems

KEY FEATURES

• Flexible timing in a single IC

• Generates any combination of output frequencies from any input frequency

• Input frequency range:

• Differential: 7.68 MHz to 750 MHz

• LVCMOS: 7.68 MHz to 250 MHz

• Output frequency range (Integer):

• Differential: up to 3 GHz

• Output frequency range (fractional):

• Differential: up to 735 MHz

• LVCMOS: up to 250 MHz

• Ultra-low jitter:

• 80 fs typ (12 kHz–20 MHz)

· Epson的恒温晶振OG1409CAN,提供超高精度、稳定度的时钟,频率温度稳定度为0.05 ppm(-40℃~85℃),能够快速预热和准确锁定,能够在3分钟内达到0.1 ppm稳定度的时钟输出,可以快速提供稳定的、高精度参考源时钟。

【OG1409CAN】

恒温晶体振荡器OCXO(Oven Controlled Crystal Oscillator)是利用恒温槽使晶体振荡器或石英晶体振子的温度保持恒定,将由周围温度变化引起的振荡器输出频率变化量削减到最小的晶体振荡器。爱普生恒温晶振批量型号主要是10MHz,15.36MHz和20MHz三个常用频点,其他频率完全可以定制,具体请于爱普生官方网站推荐代理商-南京南山在线客服咨询。

OG2525CCNHCBDDJ

标准频率:10MHz

外部尺寸:25.4 × 25.4 × 12.7mm(Pin类型)

频率温度特性:50×10-9@-20℃~+70℃

电源电压:5V

特性:非常快速预热和准确稳定;SC切晶体单元。

OG2522CANHCADDG

标准频率:15.36MHz

外部尺寸:25.4 × 22.0 × 12.1mm(薄型贴片SMD)

频率温度特性:50×10-9 @-20℃~+70℃

电源电压:5V

特性:非常快速预热和准确稳定;SC切晶体单元。

OG1409CAN系列

标准频率:20MHz

外部尺寸:14.6 ×9.7 × 6.5 mm(薄型贴片SMD)

频率温度特性:50×10-9 @-40℃~+85℃

电源电压:3.3V

特性:SMD贴片,更薄;IPC/JEDEC J-STD-020D回流焊可用。

相关元件供应

型号:SI5386E-E-GM 品牌:SILICON LABS

【基站同步时钟】

基站同步时钟是一种高性能的时间频率参考接收机,能够为电信、移动通信基站、小灵通基站、GSM网络优化等系统提供高精度的时间和频率同步信号。

基站同步时钟采用了低相噪锁相环技术和大规模集成电路设计,内置高稳定度恒温晶振OCXO和高品质、高精度授时型GPS接收机,采用先进的GPS频率测控技术,对晶体振荡器的输出频率进行精密测量与调节,使其输出频率精确同步在GPS系统上,提供高精度的时间频率基准信号,能够输出满足ITU-T G.811要求1级基准时钟源,可以使用在数字交换机、SONET和SDH传输系统上。同时,HJ5432A还可以为任何级别的定时信号发生器(TSG)提供1级时钟同步信号,可以向外提供追踪与UTC时间的2.048Mb/s(E1)和2.048MHz输出信号。

基站同步时钟的Opt-EIO选项能够提供再定时功能,可接收E1信号并利用本身精准的时间参考信号对其进行重新解码,输出波形符合ITU-T G.703码型为HDB3的 E1信号,当设备自身降质或者断电时,将启动直通模式将接收到的E1信号输出。

基站同步时钟输出的1pps信号是GPS驯服晶振输出频率信号经过10,000,000次分频后得到的,相位与载波信号严格一致,且不受GPS秒脉冲短时间随机跳变带来的影响,相当于UTC时间基准的“复现”。这种特性特别适合于通信基站等对时间频率要求严格的系统。

基站同步时钟具有泰福特科技独创的智能学习算法,在GPS驯服晶振的过程中能够不断“学习”晶振的漂移等特性,并将这些参数存入板载EEPROM存储器中。当GPS出现异常或不可用时,HJ5432A能够自动切换到保持模式(Hold-over mode),利用高效的智能保持算法,依靠内置高稳晶振继续提供高可靠性的时间和频率信号输出,在短时间内仍保持有较高的精度。当设备断电重新开机后,设备可以利用原来已经存储的历史数据,使时钟在较短的时间内达到较高的准确度。

基站同步时钟5432A前面板具有电源、GPS、1pps、锁定等指示灯,并通过LCD液晶屏实时显示当前时间和GPS工作状态等信息。HJ5432A同时支持通过串口输出GPS等状态信息,易于实现系统的集成化管理和监控。

责任编辑:Davia

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)