基于STM32F100R8T6+SN65HVD06D+LPC2214FBD144的DP/PA Link设计方案

5

5

拍明

拍明

原标题:基于STM32的DP/PA Link设计

引言

DP/PALINK模块实现上位冗余PROFIBUS-DP主站系统与下位非冗余PROFIBUS-PA设备系统之间的网络转换。对于较高级别的系统面向自动化设备),DP/PALINK是DP从站,只占用较高级别DP主站系统的一个节点;DP/PALINK是PA主站,PA总线系统中的现场设备不占用上级DP总线系统的节点地址。

1功能描述

本模块通过64针欧式连接器与底座连接,可配置为模块单机或冗余使用。通过设置底座上的终端电阻,在下级DP总线网络中可作中间节点,也可作末端节点。

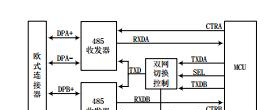

1.1硬件功能框图

DP/PALINK模块的硬件电路功能框图如图1所示。可用于实现上位冗余PROFIBUS-DP主站系统与下位非冗余PROFIBUS-PA设备系统之间的网络转换。

图1中的MCU选用ST公司的STM32F100R8T6,它采用基于ARM最新架构的32位Cortex-M3内核,结合了执行Thumb-2指令的32位哈佛微体系结构和系统外设,系统时钟最高24MHz,芯片性能达1.25DMIPS/MHz,内嵌64KB的

FLASH和8KB的SRAM,片上资源丰富,功能上完全可以满足系统设计需求。

ARM选用LPC2214FBD144,表贴,TQFP封装,144引脚,Philips。集成有16KB的片内RAM及256KB的片内FLASH。

模块的DP数据转发、长发故障的判断、读取监控电源的状态、通道灯的状态显示等基本由硬件逻辑完成。硬件可编程逻辑器件选用Xilinx公司性价比相对较高的spartan-6系列的xc6slx9器件,它具有5720个LUT(查找表),9152个L(C逻辑单元),11440个FK触发器),32个BlockRAM(18KbEach),最大用户引脚102个,144-pinTQFP封装。

1.2时钟设计

本模块的时钟要求是低成本、能够正常起振、不停振、温漂小。图2给出了本模块的时钟树。下面以MCU晶体为例来进行说明。

MCU选择石英晶体。本次设计中主要从HC-49XA-G20SSA-8.000MHz和HC-49XA-C20SSA-12MHz二者中选择一个,二者都满足性能要求,在MCU内部容易倍频得到48MHz时钟频率,但是HC-49XA-G20SSA-8.000MHz为工业级,工作温度范围宽,所以选型HC-49XA-G20SSA-8.000MHz。晶体参数表如表1所列。

1.3电路元器件的选择

本电路中采用22pF±5%陶瓷电容,电路中的振荡器的增益余量用于表明振荡器是否起振。外部电阻Rext可选择904Ω,这样,就仍然能够保证正常起振。

针对选型的晶体HC-49XA-G20SSA-8.000MHz,可通过计算得到对UART波特率的影响。MCU的时钟树从引脚输入8MHz,经PLL倍频到24MHz作为系统时钟。因为UART波特率越高时钟的误差对波特率的影响越大。MCU支持的最大波特率为1.5MHz。假定在波特率为1.5MHz时,计数器的时钟为系统时钟24MHz,UART的预分频数值为16。因为每发送一个字节,都会重新检测起始位,因此,波特率的误差只存在于一个字节的发送周期内。这样可以计算发送一个字节(10位)产生的累积信号偏移+检测间隔误差的偏移量为:±(132PPM*11*16+1/32)=±5.45%。由于UART接收都是在信号中间位置捕捉信号,所以,时钟的误差对UART的性能不会产生影响。

关于时钟误差对MCU定时器的影响。因为MCU的定时器主要用于超时定时,所以对时钟的精度要求不高,即时钟误差对定时器的影响可以忽略不计。

1.4DP总线设计

DP总线通信芯片采用TI公司的SN65HVD06D,其通信速率可达10Mb/s;最小差动输出电压为2.5V(54Q负载);ESD保护超过16kV;同时带有上电、掉电保护功能,支持热插拔。图3所示是485电路的功能框图。485电路包括6部分,MCU、POWER、双网切换控制、两个485收发器、欧式连接器。

Power部分主要为MCU、双网切换控制器和485收发器提供电源。MCU是485电路的控制器,主要发送串行数据、接收串行数据、诊断485电路故障、切换网络和切断故障等功能。表2所列是双网切换控制器的真值表。

模块的DP双网采用双UART来实现。发送数据时,MCU通过CTRA、CTRB信号分别控制两路485收发器的发送使能。发送数据时,MCU通过SEL控制双网控制器选择MCU的TXDA或TXDB与TXD相连,这样UARTA或者

UARTB会向两个485收发器同时发送数据。发送侧双网选择的真值表如表2所示。RXDA和RXDB为接收端口,它接入MCU的UARTA和UARTB。这样双网的数据同时进入两个UART,由MCU内部诊断及切换逻辑选择其中一个UART的数据进行处理。

485收发器是完成485差分信号到串行通信的转换,由485芯片、外围上下拉电路和防护电路组成。485收发器的差分信号通过欧式连接器连接到RS485总线上,进行通信。

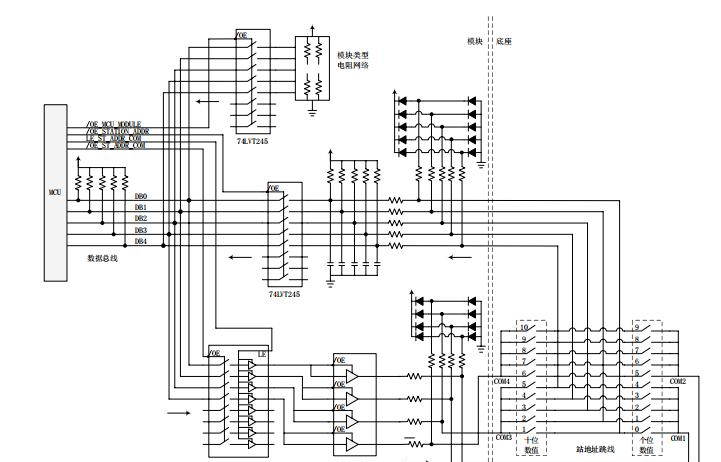

2读取站地址、CPU类型和模块类型设计

模块读取位于模块上的开关电路及底座上的跳线来获得站地址。站地址开关电路如图4所示。

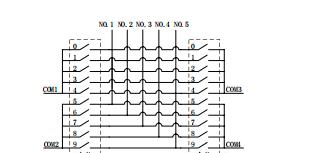

模块的站地址需要两列排针,每列上有一对针插入短路器,可将I。模块站地址设置为10~109号。一列排针表示站地址十位上的数字1~10,另一列排针表示站地址个位上的数字0~9。图5所示是站地址原理矩阵图。

图5中,COM1〜COM2组成十位数行,NO.1〜NO.5组成列,共可以构成10种状态,COM3~COM4组成个位数行,NO.1〜NO.5组成列也可以构成10种状态,所以可以表示

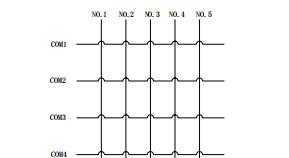

100种地址。图6所示是本系统的站地址逻辑图。

读取站地址时,首先在MCU初始化时,将/OE_MCU_MOUDE,/OE_STATION_ADDR、/OE_ST_ADDR_COM信号初始化为高电平,将LE_ST_ADDR_COM信号初始化为低电平。

读取站地址个位0~4,假设图6中,短路器把4号地址短路,MCU弓|脚/OE_ST_ADDR_COM发出低电平信号,即片选74LVC573芯片。数据总线[DB0:DB4]输出0x1E。然后MCU通过引脚LE_ST_ADDR_COM发出高电平,锁存数据总线DB[0:4]数据,0x1E。由于三态门74LVTH125每一路片选和数据端连接在一起,当输入为低电平时,才输出低电平;当输入为高电平时,输出为三态。这样74LVTH125输出端COM1为低电平,COM2、COM3和COM4为三态。这样通过底座上的跳线可以读取个位0~4范围内的站地址。然后MCU发出高电平的/OE_ST_ADDR_COM信号,和低电平的/OE_STATION_ADDR信号,片选读站地址74LVT245芯片。由于短路器把4号地址短路,COM1能把低电平信号通过跳线传送到数据线DB0上。由于其他地址为未有短路器,保持为上拉的高电平。这样MCU数据总线上的数据位0x0F。

MCU通过读取数据总线DB[0:4]获取个位0~4范围内的站地址,然后MCU发出高电平的/OE_STATION_ADDR信号,完成读取。

读取站地址个位5~9,读取过程与读取个位0~4范围的站地址相似。

读取站地址十位1~5和读取站地址十位6~10,读取过程与读取个位0~4范围的站地址相似。

当跳线个位或十位同时存在多余一个短路器时,MCU将认为存在故障,无法读取站地址。当跳线个位和十位上都不存在短路器时,MCU将认为存在故障,无法读取站地址。

由于在站地址电路的74器件需要提高热插拔等级,所以选用LVT逻辑器件,支持二级热插拔。由于74LVC573抗静电和热插拔防护等级不高,不支持三态,所以在74LVC573后附加一个支持二级热插拔等级的74LVTH125,并在输出电路上增加嵌位二极管,防护静电。74LVT245和防护电路能够抗静电和支持热插拔。

3冗余电路的设计

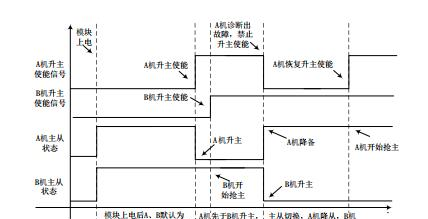

PA模块支持切换式冗余方式,模块自行完成切换并告知主控I/O自身的主从状态。互锁机制是保证只有一个主机的关键逻辑,主从机互锁电路如下图7所示。图8所示是主从机互锁时序图。

经过主从切换后,B机最终将变为主机,其工作原理如下:未启动状态,上电之后,双机的本板升主使能信号均为逻辑0状态,因此经过与非门之后,双机均处于逻辑1状态(备机状态),双机的本机状态输出同时通过上拉电阻保持在高电平状态。

双机启动后,先启动的模块(A或B自由竞争)通过自诊断发现本机正常,置本机升主使能信号为1,本机随即将主从状态输出为0。后启动的模块发现自身自诊断正常,也置本机升主使能信号为1,但是与非门的输入信号-对板主从信号已率先输出为0,导致本机主从状态输出被锁定,因此本机主从状态输出始终为1。

主机通过自诊断发现本机有故障,置本机升主使能信号为0进行主动降从,从机升主。

主从机进行切换后,当前从机通过自诊断发现本机无卡件致命故障,恢复置本机升主使能信号为1,但是与非门的输入信号-对板主从信号已被置为0,导致本机主从状态输出被锁定,因此本机主从状态输出始终为1。通过这种方式实现了A和B两者只能有一个主状态,可以同时为从状态,即实现了主从机互锁机制。

4结语

本次设计通过使用MCU、ARM和FPGA芯片的配合工作,能为上位冗余PROFIBUS-DP主站系统与下位非冗余PROFIBUS-PA设备系统之间的网络转换提供一个安全可靠的转换方案。

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)