ADI ADSP-BF592 Blackfin处理器开发评估方案

78

78

拍明

拍明

原标题:ADI ADSP-BF592 Blackfin处理器开发评估方案

ADI 公司的ADSP-BF592是集成了ADI/Intel微信号架构(MSA)的高达400MHz Blackfin处理器, 功耗低至51mW,包括了两个16位MAC信号处理引擎,两个40位ALU,四个8位视频ALU以及40位移位器,正交RISC类微处理器指令集和单指令多数据(SIMD)多媒体功能,具有先进的调试,跟踪和性能监测,主要用于工业,医疗,视频,音频和通用市场.本文介绍了ADSP-BF592主要特性, 方框图, Blackfin处理器核框图以及ADSP-BF592 EZ-KIT Lite评估板主要特性,框图,电路图和材料清单.

The ADSP-BF592 processor is a member of the Blackfin® family of products, incorporating the Analog Devices/Intel Micro Signal Architecture (MSA). Blackfin processors combine a dual-MAC state-of-the-art signal processing engine, the advantages of a clean, orthogonal RISC-like microprocessor instruction set, and single-instruction, multiple-data (SIMD) multimedia capabilities into a single instruction-set architecture.

The ADSP-BF592 processor is completely code compatible with other Blackfin processors. The ADSP-BF592 processor offers performance up to 400 MHz and reduced static power consumption.

ADSP-BF592主要特性:

Up to 400MHz high performance Blackfin processor

Two 16-bit MACs, two 40-bit ALUs, four 8-bit video ALUs, 40-bit shifter

RISC-like register and instruction model for ease of programming and compiler-friendly support

Advanced debug, trace, and performance monitoring

Accepts a wide range of supply voltages for internal and I/O operations,

Off-chip voltage regulator interface

64-lead (9 mm × 9 mm) LFCSP package

MEMORY

68K bytes of core-accessible memory

64K byte L1 instruction ROM

Flexible booting options from internal L1 ROM and SPI memory or from host devices including SPI, PPI, and UART

Memory management unit providing memory protection

PERIPHERALS

Four 32-bit timers/counters, three with PWM support

2 dual-channel, full-duplex synchronous serial ports (SPORT), supporting eight stereo I2S channels

2 serial peripheral interface (SPI) compatible ports

1 UART with IrDA support

Parallel peripheral interface (PPI), supporting ITU-R 656 video data formats

2-wire interface (TWI) controller

9 peripheral DMAs

2 memory-to-memory DMA channels

Event handler with 28 interrupt inputs

32 general-purpose I/Os (GPIOs), with programmable hysteresis

Debug/JTAG interface

On-chip PLL capable of frequency multiplication

图1.ADSP-BF592方框图

图2.ADSP-BF592 Blackfin处理器核框图

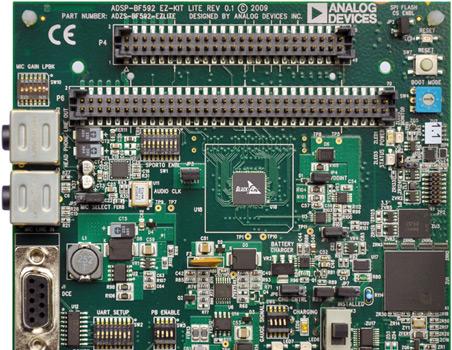

ADSP-BF592 EZ-KIT Lite评估板

The ADSP-BF592 EZ-KIT Lite® provides developers with a cost-effective method for initial evaluation of the ADSP-BF592 processor via a USB-based, PC-hosted tool set. With this EZ-KIT Lite, users can learn more about the Analog Devices (ADI) ADSP-BF592 hardware and software development, and quickly prototype a wide range of applications.

The EZ-KIT Lite includes an ADSP-BF592 Blackfin Processor desktop evaluation board along with an evaluation suite of the VisualDSP++® development and debugging environment, including the C/C++ compiler, assembler, and linker. The evaluation suite of VisualDSP++ is designed to be used with the EZ-KIT Lite only.

The EZ-KIT Lite also comes with a standalone debug agent board that is removable to allow a user to plug-in an external emulator.

ADSP-BF592 EZ-KIT Lite评估板主要特性:

Analog Devices ADSP-BF592 Blackfin processor

Programmable VDDINT core power: AD5258 TWI digital potentiometer and ADP1715 low dropout linear regulator

SPI flash memory: Numonyx M25P16 – 16 Mb

Audio codec: Analog Devices SSM2603 stereo, 24-bit analog-to-digital and digital-to-analog converters, Highly efficient headphone amplifier, Stereo line input and monaural microphone input

Universal asynchronous receiver/transmitter (UART): ADM3202 RS-232 line driver/receiver, DB9 female connector

LEDs: Eight LEDs: one board reset (red), three general-purpose (amber), one power (green), one battery good indicator (green), one battery low indicator (amber) and one battery charging indicator (amber)

Push buttons: Four push buttons: one reset, two programmable flags, and one wake-up with debounce logic

Expansion interface II: Next generation of the expansion interface design, provides access to most of the processor signals

JTAG ICE 14-pin header

图3.ADSP-BF592 EZ-KIT Lite评估板外形图

图4.ADSP-BF592 EZ-KIT Lite评估板框图

图5.ADSP-BF592 EZ-KIT Lite评估板电路图(1)

图6.ADSP-BF592 EZ-KIT Lite评估板电路图(2)

图7.ADSP-BF592 EZ-KIT Lite评估板电路图(3)

图8.ADSP-BF592 EZ-KIT Lite评估板电路图(4)

图9.ADSP-BF592 EZ-KIT Lite评估板电路图(5)

图10.ADSP-BF592 EZ-KIT Lite评估板电路图(6)

ADSP-BF592 EZ-KIT Lite评估板材料清单:

责任编辑:HanFeng

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)