LMK05318网络同步器时钟功能介绍

58

58

拍明

拍明

原标题:LMK05318网络同步器时钟功能介绍

在通信或者工业应用中,同步时钟非常重要,它确保了信号的完整性和一致性。可以说,时钟同步技术是现代通信中不可缺少的一个重要环节,选择好的同步时钟至关重要。

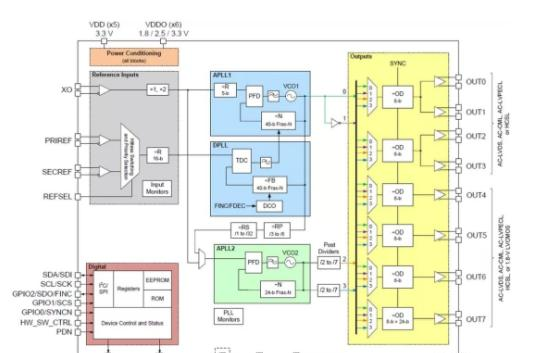

Texas Instruments LMK05318网络同步器时钟(带BAW)提供抖动消除、时钟生成、先进的时钟监控和卓越的无中断切换性能。这些特性设计用于满足通信基础设施和工业应用的严格计时要求。该器件具有超低抖动和高电源噪声抑制(PSNR)性能,可降低高速串行链路中的误码率(BER)。该器件可使用TI专有的体声波(BAW)VCO技术生成具有50fs RMS抖动的输出时钟,且不受XO和参考输入的抖动和频率影响。

DPLL支持抖动和漂移衰减的可编程环路带宽,而两个APLL则支持分频率转换,从而可以实现灵活的时钟生成。DPLL上支持的同步选项包括无中断切换、数字保持以及频率步进分辨率小于0.001ppb的DCO模式(可实现精确的时钟转向(IEEE 1588 PTP从运动))。DPLL可以锁相至1PPS(每秒脉冲)基准输入,并在一个输出上支持可选的零延迟模式,以实现具有可编程偏移的确定性输入至输出相位对齐。先进的基准输入监控块可确保稳健的时钟故障检测,并在发生基准缺失(LOR)时帮助将输出时钟干扰降至最低。

特点

一个数字锁相环(DPLL),具有如下特性

无中断切换:±50ps相位瞬态

具有快速锁定功能的可编程环路带宽

使用低成本TCXO/OCXO实现符合标准的同步和保持模式

两个具备业界领先抖动性能的模拟锁相环(APLL)

312.5MHz时具有50fs RMS抖动(APLL1)

155.52MHz时具有125fs RMS抖动(APLL2)

两个基准时钟输入

基于优先级的输入选择

在缺失参考时实现数字保持

具有可编程驱动器的八个时钟输出

多达六个不同输出频率

AC-LVDS、AC-CML、AC-LVPECL、HCSL和1.8V LVCMOS输出格式

加电后自定义时钟的EEPROM/ROM

灵活的配置选项

输入和输出为1Hz(1PPS)至800MHz

XO/TCXO/OCXO输入:10MHz至100MHz

DCO模式:0.001ppb/步长,可进行精确的时钟转向(IEEE 1588 PTP从运动)

先进的时钟监控和状态

I2C或SPI接口

PSNR

–86dBc(3.3V电源噪声为50mVpp)

电源

3.3V电源,提供1.8V、2.5V或3.3V输出

工业温度范围

−40°C至+85°C

应用

SyncE(G.8262)、SONET/SDH(Stratum 3/3E、G.813、GR-1244、GR-253)、IEEE 1588 PTP从器件时钟或光传输网络(G.709)

400G线卡、以太网交换机和路由器用交换卡

无线基站(BTS)、无线回程

功能框图

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)