基于全耗尽平面晶体管技术的NovaThor平台设计

12

12

拍明

拍明

原标题:基于全耗尽平面晶体管技术的NovaThor平台设计

随着智能手机功能近不断升级演化,消费者的期望值日益攀升。速度更快的多核高主频CPU处理器、令人震撼的3D图形、全高清多媒体和高速宽带现已成为高端手机的标配。同时,消费者还期望手机纤薄轻盈,电池续航能力至少与以前的手机持平。对于手机厂商和设计人员来说,消费者的期望意味着移动芯片需具备优异的性能,同时兼具低成本和低功耗。全耗尽平面晶体管技术 (FD-SOI:Fully Depleted Silicon on Insulator),是满足这些需求的解决方案。

在2012年移动通信世界大会上(Mobile World Congress),意法。爱立信执行官Didier Lamouche证实我们的下一代NovaThor平台,即NovaThorL8540的后续产品,将采用28nm FD-SOI制造工艺。

FD-SOI技术目前已经可供芯片开发使用,该技术将会使28nm工艺制程的芯片产品在性能和功耗方面有显着的提升。因为工艺复杂程度相对较低,FD-SOI解决了制程升级、泄漏电流和可变性等问题,能够将CMOS制程节点进一步降至28nm或28nm以下。

像FinFET技术一样,FD-SOI初是为20nm节点及以下开发设计的,能够突破传统体效应CMOS制程升级的限制因素,例如,高泄漏电流和终端设备多样性的难题;但是,又与FinFET技术不同,FD-SOI保留了传统体效应CMOS工艺的平面结构复杂度相对较低的优点,这可加快工艺开发和量产速度,降低现有设计的迁移难度。意法爱立信、意法半导体、Leti 和Soitec的技术合作让我们能够在28nm技术节点发挥FD-SOI的优势:先进性能、具有竞争力的处理速度/泄漏电流比和优化能效。

在宽电压范围内性能

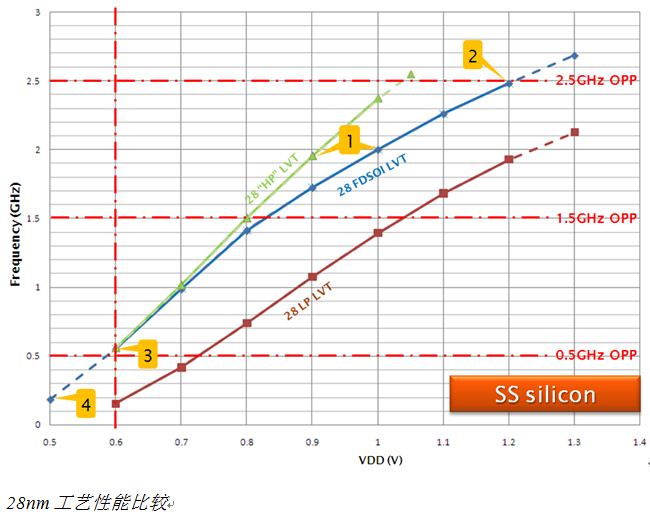

下图比较了在慢工艺角(SS)和环境温度恶劣时ARM Cortex-A9 CPU内核的一个特定关键通道能够达到的频率-Vdd电源电压曲线。

每条曲线代表一个特定的28nm制程:

.28HP-LVT是用于移动设备的高性能体效应CMOS工艺,瞄准高性能移动设备CPU,具有处理速度快和栅极氧化层薄的特点,因此,从可靠性看, Vdd 过驱动能力有限(~1.0V)。

.28LP-LVT 是一种低功耗的体效应CMOS 工艺,过去用于低功耗移动应用,LP 基于栅氧化层更厚的晶体管,支持更高的过驱动电压(高达1.3V)。

.28FDSOI-LVT是意法半导体开发的28nm FD-SOI工艺,栅极结构与28LP相似,也支持1.3V过驱动电压。

在这三种工艺中,只考虑低压阈值(LVT),因为处在这样的电压下时处理性能。

1.首先观察到的是,在标称电压(HP=0.9V,LP=1.0V,FD-SOI=1.0V)时,FD-SOI的峰值性能与HP工艺相似;在Vdd电压相同时,性能比LP高35%.

2.此外,随着Vdd 电压升高,FD-SOI的性能进一步提高,而 HP 工艺无法承受更高的电压,因此,前者的综合峰值性能高于后者。

3.在工作电压过低时,如Vdd=0.6V, LP将无法运行或性能很低;FD-SOI与HP工艺相当甚至高于HP工艺,但是前者的泄漏电流和动态功耗要比后者低很多,我将在后面的内容中给予说明。

4.相比体效应CMOS工艺,FD-SOI的工艺可变性低,在适合CPU处理非密集型任务的频率(200MHz-300MHz)时,能够支持更低的工作电压(0.5V),例如,硬件加速音、视频播放。

因此,在宽Vdd电压范围(0.5V 至 1.3V)内,FD-SOI的综合性能高于移动处理器专用的体效应CMOS工艺,这些性能优势可用于提高峰值性能,或者在保证性能不变的前提下降低Vdd工作电压,从而降低动态功耗。

我们探讨了FD-SOI工艺在性能-电压比方面的技术优势,接下来,我们将分析另外两大优势:具有竞争力的处理速度/泄漏电流比和优化能效。

具有竞争力的处理速度/泄漏电流比

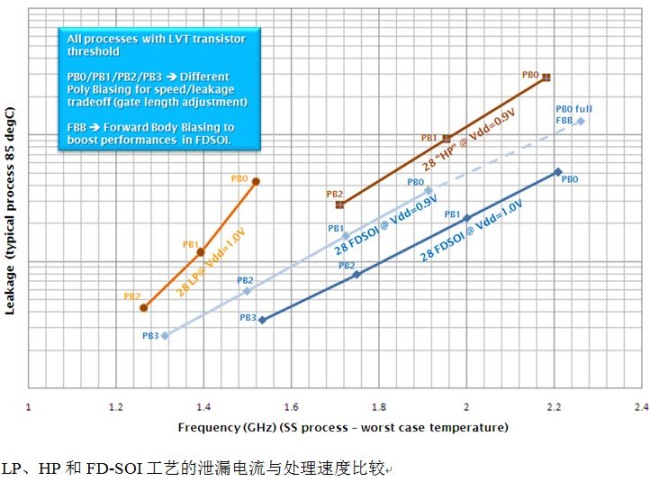

FD-SOI工艺不仅带来前文所述的性能优势,还具有同级产品的泄漏电流,下图示是前文图示的ARM Cortex-A9 关键通道在85°C时典型泄漏电流与频率之比。以系统的方法分析,当泄漏电流相同时,FD-SOI在标称电压(1.0V)时的运行频率高于标称电压(1.0V)时的LP工艺或标称电压(0.9V)时的HP工艺。

浅蓝色曲线代表Vdd=0.9V条件下的FD-SOI 泄漏电流/速度曲线,这意味着FD-SOI可让我们降低标称 Vdd 电压(对动态功耗影响巨大的参数),同时保持与LP和HP工艺相同的或更高的性能。然后,如蓝色延长虚线所示,施加在LVT FD-SOI晶体管上的正向体偏压(*) 使其能够达到HP可达到的性能,而在施加偏压后,多晶硅晶体管的泄漏电流增幅与LP工艺相同。

该泄漏电流/速度比优势是28nm FD-SOI工艺独有优势,真正地融LP 和 HP两大工艺的优点于一身。

体偏压是在CMOS晶体管的体效应部分施加可变电压,以提高泄漏电流为代价换取更快运行速度(正向体偏压),或者以牺牲性能为代价换取更低的泄漏电流(反向体偏压)。虽然体效应CMOS具有这项功能,但是,因为埋沟氧化层将晶体管沟道与硅体效应部分(背栅效应)隔离,体偏压的效果在FD-SOI技术上更加出色。

优化能效

对高端移动应用来说,良好处理性能兼出色的泄漏电流还不够,在移动设备日常使用过程中降低不同工作模式的总功耗才是化电池续航能力的关键。

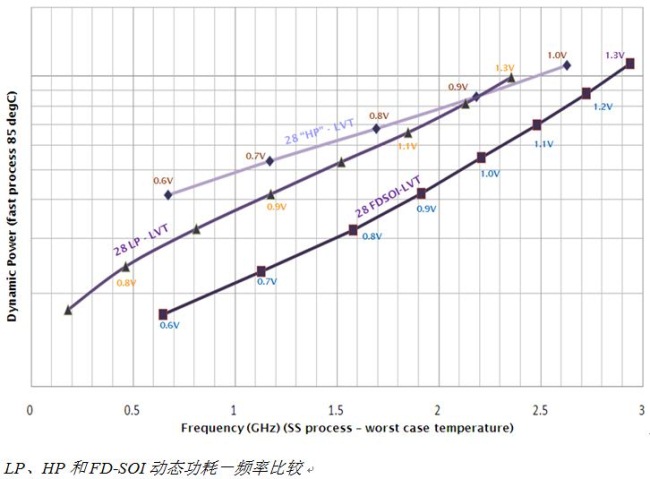

下图描述了三种不同的 28nm 工艺的动态功耗特性,并给出了动态功耗-频率特性曲线。

从图中不难看出,在给定频率时,FD-SOI的总功耗总是比其它两项技术低很多,即便达到目标频率所需的电源电压略高于28nm HP.这主要因为FD-SOI技术的总功耗中泄漏电流较低。在整个电源电压范围和对应的性能范围内均是如此,这充分证明,FD-SOI是能够给移动设备带来能效的解决方案。

从上文可以看出,28nm FD-SOI在对于移动计算设备极其重要的关键参数方面优于现有的体效应工艺,具有高性能且低功耗的优点。

责任编辑:

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)